(54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ КРАТНОСТИ 0,5

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник питания | 1980 |

|

SU900376A1 |

| СЧЕТНЫЙ ТРИГГЕР НА МДН-ТРАНЗИСТОРАХ | 1973 |

|

SU369717A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| Многоканальный коммутатор | 1984 |

|

SU1220124A1 |

| Динамический Д-триггер с третьим состоянием по выходу | 1990 |

|

SU1774472A1 |

| Делитель частоты с переменным коэффициентом деления | 1980 |

|

SU1075413A1 |

1

Изобретение относится к импульсной технике и может быть использовано в устройствах, где необходимо делен 1е частоты следования импульсов на число, кратное 0,5.

Известен делитель частоты на 1,5, содержащий два триггера памяти, два коммутационных триггера и два элемента И-НЕ 1.

Недостатком известного устройства является его сложность.

Известен также более универсальный делитель частоты с дробным коэффициентом деления, в котором коэффициенты деления могут принимать значения К N-0,5, где N 2, 3, 4, ..., содержащий делитель частоты с целым коэффициентом деления, выход которого подключен к выходной щине и к С-входу триггера, инверсный выход которого подключен к D-входу этого же триггера и к одному входу первого элемента 2И-НЕ, второй вход которого подключен ко входной шине, а выход подключен к одному входу второго элемента 2И-НЕ, второй вход которого подключен к выходу третьего элемента 2И-НЕ, первый вход которого подключен к прямому выходу триггера, а второй вход подключен к выходу инвертора, вход которого подключен ко входной шине устройства.

причем выход второго элемента 2И-НЕ подключен ко входу делителя частоты с целым коэффициентом деления 2.

Недостатком известного устройства является содержание значительного количестJ ва компонентов, что снижает надежность, быстродействие и экономичность работы.

Цель изобретения - повышение быстродействия, надежности и экономичности делителя частоты, а также обеспечение неискаженной передачи логических уровней на10 пряжения.

Цель достигается тем, что в делитель частоты с дробным коэффициентом деления кратности 0,5, содержащий делитель частоты с целым коэффициентом деления, выход которого подключен к выходной шине и к С-вхо15ду триггера, инверсный выход которого подключен к его D-входу, а также инвертор, вход которого подключен ко входной шине, введены первый МДП транзистор п-типа, сток которого подключен к выходу инверто2Q ра, а затвор - к прямому выходу триггера, и второй МДП транзистор п-типа, сток которого подключен ко входной шине, а затвор - к инверсному выходу триггера, истоки обоих МДП транзисторов подключены ко

входу делителя частоты с целым коэффициентом деления, а также параллельно первому и второму МДП транзисторам п-типа подключены соответственно первый и второй МДП транзисторы р-типа, причем затвор первого МДП транзистора р-типа подключен к инверсному выходу триггера, а затвор второго МДП транзистора р-типа - к прямому выходу триггера.

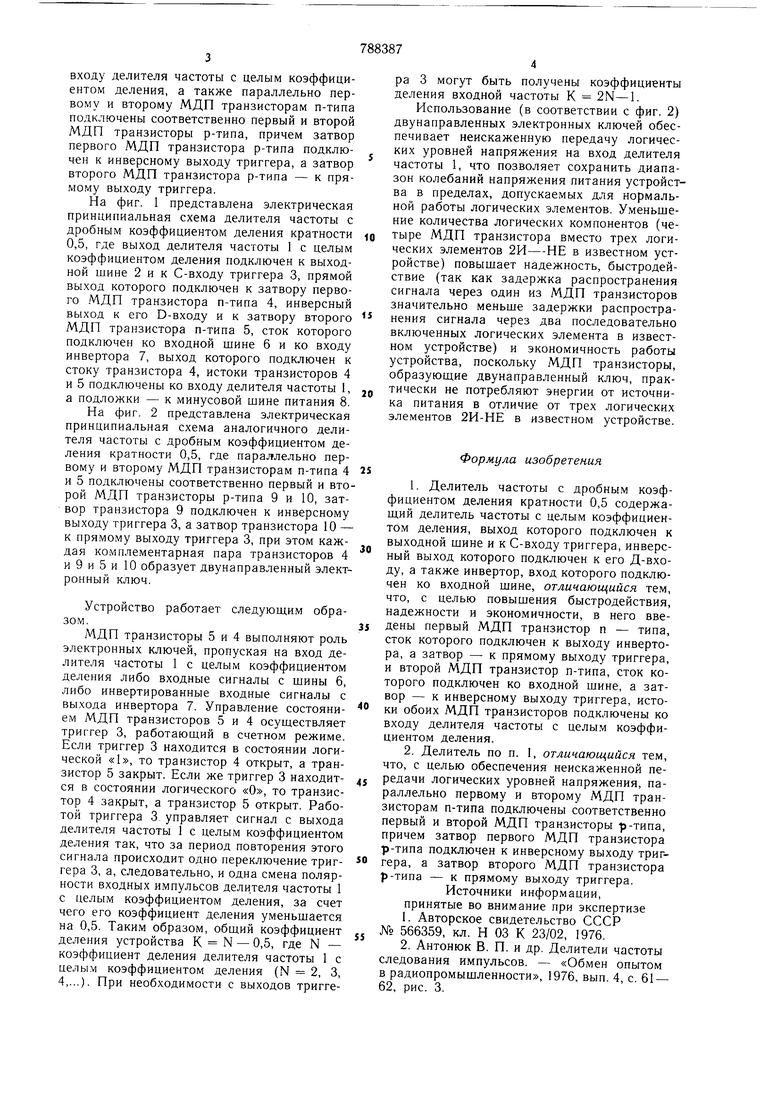

На фиг. 1 представлена электрическая принципиальная схема делителя частоты с дробным коэффициентом деления кратности 0,5, где выход делителя частоты 1 с целым коэффициентом деления подключен к выходной шине 2 и к С-входу триггера 3, прямой выход которого подключен к затвору первого МДП транзистора п-типа 4, инверсный выход к его D-входу и к затвору второго МДП транзистора п-типа 5, сток которого подключен ко входной шине 6 и ко входу инвертора 7, выход которого подключен к стоку транзистора 4, истоки транзисторов 4 и 5 подключены ко входу делителя частоты 1, а подложки - к минусовой шине питания 8.

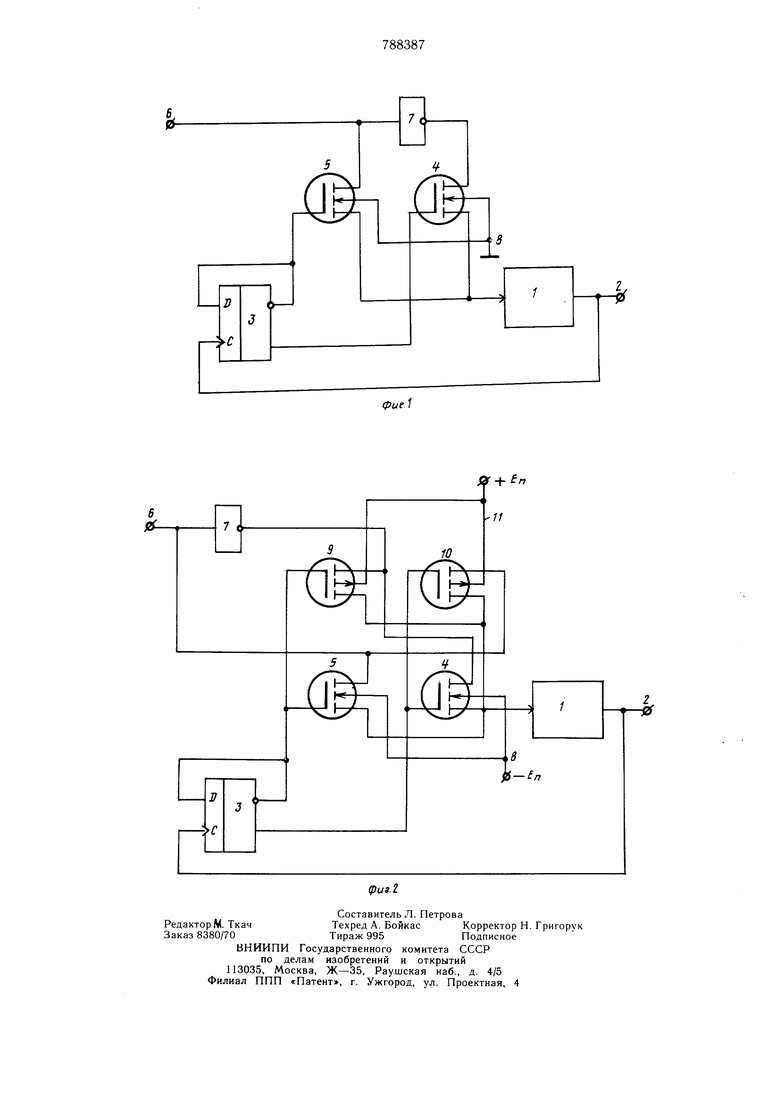

На фиг. 2 представлена электрическая принципиальная схема аналогичного делителя частоты с дробным коэффициентом деления кратности 0,5, где параллельно первому и второму МДП транзисторам п-типа 4 и 5 подключены соответственно первый и второй МДП транзисторы р-типа 9 и 10, затвор транзистора 9 подключен к инверсному выходу триггера 3, а затвор транзистора 10 - к прямому выходу триггера 3, при этом каждая комплементарная пара транзисторов 4 и 9 и 5 и 10 образует двунаправленный электронный ключ.

Устройство работает следующим образом.

МДП транзисторы 5 и 4 выполняют роль электронных ключей, пропуская на вход делителя частоты 1 с целым коэффициентом деления либо входные сигналы с шины 6, либо инвертированные входные сигналы с выхода инвертора 7. Управление состоянием МДП транзисторов 5 и 4 осуществляет триггер 3, работающий в счетном режиме. Если триггер 3 находится в состоянии логической «1, то транзистор 4 открыт, а транзистор 5 закрыт. Если же триггер 3 находится в состоянии логического «О, то транзистор 4 закрыт, а транзистор 5 открыт. Работой триггера 3 управляет сигнал с выхода делителя частоты 1 с целым коэффициентом деления так, что за период повторения этого сигнала происходит одно переключение триггера 3, а, следовательно, и одна смена полярности входных импульсов дели.теля частоты 1 с целым коэффициентом деления, за счет чего его коэффициент деления уменьшается на 0,5. Таким образом, общий коэффициент деления устройства К N - 0,5, где N - коэффициент деления делителя частоты 1 с целым коэффициентом деления (N 2, 3, 4,...). При необходимости с выходов триггера 3 могут быть получены коэффициенты деления входной частоты К 2N-1.

Использование (в соответствии с фиг. 2) двунаправленных электронных ключей обеспечивает неискаженную передачу логических уровней напряжения на вход делителя частоты 1, что позволяет сохранить диапазон колебаний напряжения питания устройства в пределах, допускаемых для нормальной работы логических элементов. Уменьшение количества логических компонентов (четыре МДП транзистора вместо трех логических элементов 2И-НЕ в известном устройстве) повышает надежность, быстродействие (так как задержка распространения сигнала через один из МДП транзисторов значительно меньше задержки распространения сигнала через два последовательно включенных логических элемента в известном устройстве) и экономичность работы устройства, поскольку МДП транзисторы, образующие двунаправленный ключ, практически не потребляют энергии от источника питания в отличие от трех логических элементов 2И-НЕ в известном устройстве.

Формула изобретения

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-12-15—Публикация

1979-02-06—Подача