(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Цифровой вольтметр | 1979 |

|

SU843221A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1462475A1 |

| Устройство для измерения температуры | 1988 |

|

SU1589080A1 |

| Рекурсивное вычислительное устройство | 1988 |

|

SU1522264A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Компаратор отношений сопротивлений | 1977 |

|

SU661411A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2005 |

|

RU2292051C2 |

1

Изобретение относится к электроизмерительной и вычислительной технике и используется в цифровых вольтметрах, однопредельных широкодиапазонных аналого-гшфровых преобразователях и информационно-измерительных системах.

Известен аналого-цифровой преобразователь, содержащий источник эталонного напряжения, две пары управляемых ключей, резистивный делитель, состоящий из двух последовательгтых резисторов, блок управления и последовательно включенные усилитель, преобразователь аналог-код, цифровой счетно-решающий блок и выходной блок, причем входы первой пары управляемых ключей соединены с выводами источника эталонного напряжения, один из которых соединен с входом сигнала, а выходы - с входом резистивного делителя, входы второй пары управляемых ключей соединены соответственно с входом и выходом резистивного делителя, а выходы - со входом усилителя. Управляющие входы

ключей преобразователя аналог-код и счетно-решающего блока соединены с соответствующими выходами блока управления С1 .

Недостатком данного аналого-цифрового преобразователя является низкая точность преобразования в широком динамическом диапазоне изменения входных сигналов.

Цель изобретения - повышение точности преобразования в широком динамическом диапазоне изменения входных сигналов.

Поставленная цель достигается тем, что в известный аналого-цифровой преобразователь, содержащий источник эталонного напряжения, первый выход которого соединен с первым входом первого ключа, второй вход которого соединен с первым выходом блока управления, вто рой выход источника эталонного напряжения соединен с первым входом второ- то ключа, второй вход которого соединен с выходом первого ключа, входом третьего ключа и первым выводом первого резистора резнетивного делителя, второй вывод которого соединен с первым входом четвертого ключа и с первым выводо второго резистора резнетивного делителя второй вывод которого соединен с общей шиной, вторые входы третьего и четвертого ключа соединены с третьим и четвертым выходами блока управления соответственно, пятый, шестой и седьмой выходы которого соединены соответсгвенно с первыми входами преобразователя аналог-код, цифрового счетно-решающего блока, выходного блока, второй вход которого соединен с выходом цифрового счетно-решающего блока, второй йход которого соединен с выходом преобразователя аналог-код, второй вход которого соединен с выходом усиЛителя, введены источник, опорного напряжения, три ключа, регулируемый усилитель, и конденсатор, при этом первая обкладка которого соединена с общей щиной, а вторая - с выходом пятого ключа и первым входом регулируемого усилителя, второй вход которого соединен с выходами третьего и четвертого ключей, а выход - с входом усилителя и первым входом пятого ключа, второй вход которого соединен с восьмым выходом блока Qуправления, а выход источника опорного напряжения соединен с первым входом шестого ключа, второй вход которого соединен с девятым выходом блока упраления, а выход - с первым входом второго ключа, первый вход которого соединен с входной шиной, а второй вход с десятым входом блока управления.

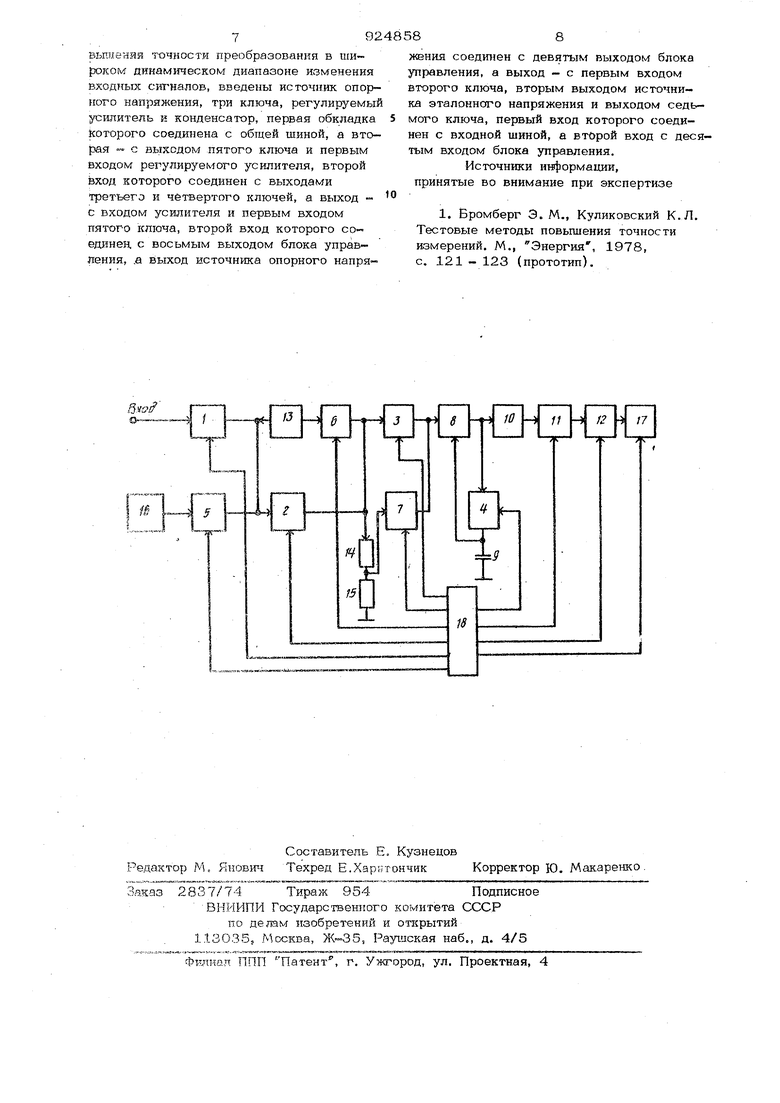

На чертеже представлена структурная схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь содержит регистрируемый усилитель 8, конденсатор 9, усилитель Ю, преобразо вателъ 11 аналог-код, цифровой счетнорешающий бло 12, источншс эталонного напряжения 13, резисторы 14 и 15 ре™ зистивного делителя, источник 16 опор™ ного напряжения, выходной блок 17, блок 18 управления. Блок 18. управления осуществляет синхронизацию работы управляемых ключей 1 7, преобразователя аналог-код 11 и цифрового счет но-решающего блока 12. Коэффициент усиления регулируемого усилителя 8 регулируется так, что при динамическом диапаэойе изменения входного сигнала в раз, коэффициент усиления меняется в Vft раз. А величийа опорного на92

циент усиления регулируемого усилителя 8 устанавливается в начале первого такта и сохраняется постоянным в течение последующих тактов за счет сохранения управляющего напряжения на конденсаторе 8. С выхода регулируемого усилителя 8 напряжение также поступает на вход последовательно включенных усилителя 10 и преобразователя 11 аналог-код. С выхода преобразователя 11 записывается в цифровом счетно-реагающем блоке 12 код числа

,

где К - коэффициент усиления, установленный в начале такта ; и - напряжение входного сигнала; N0 - смещение нуля градировочной характеристики для выбранного аппроксимирующего участка. В течение второго такта ключи 1, 3 и 6 открыты, клЬчи 2, 4,5 и 7 закрыты. Напряжение входного сигнала включено посдедовательно с иапряжением 1«:точника 13 эталонного напряжения и на вход регулируемого усилителя 8 поступает сумма этих напряжений. С выхода преобразователя 11 в цифровое счетно-решающее устройство 12 затитсываетоя число 4 пряжения источника 16 выбирается в, Ж раз меньше максимального значения входного сигнала. В процессе автоматического регулирования коэффициента усиления происходит перераспределение динамических диапазонов между входным сигналом и опорным напряжением. Динамический диапазон входного сигнала сужает в ifA раз, а динамический диапазон опорного напряжения расширяется во столько же раз, что и позволяет восстанавливать динамический диапазон цифрового сигнала, адекватного входному, с помощью деления в цифровом счетнорешающем блоке 12. Устройство работает следующим образом. В течение первого такта ключи 1-4 открыты, ключи 5, 6 и 7 закрыты. Вход- ной сигнал через открытые кг1ючи. 1, 2 и 3 поступает на вход регулируемого усилителя 8. Выходное напряжение регулируемого усилителя В через открытый. ключ 4 поступает на конденсатор 9, ко- торый запоминает его. С конденсатора 9 регулирующее напряжение поступает на регулирующий вход регулируемого усилителя 8, при этом, чем больше входное напряжение, тем меньше коэффициент усипения усилителя 8 и наоборот. КоэффиИеЧих + )о, . где Ug - значение напряжения эталонно источника. В течение третьего такта ключи 1, 2и 7 открыты, ключи 3-6 закрыть. Входной сигнал через открытые ключи 1 и 2 поступает на вход резистивного делителя, состоящего из -двух последовательно соединенных резисторов 14 и 15, с выхода которого через открытый ключ 7 поступает на вход регулируемого усилителя 8.-В цифровой счетно-решающий блок 12 записывается код числ , /где - коэффициент деления резистив ного делителя на резисторах 14 и 15. В течение четвертого такта ключи 2 3и 5 открыты, ключи 1, 4, 6 и 7 закрыты. На вход регулируемого усилителя 8 поступает напряжение с выхода опорного источника 16. В цифровое. счетно-решающее устройство 12 записывается код числа . гдеОоп- величина опорного напряжения Ц0 -смещение Нуль градировочной характеристики для выбранного аппрокси мирующего линейного участка. В течение пятого такта ключи 3, 5 и 6 открыты, ключи 1, 2, 4 и 7 закры ты. Источники опорвюго и эталонного напряжений включены последовательно и на вход регулируемого усилителя 8 поступает сумма двух напряжений. В цифровой счетно-решающий блок 12 записывается код числа Hg Ki Ug Oonl+No.. Во время шестого такта ключи 2, 5 и 7 открыты, ключи 1, 3, 4 и 6 закры ты. Опорное напряжение поступает на вход регистраторного делителя 14 и 15 с выхода которого через открытый ключ на вход регулируемого усилителя 8. В цифровой счетно-решающий блок 12 зап сьтается коп числа . После этого цифровой счетно-решающий блок 12 производит обработку данных по мере их поступления по следую- щему алгоритму: (N,-N)( 4) iV)() Результат обработки связан с входным напряжением следующим соотношением : т. е, не зависит от коэффициента усиления регулируемого усилителя 8 и параметров градуированной характеристики, точности и стабильности эталонного напряжения и резистивного делителя, а определяется лишь стабильностью источтзкка опорного напряжения. Результат обработки переписывается в конце шосла измерений в выходной блок 17 по команде с блока 18 управления и сохраняется в нем до поступления результата следующих вычислений. ИсполЕзЗование дополнительной пары управляемых ключей на входе AUTI с источником опорного напряжения исключает влияние нестабильности эталонного напряжения и коэффициента деления резистивного делителя на точность преобразования, что позволяет получить более высокую точность. Формула изобретения Аналого-цифровой преобразователь, содержащий источник эталонного напряжения, первый выход которого соединен с первым входом первого ключа, второй вход которого соединен с первым выходом блока управления, второй выход источнтса эталонного напряжения соединен с первым входом второго ключа, второй вход которого соединен с вторым выходом блока управления, а выход соединен с выходом первого ключа, входом третьего ключа и первым выводом первого резистора резистивного делителя, второй вывод которого соединен с первым входом четвертого ключа и с первым выводом второго резистора резистивного делителя, второй вывод которого соединен с обшей шиной, вторые входы третьего и четвертого ключей соединены с третьим и четвертым выходами блока управления соответственно, пятый, шестой и седьмой выходы которого соединены соответственно с первыми входами преобразователя аналог-код, цифрового счетно-решающего блока, выходного блока, второй вход которого соединен с выходом цифрового счетно-решающего блока, второй вход которого соединен с выходом преобразователя аналог-код, второй вход которого соединен с выходом усилителя,- о т л и - ч а ю ш и и с я тем, что, с целью по792вьЕяений точности преобразования в широком дикам51ческом диапазоне изменения входных сигналов, введены источник опорного напряжения, три ключа, регулируемый усилитель к конденсатор, первая обкладка Которого соединена с общей шиной, а вторая с выходом пятого ключа и первым входом регулируемого усилителя, второй вход которого соединен с выходами третьего и четвертого ключей, а выход с входом усилителя и первым входом пятого ключа, второй вход которого соединен, с восьмым выходом блока управления, .а выход источника опорного напря8жения соединен с девятым выходом блока управления, а выход - с первым входом второго ключа, вторым выходом источника эталонного напряжения и выходом седьмого ключа, первый вход которого соединен с входной шиной, а второй вход с десятым входом блока управления. Источники ии зормагши, принятые во внимание при экспертизе 1. Бромберг Э. М., Куликовский К. Л. Тестовые методы повьпиения точности измерений. М., Энергия, 1978, с. 121 - 123 (прототип).

Авторы

Даты

1982-04-30—Публикация

1980-10-10—Подача