1

Изобретение относится к технике связи и может быть использовано в системах передачи дискретной информации по каналам связи.

Известно устройство для узловой синхронизации декодера сверточного кода, которое содержит блоки сложения, сравнения и выбора метрик, подключенные к запоминающему устройству, блок для определения максимальной и ближайшей к максимальной метрике и блок для вычисления абсолютной разницы между максимальной и ближайшей к ней метриками. В известном устройстве вычисленная абсолютная разница метрик накапливается и сравнивается с порогом. Если накопленная величина меньше выбранного порога, то принимается решение об изменении узловой синхронизации 1.

Недостатком известного устройства является необходимость хранить большое количество информации и производить большое число операций, что

Приводит к усложнению аппаратуры и снижению быстродействия.

Известно также устройство для узловой синхронизации сверточного декодера, содержащее логическое устройство единогласия, подключенное к выходному устройству сверточного декодера, накопитель импульсов неединогласия и решающее устройство. При .превышении количеством импульсов неединогласия, накопленных в накопителе определенного порога, принимается решение об изменении узловой синхронизации декодера {2},

Недостаток данного устройства состоит в большом времени синхронизации и недостаточно высокая помехоустойчивость.

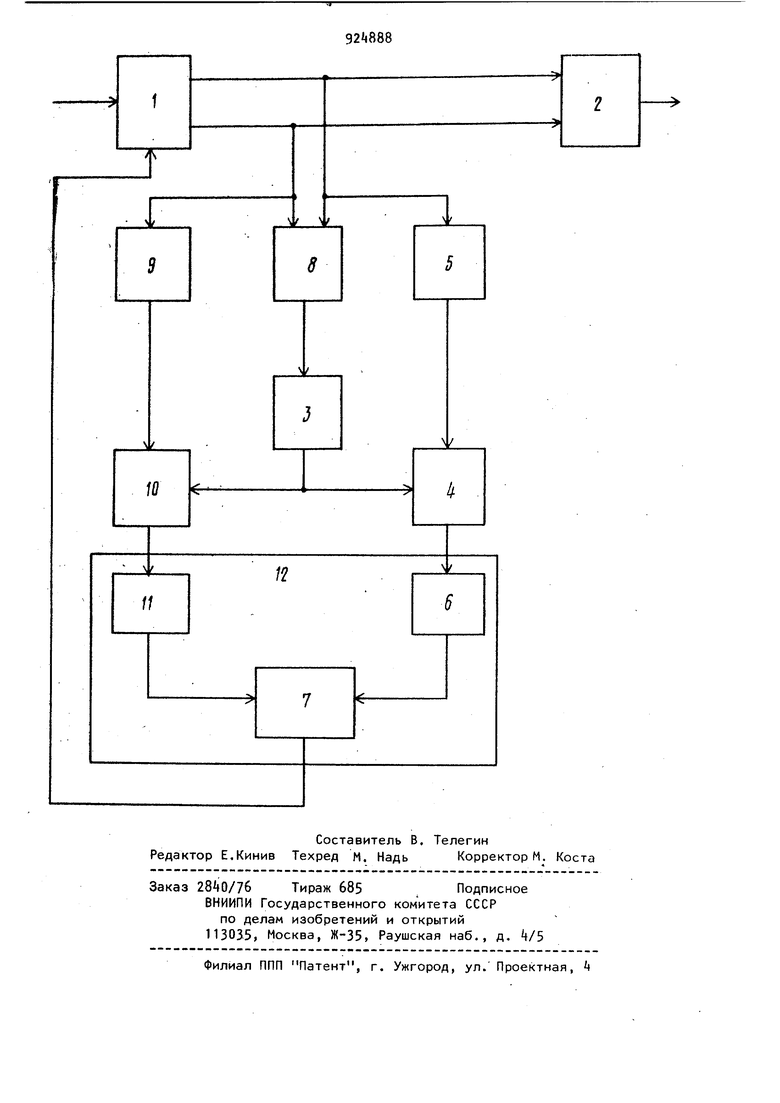

Наиболее близким к предлагаемому является устройство для синхронизации сверточного декодера, которое содержит узел выделения и распре.деления последовательности принимаемых к&нальных СИМВС5ЛОВ, кодовый ге39нератор, сумматор по модулю два, ли нию задержки, накопитель, решающее устройство и декодер сверточного ко да 3. Недостатком такого устройства яв ляется большое время установления с хронизма и невысокая помехоустойчивость. Цель изобретения - повышение помехоустойчивости устройства для узловой синхронизации сверточного декодера при одновременном снижении времени установления синхронизма. Поставленная цель достигается тем, что в устройство для узловой синхронизации сверточного декодера содержащее блок выделения и распределения последовательности принимаемых канальных символов, первый и второй выходы которого подключены к входам декодера, причем первый выход блока выделения и распределения последовательности принимаемых канальны символов через первую линию задержки соединен с первымвходом первого сум матора по модулю два, выход которого подключен к первому входу решающего устройства, выход которого соединен с управляющим входом блока выделения и распределения последовател ности принимаемых канальных символов а также кодовый генератор, выход которого подключен к второму -входу сум матора по модулю два, введены кодовы инвертор, первый и второй входы которого соединены соответственно с первым и вторым выходами блока выделения и распределения последовательности принимаемых канальных символов, а выход подключен к входу кодового генератора, вторая линия задержки, вход которой соединен с вторым выходом блока выделения и распределения последовательности принимаемых канальных символов, а выход подключен к первому входу второго сумматора по модулю два, выход которого соединен с вторым входом решающего устройства, причем второй вход второго сумматора по модулю два подключен к выходу кодового генератора. Кроме того, решающее устройство содержит два накопителя, входы которых являются соответственно первым и вторым входами решающего устройства, причем их выходы соединены с входами двухпорогового анализатора, выход которого является вы ХОДОМ решающего устройства, причем кодовый инвертор выполнен в виде сумматора по модулю два. На чертеже представлена функциональная схема устройства для узловой синхронизации сверточного декодера. Устройство для узловой синхронизации сверточного декодера содержит блок 1 вьщеления и распределения последовательности принимаемых канальных символов, выходы которого подключены ко входам декодера 2, кодовый генератор 3, выход которого подключен ко второму входу первого сумматора 4 по модулю два, первую линию 5 задержки, вход которой соединен с первым выходом блока 1 выделения и распределения последовательности принимаемых канальных символов, а ее выход подключен к первому входу первого сумматора по модулю два, причем выход сумматора по модулю два соединен со входом первого накопителя 6. Выход первого накопителя 6 подключен к первому входу двухпорогового анализатора 7, выход которого подключен к управляющему входу блока 1 выделения и распределения последовательности принимаемых символов. В состав устройства для узловой синхронизации сверточного декодера входят также кодовый инвертор 8, например, сумматор по модулю два, входы которого подкл1бчены к выходам блока 1 выделения и распределения последовательности принимаемых символов, а выход соединен со входом кодового генератора 3, вторая линия задержки 9, вход которой подключен ко второму выходу блока 1 выделения и распределения последовательности принимаемых канальных символов, а выход соединен с первым входом второго сумматора 10 по модулю два, выход которого подключен ко входу второго накопителя 11. Выход второго накопителя 11 соединен со вторым входом двухпорогового анализатора 7, а выход кодового генератора 3 подключен также ко второму входу второго сумматора 10 по модулю два. Первый и второй накопители 6 и 11 и двухпороговый анализатор 7 образуют решающее устройство 12, Устройство для, узловой синхронизации сверточного декодера работает следующим образом. Поступающий из канала связи сигнол в блоке 1 выделения и распределе ния последовательности принимаемых канальных символов преобразуется, в две последовательности символов Т (D и т(0), где О - символ задержки. В начальный момент времени указанные последовательности могут формироваться из принимаемых сигналов, соответствующих выходным последовательностям С (0)и 0(0) кодовых генераторов кодера. При правильно установленной, синхронизации последовательность Т {D) формируется из последовательности G(D), а Т (0) -из G(D), но в случае неверно установленной узловой синхронизации последовательность Т (D может формироваться из G (о) , а T(D) - из последовательно.сти G (О) . С выхода блока 1 выделения и распределения последовательности принимаемых канальных сикчволов последовательности T(D) и Т (О) поступают н входы кодового инвертора 8 и декодера 2. Кроме того, последовательность flO) через первую линию задержки 5 подается на первый вход первого сумматора пОдМОдулю два, а последовательность T(D) через вторую линию задержки 9 поступает на первый вход второго сумматора 10 по модулю два. На выходе кодового инвертора 8 с некоторой задержкой формируется, оцен ка исходной информационной последовательности 3(0) с умноженным количеством ошибок. Оценка 3 (D) с выхода кодового инвертора 8 поступает на вход кодового генератора 3 с генераторным полиномом G(D). В кодовом генераторе 3 вычисляется оценка Т (D) последовательности Т(0), которая в первом сумматоре по модулю два сравнивается с последовательностью Т (D), задержанной в первой линии задержки 5 на время обработки информации в кодовом инверторе 8 и кодовом генераторе 3. При отсутствии ошибок в канале и правильно установленной синхронизации результат сравнения на выходе сумматора по модулю два равен нулю. Если в канале имеются ошибки, результат сравнения отличен от нуля. Результат сра нения с выхода первого сумматора по модулю два подается на вход первого накопителя 6 решающего устройства 12. Во втором сумматоре 10 по модулю два производителя сравнение последовательности Т (О) с последователь О / ностью т (D), Задержанной в линии задержки 9 Если ошибки в канале отсутствуют и узловая синхронизация установлена верно, то результат сравнения на выходе сумматора 10 по модулю два с вероятностью 0,5 будет равен единице. Результат второго сравнения с выхода второго сумматора 10 по модулю два поступает на вход вто-, рого накопителя 11, решающего устройства 12. Выходные сигналы накопителей 6 и 11 подаются на входы двухпорогового анализатора 7, который выносит решение о необходимости изменения состояния узловой син фонизации только в том случае, когда сигнал со второго накопителя 11 не превышает установленного порога, а сигналом с первого накопителя 6 порог превышен, В этом случае на выходе двухпорогового анализатора 7 формируется управляющий сигнал, который подается на управляющий вход блока 1 выделения и распределения последовательности принимаемых канальных импульсов и обеспечивает изменение узловой синхрони%зации. Если же выходные сигналы обоих накопителей 6 и 11 не превышают установленный порог либо оба одновременно превышают пороговое значение, то в этом случае двухпороговый анализатор 7 принимает решение о сохранении состояния узловой синхронизации на следующий интервал анализа. Предлагаемое изобретение по сравнению с известными устройствами снижает вероятность срыва синхронизма и тем самым повышает помехоустойчивость устройства для узловой синхронизации сверточного кода. Формула изобретения 1. Устройство для узловой синхронизации сверточного декодера, содержащее блок выделения и распределения последовательности принимаемых канальных символов, первый и второй выходы которого подключены к входам декодера, причем первый выход блока выделекйя и распределения последовательности, принимаемых канальных символов

через первую линию задержки соединен с первым входом первого сумматора по модулю- два, выход которого подключен к первому входу решающего устройства, эыход которого соединен с управляющим входом блока выделения и распределе ия последовательности принимаемых канальных символов, а также кодовый генератор, выход которого подключен к второму входу сумматора по модулю два, отличающееся тем, что, с целью повышения помехоустойчивости . при одновременном снижении времени установления синхронизма, в него введены кодовый инвертор, первый и второй входы которого соединены соответственно с первым и вторым выходами блока выделения и распределения последовательности принимаемых канальных символов, а выход подключен к входу кодового генератора, вторая линия задержки, вход которой соединен с вторым-выходом блока выделения и распределения последовательности принимаемых канальных символов, а выход подключен к первому входу второго сумматора по модулю два, выход которого соединен с вторым входом решающего устройства, причем второй вход второго сумматора по модулю два подключен к выходу кодового генератора.

2.Устройство по п,1, о т л и чающееся тем, что решающее устройство содержит два накопителя, входы которых являются соответственно первым и вторым входами решающего устройства, причем их выходы соеди нены с входами двухпорогового анализатора, выход которого является выходом решающего устройства.

3.Устройство по п.1, о т л и чающееся тем, что кодовый инвертор выполнен в виде сумматора по модулю два.

Источники информации, принятые во внимание при экспертизе

1. Патент США № , кл. 3iO-l46 61 А Q, опублик. 1975.

2.Патент США ff 3.789.359, л. 1 О, опублик. 1972.

3.Авторское свидетельство СССР , кл. Н L 1/10, 18.05.73

(прототип) ,

f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство узловой синхронизации сверточного декодера | 1973 |

|

SU467484A1 |

| Устройство для узловой синхронизации в системах передачи информации | 1981 |

|

SU960896A1 |

| Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией | 1990 |

|

SU1795499A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Многоканальный приемник с кодовым разделением каналов для приема квадратурно-модулированных сигналов повышенной структурной скрытности | 2016 |

|

RU2610836C1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМНИК С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ ДЛЯ ПРИЕМА КВАДРАТУРНО-МОДУЛИРОВАННЫХ СИГНАЛОВ ПОВЫШЕННОЙ СТРУКТУРНОЙ СКРЫТНОСТИ | 2013 |

|

RU2544767C1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В КАНАЛАХ С ГРУППИРОВАНИЕМ ОШИБОК | 1998 |

|

RU2127956C1 |

12

/

Авторы

Даты

1982-04-30—Публикация

1979-04-12—Подача