1

Изобретение относится к системам передачи информации по каналам связи.

Известно устройство узловой синхронизации декодера сверточного кода, содержащее схему определения метрик путей, схему сравнения метрик путей, а также схемы сравнения приращения метрик с различными порогами t.1

Однако это устройство имеет отно-сительно низкую помехоустойчивость, j..

Наиболее близким к предложенному по технической сущности является устройство узловой синхронизации сверточного декодера, содержащее узел „ выделения и распределения последовательности принимаемых канальных символов, выходы которого подключены ко входу декодера, линию задержки, выход которой подключен к первому входу сут-2о матора по модулю два, выход которого подключен к решающему узлу, выход которого подключен ко входу узла выделения и распределения последовательности принимаемых канальных симво лов Г2.

Однако в данном устройстве при ис- пользовании кодового генератора, ана- логичного одному из кодовых генераторов кодера сверточного кода, существуют периодические последовательности , при которых и при неправильной фазе узловой синхронизации расхождение входной и выходной кодовыми последовательностями небольшое. Так как порог решающего узла, выбранный из расчета устойчивой работы устройства при минимальном рабочем со отношении сигнал-шум, оказывается в этом случае относительно высоким, то не происходит установка правильной фазы узловой синхронизации, т.е. достоверность устройства невысока.

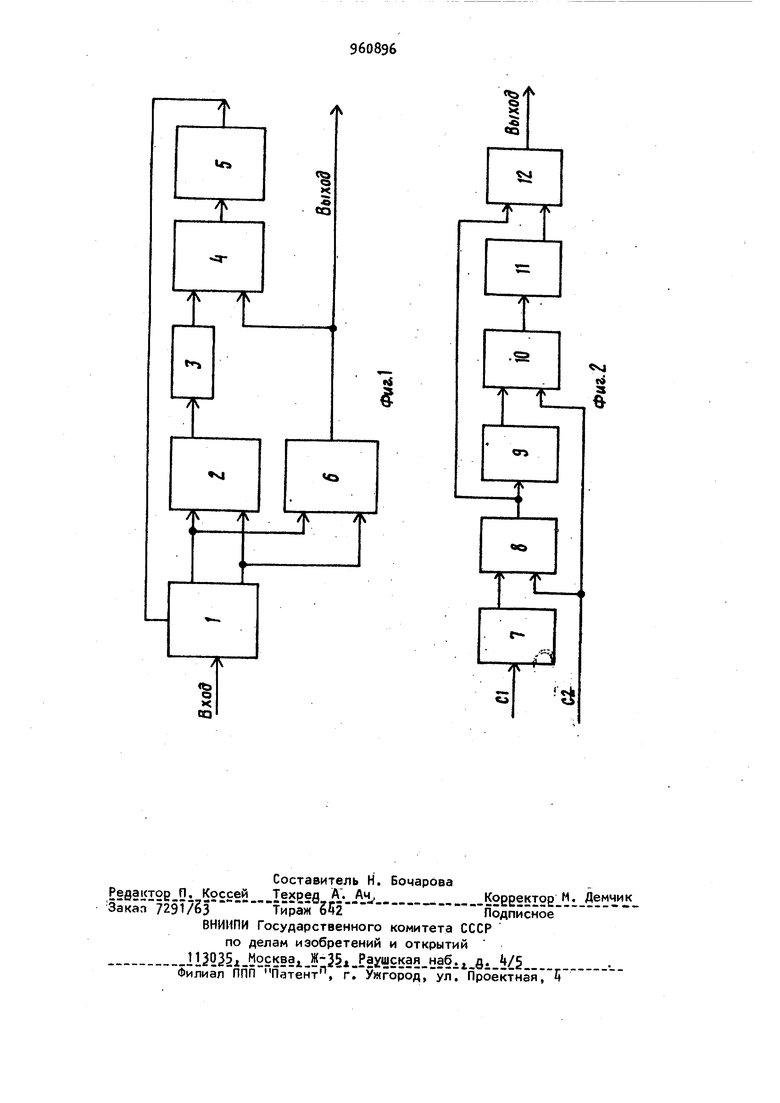

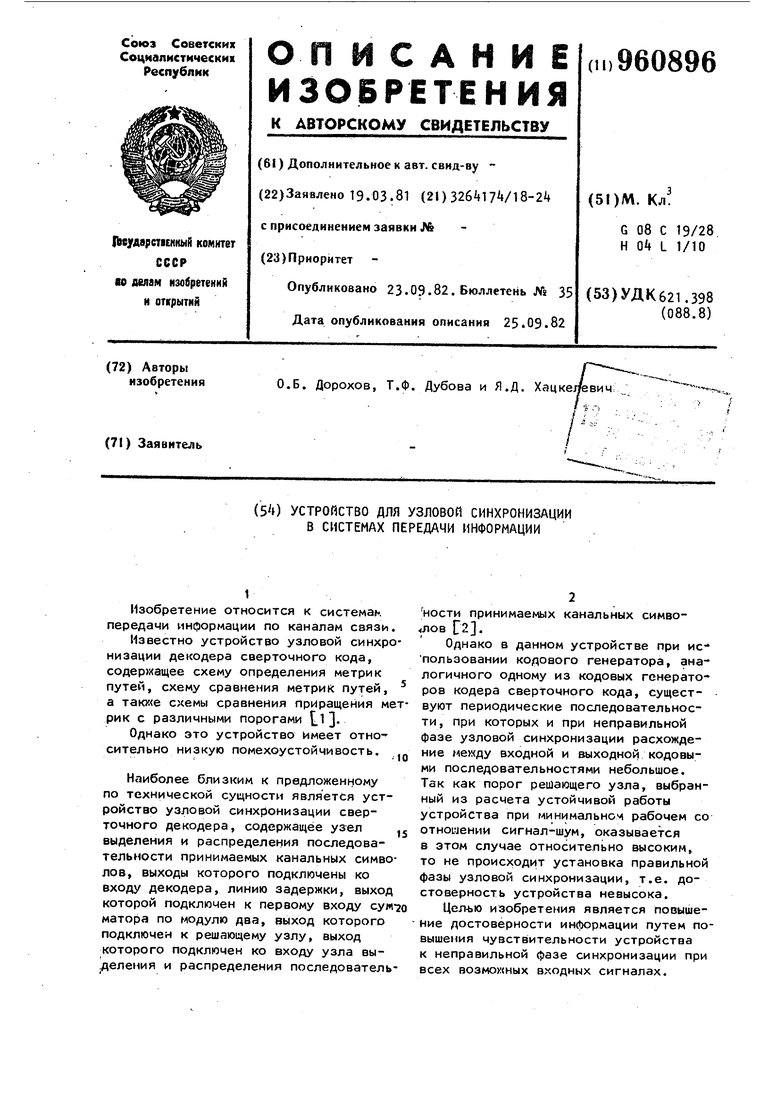

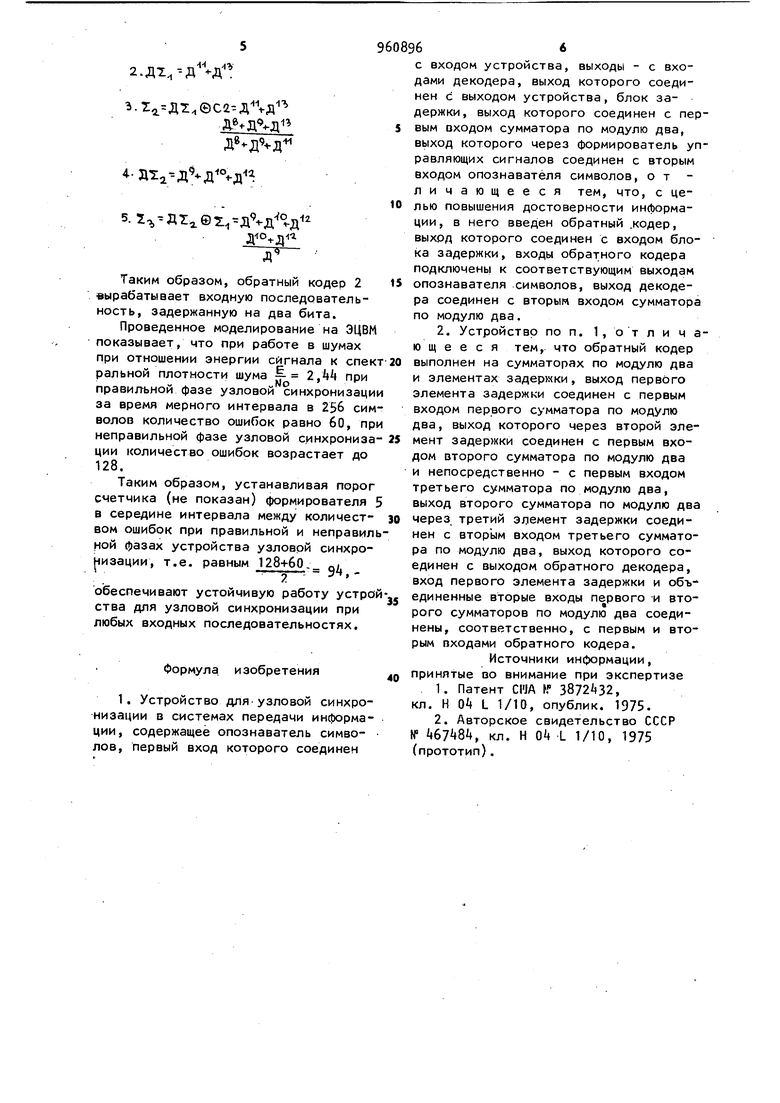

Целью изобретения является пооыше- ние достоверности информации путем повышения чувствительности устройства к неправильной фазе синхронизации при всех возможных входных сигналах. 3960 Поставленная цель достигается тем, что в устройство для узловой синхронизации в системах передачи информации , содержащее опознаватель символов, первый вход которого соединен с входом устройства, выходы - с входами декодера, выход которого соединен С выходом устройства, блок задержкИ, выход которого соединен с первым входом сумматора по модулю два, выход которого через формирователь управляющих сигналов соединен с вторым входом опознавателя символов, введен обратный кодер, выход которого соединен Ь входом блока задер : ки, входы обратт ного кодера подключены к соответствующим выходам опознавателя символов, выход декодера соединен с вторым входом сумматора по модулю два. Обратный кодер выполнен на суммато рах по модулю два и элементах задержки , выход первого элемента задержки соединен с первым входом первого сумматора по модулю два, выход которого через второй элемент задержки соединен с .первым входом второго сумматора по модулю два и непосредственно с первым входом третьего, сумматора по модулю два, выход второго сумматора по модулю два через третий элемент задержки соединен с вторым входом третьего сумматора по модулю два,, выход которого соединен с выходом обратного декодера, вход первого элемента задержки и объединенные вторые входы первого и второго сумматоров по модулю два соединены, соответственно, с первым и вторым входами обратного кодера. На фиг. 1 приведена схема устройства; на фиг. 2 - схема обратного кодера. Устройство для узловой синхронизаг ции в системах передачи информации со держит опознаватель 1 символов, обратный кодер 2, блок 3 задержки, сумматор по модулю два, формирователь управляющих сигналов, декодер 6. Обратный кодер 2 содержит элемент 7 задержки, сумматор 8 по модулю два, вто рой элемент 9 задержки, второй сумма тор 10 по модулю два, третий элемент 11 задержки, третий сумматор 12 по модулю два. Устройство для узловой синхронизации работает следующим образом. Полученные в опознавателе 1 каналь ные символы С1 и С2 подаются на вхо4ды декодера 6 и обратного кодера 2. 3 обратном кодере 2 производится восстановление входной информационной последовательности путем операций, обратных кодированию, С выхода обратного кодера 2 информационная последовательность поступает на вход блока 3 задержки, где она задерживается на время, необходимое для обработки информации в декодере 6. Полученные информационные последовательности с выхода декодера бис блока 3 задержки подаются на входы сумматора 4 по модулю два, где происходит их сравнениё. Предлагаемое устройство в отсутствии шумов при неправильной фазе не выходе сумматора -по модулю два при любой информационной последовательно Уи имеет 50 ошибочных символов, прошедших за время выбранного мерного интервала, например если выбрать мерный интервал равным 256 симполам, количество ошибок равно 1281:1. С выхода формирователя- 5 сигнал управления подается на опоанаватель 1 символов, выставляя в нем правильную фазу узловой синхронизации. В обратном кодере 2 исправление канальных ошибок, возникающих при шумах в канале, не осуществляется и даже увеличивается в 2-2,5 раза, однако и при наличии шумов при неправильной фазе узловой синхронизации рассогласование между двумя указанными последовательностями равно примерно половине. Обратный кодер 2 для сверточного кода с кодовым ограничителем Каб представляет собой логическую схему (фиг. 2). Алгебраические преобразования, происходящие в обратном кодере, рассмотрим на примере работы со сверточным кодом, порождаемым полиномами tlCq) . -11ССа) Зададим входную последовательность 0000001000000... , т.е. f(x) о , тогда (Х)1(С-1)-ДЧд д 4-ДЧ,д.з (Х)11{са) Проверим работу обратного кодера 2, работающего по схеме, изображенной на фиг. 2: to, п-12. -15 i Т гС-1©С2-Д Д%ДПД - Д 2.ДТ,--Д .12..© 2--Д Д Дв. -ДТ. 5.,. д Таким образом, обратный кодер 2 вырабатывает входную последовательность, задержанную на два бита. Проведенное моделирование на ЭЦВМ показывает, что при работе в шумах при отношении энергии сигнала к спек ральной плотности шума 2,АА при правильной фазе узловой синхронизаци за время мерного интервала в 256 сим волов количество ошибок равно 60, пр неправильной фазе узловой синхрониза ции количество ошибок возрастает до 128. Таким образом, устанавливая порог счетчика (не показан) формирователя в середине интервала между количеством ошибок при правильной и неправил ной фазах устройства узловой синхронизации, т.е. равным 128+60. „i обеспечивают устойчивую работу устро ства для узловой синхронизации при любых входных последовательностях. Формула изобретения 1. Устройство для узловой синхронизации в системах передачи информа ции, содержащее опознаватель символов, первый вход которого соединен 64 с входом устройства, выходы - с входами декодера, выход которого соединен с выходом устройства, блок задержки, выход которого соединен с первым входом сумматора по модулю два, выход которого через формирователь управляющих сигналов соединен с вторым входом опознаватёля символов, от личающееся тем, что, с целью повышения достоверности информации, в него введен обратный .кодер, выход которого соединен с входом блока задержки, входы обратного кодера подключены к соответствующим выходам опознаватёля символов, выход декодера соединен с вторым входом сумматора по модулю два. 2. Устройство по п. 1, о т л и ч аю щ е е с я тем, что обратный кодер выполнен на сумматорах по модулю два и элементах задержки, выход первого элемента задержки соединен с первым входом первого сумматора по модулю два, выход которого через второй элемент задержки соединен с первым входом второго сумматора по модулю два и непосредственно - с первым входом третьего сумматора по модулю два, выход второго сумматора по модулю два через третий элемент задержки соединен с вторым входом третьего сумматора по модулю два, выход которого соединен с выходом обратного декодера, вход первого элемента задержки и объединенные вторые входы первого и второго сумматоров по модулю два соединены, соответственно, с первым и вторым входами обратного кодера. Источники информации, принятые во внимание при экспертизе 1.Патент CIJA К , кл. Н 0 L 1/10, опублик. 1975. 2.Авторское свидетельство СССР № , кл. Н 0 L 1/10, 1975 (прототип).

tr

В к

со

ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство узловой синхронизации сверточного декодера | 1973 |

|

SU467484A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В КАНАЛАХ С ГРУППИРОВАНИЕМ ОШИБОК | 1998 |

|

RU2127956C1 |

| Устройство для узловой синхронизации сверточного декодера | 1979 |

|

SU924888A1 |

| СПОСОБ ПЕРЕДАЧИ ГОЛОСОВЫХ ДАННЫХ В ЦИФРОВОЙ СИСТЕМЕ РАДИОСВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2301492C2 |

| Система для передачи и приема дискретной информации | 1986 |

|

SU1376115A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией | 1990 |

|

SU1795499A1 |

| Декодер сверточного кода | 1985 |

|

SU1320904A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

-

/г

vj

Ч

/ /г

/ Г

/Г

е о

X

00

/

Авторы

Даты

1982-09-23—Публикация

1981-03-19—Подача