(54) РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр | 1981 |

|

SU1024989A1 |

| Устройство для отображения информации на экране матричного индикатора | 1984 |

|

SU1246130A1 |

| Регистр | 1979 |

|

SU860137A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Программируемый трансверсальный фильтр | 1988 |

|

SU1651354A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1987 |

|

SU1529453A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

I

Изобретение относится к цифровой вычислительной технике и. может быть применено в измерительных и вычислительных приборах.

Известен регистр, используемый в аналогоцифровых преобразователях (АЦП) поразрядного уравновешивания 1 .

Однако в известном регистре велико время задержки между появлением сигнала с аналоговой схемы сравнения и цифровым сигналом с выхода развертывающего регистра, что накладывает ограничения на быстродействие АЦП. Кроме того, такие схемы развертывающих регистров характеризуются слож-. костью управления ими и повышенными.требованиями к временному расположению управляющих импульсов 1 .

Наиболее близким к предлагаемому по технической сущности является регистр, содержащий ячейки памяти, каждая из которых выполнена на двух триггерах и элементе И-НЕ 2.

Однако затраты оборудования на один разряд такой схемы велики. Повышение быстродействия и надежности достигается

введением дополнительного триггера. Аштара- турные затраты составляют более двух корпусов микросхем 133-й серии. Для управления такой схемой требуется две серии синхроимпульсов. Способ формирования такой серии управляющих синхроимпульсов, предложенный в зтом регистре, приводит к неодновременности и неравномерности переключений соседних разрядов и выбросам в переходном процессе на выходе цифро-анало10гового преобразователя, входящего в состав АЦП поразрядного уравновешивания.

Целью изобретения является упрощение регистра и повышение его быстродействия.

Поставленная цель достигается тем, что

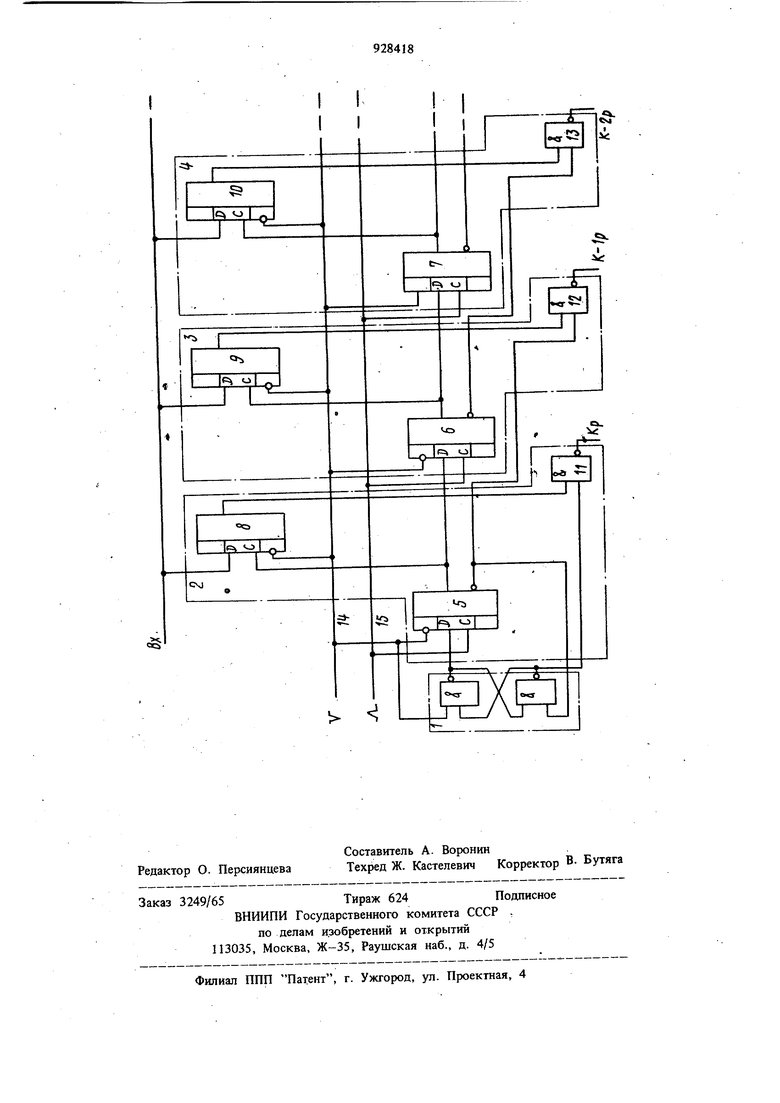

15 в регистре, содержащем ячейки, каждая из которых состоит из основного и вспомогательного триггеров и элементы И-НЕ, RSтриггеров, шину сброса и шину тактовых импульсов, первые входы основных тригге20ров ячеек памяти соединены с информационным входом регистра, а вторые входы I основных триггеров и первые входы вспомогательных триггеров ячеек памяти соедииены с шиной сброса, вторые входы вспомогательных триггеров ячеек памяти соедине ны с ишной тактовых импульсов, выход основного триггера каждой ячейки памяти соединен с первым входом элемента И-НЕ данной ячейки памяти, третий вход основного триггера каждой ячейки памяти соединен с первым выходом вспомогательного триггера данной ячейки памяти и с третьим входом вспомогательного триггера последующей ячейки памяти, второй выход вспомогательного триггера каждой ячейки памяти подклю чен ко второму входу элемента И-НЕ последующей ячейки памяти, кроме первой, третий вход вспомогательного триггера первой ячейки памяти соединен с первым выходом RS-триггера, второй выход KOlbporo соединен со вторым входом элемента И-НЕ первой ячейки памяти, второй выход вспомогательного триггера первой ячейки памяти соединен со вторым входом элемента И-НЕ пояледующей ячейки памяти и с первым вхо дом RS-триггера, второй вход которого подключен к шине сброса, вьгходы элементов И-НЕ ячеек памяти являются выходами регистра. На чертеже изображена функциональная схема предложенного регистра. I Регистр содержит RS-триггер 1, ячейки памяти 2, 3 и 4 (на чертеже показаны только три ячейки памяти), состоящие из вспомогательных триггеров 5-7, основных триггеров 8-10 и элементов И-НЕ 11-13, шину c6ix)ca 14 и шину тактовых импульсов 15 Регистр функционирует следующим образом Сигналом Установка исходнбго состояния все, триггеры 8-10 приводятся в состояние логической 1, а триггеры 5-7 - в состояние логического О. Поэтому на выходах элементов И-НЕ 12 и 13, кроме элемента И-НЕ 11, устанавливается значение О, а на выходе элемента И - значение 1, так как на один из ее входов поступает сигнал О с выхода RS-триггера 1 .С поступлением на шину 15 синхроимпульсы происходит перепись логической 1 из триггера 1 в триггер 5, который сбрасывает триггер 1 в состояние О. Инверсный выход RS-триггера 1 открывает элемент 11. Переход с логического О на логическую 1 триггера 5 вызывает запись информации со входа регистра в регистр 8. Записанный сигнал в инверсном виде поступает на выход регистра через элемент И-НЕ П. Переход с О на 1 триггера 5 вызывает также появление I на выходе следующего разряда регистра, так как инверсный выход триггера 5 закрывает элемент И-НЕ 12. Состояние триггера 7 не изменяется. С поступлегшем следующего 84 синхроимпульса логическая 1 из триггера 5 переписывается в триггер 6, а сам триггер 5 устанавливается в состояние О, открывая своим инверсным выходом элемент И-НЕ 12. Одновременно о этим сигнал со входа регистра записывается и триггер 9 и проинвертироваиный элементом 12, поступает на выход регистра. Последующие ячейки памяти регистра работают аналогично. Применение регистра дает положи1ельный технико-экономический эффект, так как позволяет сократить аппаратурные затраты до 1,25 корпуса микросхем 133-й серии на 1 разряд регистра и обеспечить максимальное его быстродействие. Формула изобретения Регистр, содержащий ячейки памяти, каждая из которых состоит из основного и вспомогательного триггеров и элемента И-НЕ, RS-триггер, шину сброса и щину. тактовых импульсов, отличающийся тем, что, с целью упрощения регистра, в нем первые входы основных триггеров ячеек памяти соединены с информационным входом регистра, а вторые входы основных триггеров и первые входы вспомогательных триггеров ячеек памяти соединены с шиной сброса, вторые входы вспомогательных триггеров ячеек памяти соединены с шиной тактовых импульсов, выход основного триггера каждой ячейки памяти соединен с первым входом элемента И-НЕ данной ячейки памяти, третий вход основного триггера каждой ячейки памяти соединен с первым выходом вспомогательного тирггера данной ячейки памяти и с третьим входом вспомогательного триггера последующей ячейки памяти, второй выход вспомогательного триггера каждой ячейки памяти подключей ко второму входу элемента И-НЕ последующей ячейки памяти, кроме первой, третий вход вспомогательного триггера первой ячейки памяти соединен с первым выходом RS-триггера, второй выход которого соединен со вторым входом элемента И-НЕ первой ячейки памяти, второй выход вспомогательного триггера первой ячейки памяти соединен со вторым входом элемента И-НЕ последующей ячейки памяти и с первым входом RS-триггера, второй вход которого подключен к шине сброса, выходы элементов И-НЕ ячеек памяти являются выходами регистра. Источники информации, принятые во внимание при экспертизе 1.Справочник по интегральным микросхемам. Под ред. Б. В. Тарабрина, М., Энергия, 1980, с. 281. 2.Авторское свидетельство СССР № 44.483, кл. Н 03 К 13/17, 1974 (прототип).

Авторы

Даты

1982-05-15—Публикация

1980-08-01—Подача