(Л

с:

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для сложения N двоично-десятичных чисел | 1988 |

|

SU1587497A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1975 |

|

SU746496A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1043627A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

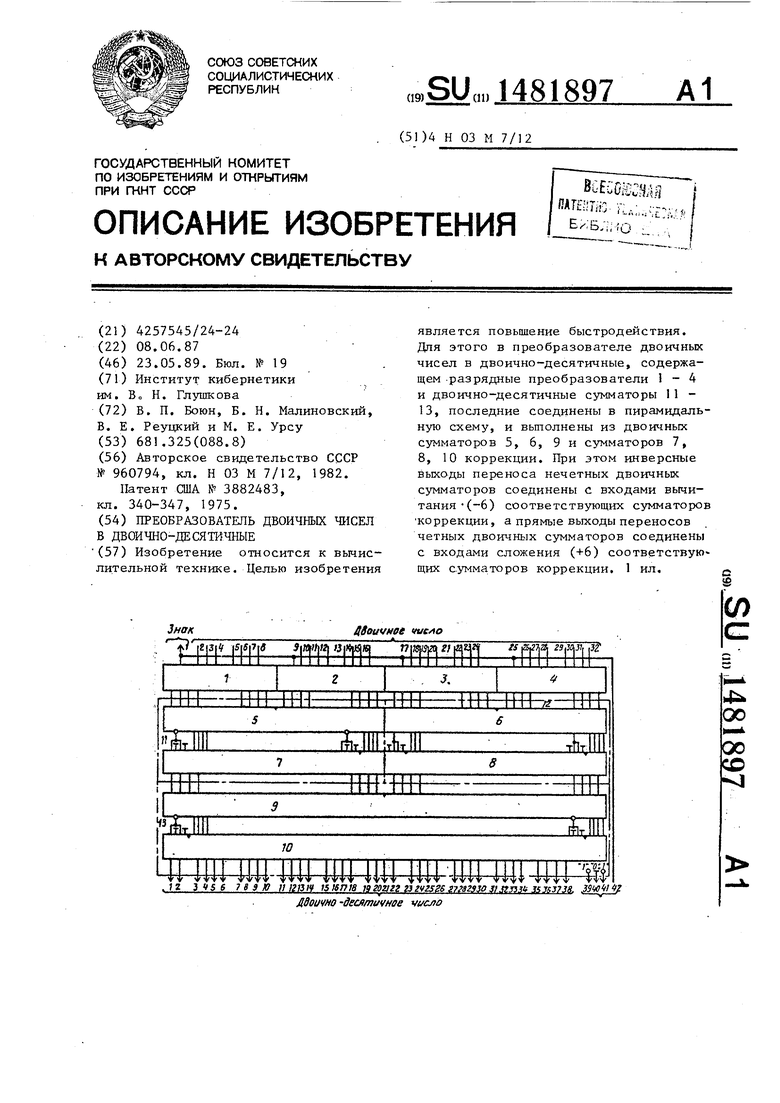

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия. Для этого в преобразователе двоичных чисел в двоично-десятичные, содержащем разрядные преобразователи 1-4 и двоично-десятичные сумматоры 11-13, последние соединены в пирамидальную схему и выполнены из двоичных сумматоров 5, 6, 9 и сумматоров 7, 8, 10 коррекции. При этом инверсные выходы переноса нечетных двоичных сумматоров соединены с входами вычитания (-6) соответствующих сумматоров коррекции, а прямые выходы переносов четных двоичных сумматоров соединены с входами сложения (+6) соответствующих сумматоров коррекция. 1 ил.

&

00 00

со

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении двоично-десятичных преобразова- тел ей.

Целью изобретения является повышение быстродействия.

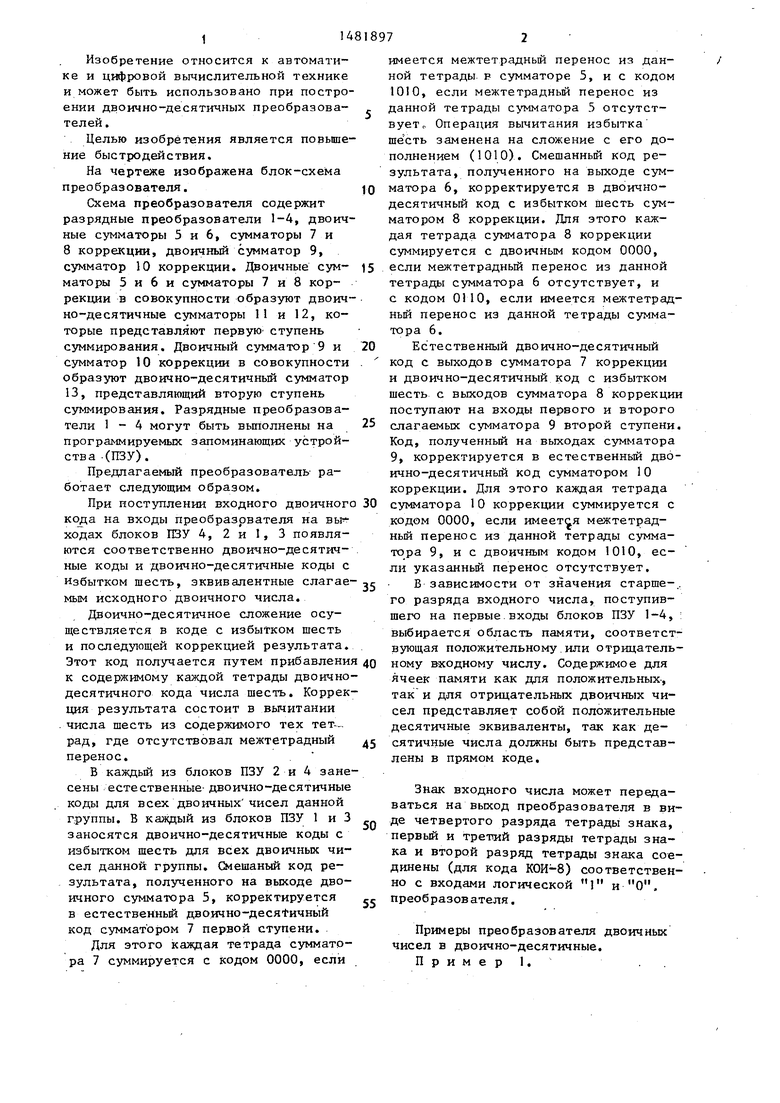

На чертеже изображена блок-схема преобразователя.

Схема преобразователя содержит разрядные преобразователи 1-4, двоичные сумматоры 5 и 6, сумматоры 7 и 8 коррекции, двоичный сумматор 9, сумматор 10 коррекции. Двоичные сум- маторы 5 и 6 и сумматоры 7 и 8 коррекции в совокупности образуют двоично-десятичные сумматоры 11 и 12, которые представляют первую ступень суммирования. Двоичный сумматор 9 и сумматор 10 коррекции в совокупности образуют двоично-десятичный сумматор 13, представляющий вторую ступень суммирования. Разрядные преобразователи 1 - 4 могут быть выполнены на программируемых запоминающих устройства (ПЗУ).

Предлагаемый преобразователь работает следующим образом.

При поступлении входного двоичного кода на входы преобразователя на выходах блоков ПЗУ 4, 2 и 1, 3 появляются соответственно двоично-десятичные коды и двоично-десятичные коды с избытком шесть, эквивалентные слагаемым исходного двоичного числа.

Двоично-десятичное сложение осуществляется в коде с избытком шесть и последующей коррекцией результата. Этот код получается путем прибавления к содержимому каждой тетрады двоично- десятичного кода числа шесть. Коррекция результата состоит в вычитании числа шесть из содержимого тех тет рад, где отсутствовал межтетрадный перенос.

В каждый из блоков ПЗУ 2 и 4 занесены естественные двоично-десятичные коды для всех двоичных чисел данной группы. В каждый из блоков ПЗУ 1 и 3 заносятся двоично-десятичные коды с избытком шесть для всех двоичных чисел данной группы, Смешаный код результата, полученного на выходе двоичного сумматора 5, корректируется в естественньй двоично-десятичный код сумматором 7 первой ступени.

Для этого каждая тетрада сумматора 7 суммируется с кодом 0000, если

.

5 0 5

0 г

0 д

0

5

имеется межтетрадный перенос из данной тетрады р сумматоре 5, и с кодом 1010, если межтетрадный перенос из данной тетрады сумматора 5 отсутствует,, Операция вычитания избытка шесть заменена на сложение с его дополнением (1010). Смешанный код результата, полученного на выходе сумматора 6, корректируется в двоично- десятичный код с избытком шесть сумматором 8 коррекции. Для этого каждая тетрада сумматора 8 коррекции суммируется с двоичным кодом 0000, если межтетрадный перенос из данной тетрады сумматора 6 отсутствует, и с кодом ОНО, если имеется межтетрадный перенос из данной тетрады сумматора 6.

Естественный двоично-десятичный код с выходов сумматора 7 коррекции и двоично-десятичный код с избытком шесть с выходов сумматора 8 коррекции поступают на входы первого и второго слагаемых сумматора 9 второй ступени. Код, полученный на выходах сумматора 9, корректируется в естественньй двоично-десятичный код сумматором 10 коррекции. Для этого каждая тетрада сумматора 10 коррекции суммируется с кодом 0000, если имеется межтетрадный перенос из данной тетрады сумматора 9, и с двоичным кодом 1010, если указанный перенос отсутствует.

В зависимости от значения старшего разряда входного числа, поступившего на первые входы блоков ПЗУ 1-4, выбирается область памяти, соответствующая положительному или отрицательному входному числу. Содержимое для ячеек памяти как для положительных, так и для отрицательных двоичных чисел представляет собой положительные десятичные эквиваленты, так как десятичные числа должны быть представлены в прямом коде.

Знак входного числа может передаваться на выход преобразователя в виде четвертого разряда тетрады знака, первый и третий разряды тетрады знака и второй разряд тетрады знака соединены (для кода КОИ-8) соответственно с входами логической Г1 и О, преобразователя.

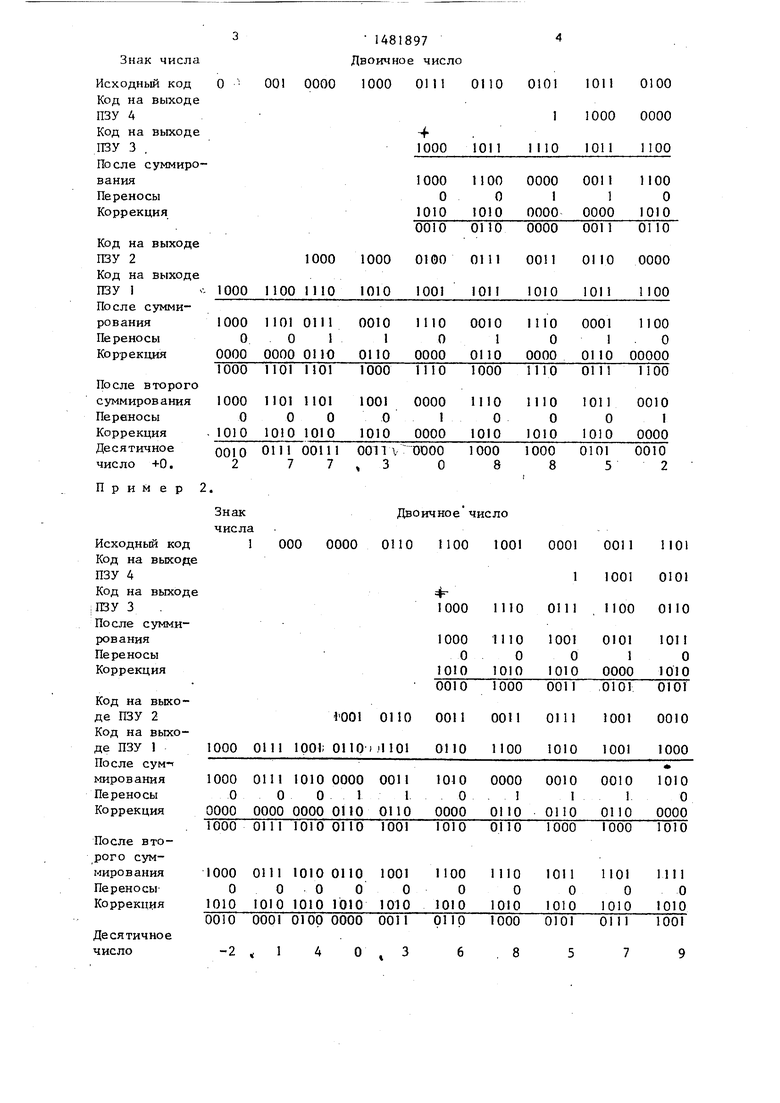

Примеры преобразователя двоичных чисел в двоично-десятичные. Пример 1.

Пример 2.

5148

Формула изобретения

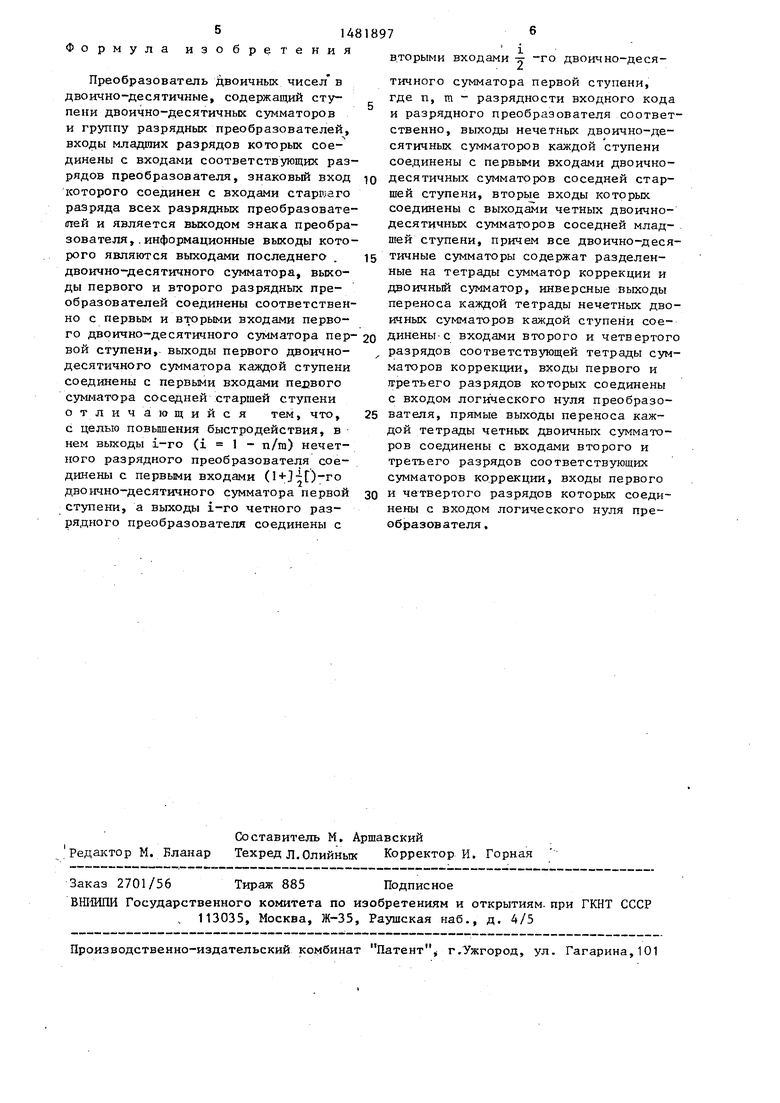

Преобразователь двоичных чисел в двоично-десятичные, содержащий ступени двоично-десятичных сумматоров и группу разрядных преобразователей, входы младших разрядов которых соединены с входами соответствующих разрядов преобразователя, знаковый вход которого соединен с входами стар&аго разряда всех разрядных преобразователей и является выходом знака преобразователя, .информационные выходы которого являются выходами последнего двоично-десятичного сумматора, выходы первого и второго разрядных преобразователей соединены соответственно с первым и вторыми входами первого двоично-десятичного сумматора первой ступени, выходы первого двоично- десятичного сумматора каждой ступени соединены с первыми входами первого сумматора соседней старшей ступени отличающийся тем, что, с целью повышения быстродействия, в нем выходы 1-го (1 1- n/tn) нечетного разрядного преобразователя соединены с первыми входами ( двоично-десятичного сумматора первой ступени, а выходы 1-го четного разрядного преобразователя соединены с

897b

i

вторыми входами - -го двоично-десятичного сумматора первой ступени, где n, m - разрядности входного кода и разрядного преобразователя соответственно, выходы нечетных двоично-десятичных сумматоров каждой ступени соединены с первыми входами двоичнодесятичных сумматоров соседней старшей ступени, вторые входы которых соединены с выходами четных двоично- десятичных сумматоров соседней младшей ступени, причем все двоично-деся5 тичные сумматоры содержат разделенные на тетрады сумматор коррекции и двоичный сумматор, инверсные выходы переноса каждой тетрады нечетных двоичных сумматоров каждой ступени соео динены с входами второго и четвертого разрядов соответствующей тетрады сумматоров коррекции, входы первого и тгретьего разрядов которых соединены с входом логического нуля преобразо5 вателя, прямые выходы переноса каждой тетрады четных двоичных сумматоров соединены с входами второго и третьего разрядов соответствующих сумматоров коррекции, входы первого

0 и четвертого разрядов которых соединены с входом логического нуля преобразователя.

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU960794A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США N 3882483, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1989-05-23—Публикация

1987-06-08—Подача