Cpi.fl

Изобретение относится к электросвязи и может быть использовано для фазирования приемного устройства систем передачи данных с псевдослучайными сигналами.

Целью изобретения является обеспечение фазирования псевдослучайных последовательностей с кратными и некратными периодами следования.

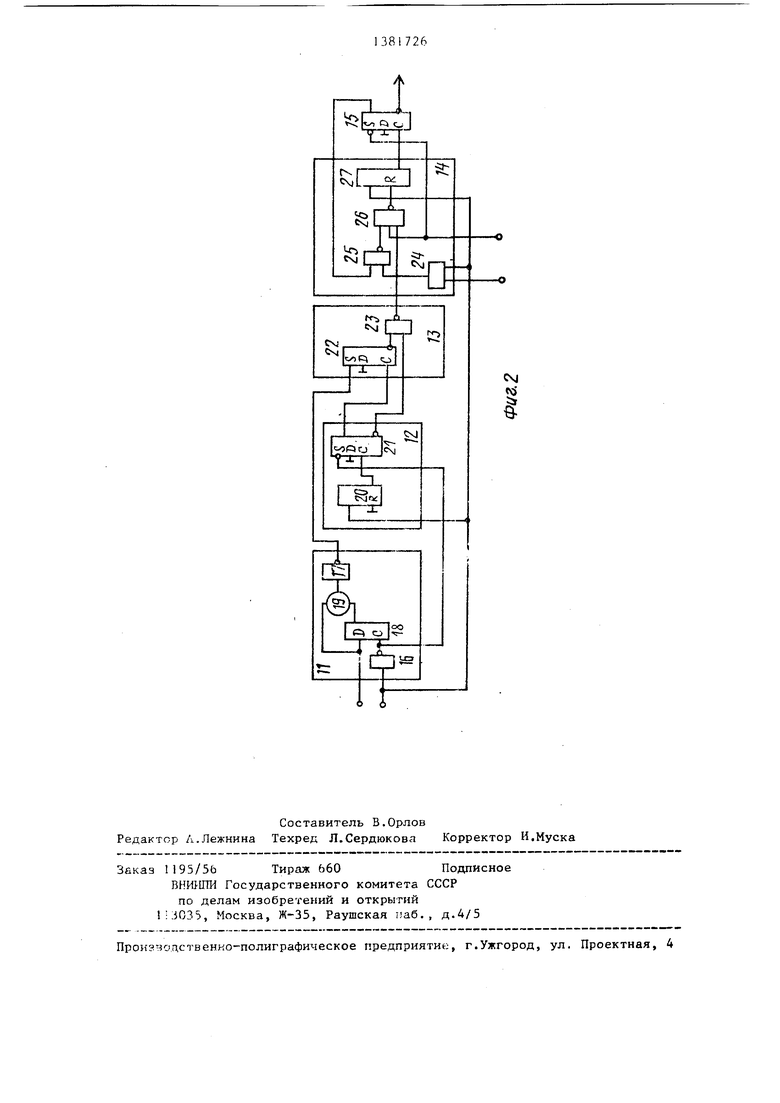

На фиг.1 представлена схема устройства фазирования псевдослучайных последовательностей; на фиг.2 - схема управляющего блока.

Устройство фазирования псевдослучайных последовательностей содержит N каналов 1 обработки псевдослучайных последовательностей, блок 2 сумматоров по модулю два и N-1 блоков 3 обработки псевдослучайных последовательностей.

Каждый из N каналов 1 обработки псевдослучайных последовательностей содержит ключ 4, регистр 5 сдвига с логическими обратными связями, суммтор 6 по модулю два и управляющий блок 7.

Блок 2 сумматоров по модулю два содержит N-1 сумматоров 8 по модулю два.

Кажд.ьй из N-I блоков 3 обработки псевдослучайных аоследовательностей содержит элемент И 9и линию 10 задержки.

Управляющий блок 7 содержит фор- мироватапь 11 фронтов, формирователь 12 меток времени, анализатор 13 входного сигнала, счетчик 14 импульсов и триггер 15 фазирования.

Формирователь 11 фронтов содержи первый и второй инверторы 16 и 17, D-триггер- 18 и сумматор 19 по модулю два.

Формирователь 12 меток времени сдержит делитель 20 частоты и D-триггер 21.

Анализатор 13 входного сигнала содержит D-триггер 22 и элемент И 23.

Счетчик I4 импульсов содержит первый, второй и третий элементы И 24-26 и делитель 27 частоты.

Устройство фазирования псевдослучайных последовательностей (ПСП) работает следующим образом.

На дополнительный вход блока 2 сумматоров, являющийся входом устроства фазирования псевдослучайных последовательностей, подается входной сигнал в виде N сложенных по модулю два ПСП. Этот сигнал без изменения проходит через N-1 сумматоров

8 блока 2 сумматоров, так как на его входы поступают сигналы О. С выхода блока 2 сумматоров сигнал поступает на вход N-ro канала i обработки, в котором на сумматоре 6 осуществляется вычитание из N ПСП, сложенных, по модулю два, N-й ПСП.

С первого выхода N-ro канала 1 обработки сигнал поступает на N-1-й канал 1 обработки, где осуществляется аналогичная операция. После обработки в N-1 каналах 1 обработки на вход первого канала 1 обработки поступает первая ПСП, которая через ключ 4 и регистр 5 подается на сумматор 6. Регистр 5 и сумматор 6 образуют узел проверки на соответствие

закону формирования ПСП.

Если поступающая на второй вход с сумматора 6 ПСП соответствует закону

формирования, то на выходе сумматора 6 будут отсутствовать сигналы ошибки. Отсутствие сигналов ошибки на выходе сумматора 6 регистрируется управляющим блоком 7, Если в течение )зремени, определи Змого емкостью счетчика 14 управг.якп,его блока 7, ня пятый вход (Сброс счетчика 14 не поступают сигналы глаибки, то счетчик 14 формирует импульо, который

запоминается в триггн1.)о. 15.

I

Сигнал 1 с прямого выхода триггера 15 поступает на ключ 4, в результате чего на вход регистра 5

начинает поступать информация с выхода логической сvpHuaTenbHof i связи регистра 5, которой ггяляегск су ;матор по модулю два. Т егистр 5 начинает работать в режш- е формирорания ПСП,

синфазной ПСП, поступающей на второй вход сумматора 6. Так как на второй вход сумматора 6 первая ПСП поступила сдвинутой по относительно этой же ПСП, поступаю мей на дополнительный вход блока 2 сумматоров, то для искличеи 5Я фазового сдвлга с регистра 5 и с; выхода с мматора 6 на линию 10 задержки поступает ряд сдви- нуты} по фазе ПСП.

.Цополнительньш фазовый сдьиг в линии 10 задержки обеспечивает получение на выходе линии 10 задержки нулевого сдвига, т.е. первая ПСП на выходе линии 10 задержки будет син-

фаз}1а первой ПСП на дополнительном входе блока 2 сумматоров.

С выхода /шнии 10 задержки первая ПСП через открытый элемент И 9 поступает на соответствую11р1й вход блока 2 сумматоров, в котором осуществляется вычитание из N сложенных по модулю два ПСП первой ПСП. Аналогично последовательно начинают работать и другие каналы 1 обработки и на соответствующих N-1 сумматорах 8 обеспечивается последовательное вычи raHTie всех ПСП, кроме N-й. Поэтому на вход N-ro канала 1 обработки пос тупает только N-я ПСП, которая фазируется аналогично остальным. Сигналы, поступающие с вторых выходов соответствующих N каналов 1 обработки, индицируют о фазировании соответст- вующих ПСП.

Управляющий блок 7 работает следующим образом.

При наличии информации на выходе D-триггера 8 формируются задержан- ные на один такт импульсы и на выходе сумматора 19 формируются одиночные положительные импульсы длительностью в один такт, которые через второй инвертор 17 устанавливают в состояние 1 П-трИ1тер 22, на инверсном выходе которого формируется сигнал О, закрывающий элемент И 23

При отсутствии сигнала ошибки делитель 27 не сбрасьшается и через определенное количество тактов, определяемое емкостью делителя 27, па его выходе формируется сигнал 1 поступающий на С-вход триггера 15. Сигналом с прямого выхода триггера 15 закрьтается второй элемент И 25, а на инверсном выходе триггера 15 формируется выходкой сигнал о наличии фазирования.

При наличии овшбок (до момента . фазирования) они поступают через второй и третий элементы И 25 и 26 на сброс делителя 27 и сигнал фазирования не формируется.

При отсутствии входной информации 1;мпульсы на выходе второго инвертора 17 не поступают на вход D-триггера 22, который очередной меткой времени с D-триггера 21 устанавливается в состояние О, открывая элемент 11 23, через который сигнал метки вре- мени поступает на сброс делителя 27, и сигнал фазирования не формируется.

JQ 5 0

5 O

Q

5

5

0

5

Таким образом, сигнал фазирования формируется при наличии входной информации и отсутствии на информационном входе управляющего блока 7 сигнала ошибок.

Формула изобретения

1.Устройство фазирования псевдослучайных последовательностей, содержащее N последовательно соединенных каналов обработки псевдослучайных последовательностей, каждый из которых включает последовательно соединенные ключ, регистр сдвига с логическими обратными связями, сумматор по модулю два и управляющий блок, выход которого подсоединен к управляющему входу ключа, первый информатдионный вход ключа подключен к выходу регистра сдвига с логическими обратными связями, а второй вход и выход сумматора по модулю два и выход управляющего блока являются соответственно входом и первым и вторым выходами канала обработки псевдослучайных последовательностей, отличающееся тем, что, г целью ,обеспечения фазирования псевдослучайных последовательностей с кратными и текратными периодами следования, в него введены блок сумматоров по модулю два и N-I блоков обработки псевдослучайных последовательностей, при этом первый и второй входы N-1 блоков обработки псевдослучайных последовательностей под- к.тючены соответственно к второму и дополнительному входам соответствующих N-1 каналов обработ1си псевдослучайных последовательностей, выходы блоков обработки псевдослучайных последовательностей подсоединены к соответствующим входам блока сумматоров по модулю два, выход которого подсоединен к входу N-ro канала обработки псевдослучайных последовательностей, причем дополнительный вход блока сумматоров по модулю два является входом устройства, а блок сумматоров по модулю два содержит N-1 последовательно соединенных сумматоров по модулю два, первый вход первого сумматора по модулю два и вторые входы других сумматоров по модулю два являются входами блока сумматоров по модулю два, второй вход первого сумматора по модулю два

51

и выход (N-l)-ro сумматора по модулю два являются соответственно дополнительным входом и выходом сумматора по модулю два, а каждый из N-1 блоков обработки псевдослучайных последовательностей содержит последовательно соединенные линию задержки и элемент И, второй вход которого вход линии задержки и выход элемента И являются соответственно первым и вторым входами и выходом каждого из N-1 блоков обработки псевдослучайных последовательностей, цри этом в каждом из N каналов обработки псевдо- случайных последовательностей второй информационный вход ключа и информационный вход управляющего блока объединены с вторым входом сумматора по модулю два, а вход Ошибка и вход Сброс управляющего блока и дополнительный выход регистра сдвига с логическими обратными связями являются соответственно первым и вторым дополнительными входами и дополни- тельным выходом каждого из N-1 каналов обработки псевдослучайных последовательностей .

2. Устройство по п.1, о т л и - чающееся тем, что управляю- щий блок содержит последовательно соединенные формирователь фронтов.

ангипизатор входного сигнала, счетчик импульсов и триггер фазирования, а также формирователь меток времени, первый вход и первый и второй выходы которого подключены соответственно к второму выходу формирователя фрон тов и второму и третьему входам анализатора входного сигнала, второй вход счетчика импульсов подключен к прямому выходу триггера фазирования, причем первый вход формирователя фронтов, второй вход формирователя фронтов, объединенный с вторым входом формирователя меток времени и третьим входом счетчика импульсов, четвертый вход счетчика импульсов, пятый вход счетчика импульсов, объе0 5

о

5

0

5

ответственно информационным и тактовым входами, входом Ошибка, входом Сброс и выходом управляющего блока.

3.Устройство по п.2, отличающееся тем, что формирователь фронтов содержит последовательно соединенные первый инвертор, D-триггер, сумматор по модулю два, второй вход которого подключен к D-входу D-триггера, и второй инвертор, причем D-вход D-триггера, вход и выход первого инвертора и выход. второго инвертора являются соответственно первым и вторым входами и вторым и первым выходами формирователя фронтов.

4.Устройство по п.2, отличающееся тем, что формирователь меток времени содержит последовательно соединенные делитель частоты и D-триггер, причем вход делителя частоты, S-вход,прямой и обратный выходы D-триггера являются соответственно вторым и первым входами и первыми вторым выходами формирователя меток времени.

5.Устройство по п.2,

отличающееся тем, что анализатор входного сигнала содержит последовательно соединенные D-триггер и элемент И, причем S-вход и С-вход D-триггера и выход элемента И являются соответственно первым и вторым входами и выходом анализатора входного сигнала.

6. Устройство по п.2, отличающееся тем, что счетчик импульсов содержит последовательно соединенные первый, второй и третий элементы И и делитель частоты, причем первый вход первого элемента И, объединенный с тактовым входом делителя частоты, второй вход первого элемента И, первый вход второго элемента И, второй и третий входы тргтъ- его элемента И и выход делителя частоты являются соответственно третьим,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля дуплексного канала связи | 1983 |

|

SU1231621A2 |

| Устройство для контроля дискретного канала | 1984 |

|

SU1298930A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Система телемеханики | 1986 |

|

SU1363282A1 |

| СПОСОБ ПАКЕТНОЙ ПЕРЕДАЧИ ДАННЫХ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 2021 |

|

RU2769378C1 |

| СПОСОБ ПАКЕТНОЙ ПЕРЕДАЧИ ДАННЫХ ШУМОПОДОБНЫМИ ФАЗОМАНИПУЛИРОВАННЫМИ СИГНАЛАМИ | 2023 |

|

RU2801875C1 |

| Устройство для контроля дуплексного канала связи | 1982 |

|

SU1061280A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

Изобретение относится к электросвязи и обеспечивает фазирование псевдослучайных последовательностей с кратными и некратными периодами следования. Устр-во содержит N каналов обработки (КО) 1 псевдослучайных последовательностей, блок 2 сумматоров по модулю два, (N-1) блоков обработки (БО) 3 псевдослучайных последовательностей. Каждый из N КО 1 содержит ключ 4, регистр 5 сдвига с логич. обратными связями, сумматор 6 по модулю два и управляющий блок 7. Блок 2 содержит (N-1) сумматоров 8 по модулю два. Каждый из (N-1) БО 3 содержит эл-т И 9 и линию 10 задержки. Блок 7 содержит формирователь (Ф) фронтов, Ф меток времени, анализатор входного сигнала, счетчик импульсов и триггер фазирования. Ф фронтов содержит два инвертора, D-триггер и сумматор по модулю два. Ф меток времени содержит делитель частоты и D-триггер. Анализатор содержит D- триггер и зл-т И. Счетчик импульсов содержит три зл-та И и делитель час- тоты. 5 з.п.ф-лы, 2 ил. i С/)

динениый с S-входом триггера фазиро- сп четвертым, вторым, первым и пятым вания, и инверсный выход являются со- входами и выходом счетчика импульсов,

..,tr

Eil3

CVJ

&

| УСТРОЙСТВО ФАЗИРОВАНИЯ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 0 |

|

SU392602A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство фазирования псевдослучайных последовательностей | 1974 |

|

SU657637A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-15—Публикация

1986-04-04—Подача