(54) НОСИТЕЛЬ С СИСТЕМОЙ ВЫВОДОВ ДЛЯ МОНТАЖА ИНТЕГРАЛЬНЫХ СХЕМ

I

Изобретение относится к микроэлектронике, в частности к конструированию носителей с системой выводов для монтажа интегральных схем.

Известен носитель с системой выводов, выполненный в виДе проводников-выводов, расположенных на полимерном Материале (пластик типа Kapton), причем внутренние, более узкие концы выводов, соответствуют расположению контактных площадок на кристалле, а внешние, более широкие,расположению выводов меткой выводной рамни 13.

Недостатком таких, .носителей с системой выводов является сложность их изготовления или необходимость 0 применении эысокотоксичных веществ (гидразингидрата) для травления полиимидного диэлектрика.

Наиболее близкой к изобретению является конструкция носителя с системой выводов для монтажа интегральных схем, содержащего диэлектрическое основание из полимерного диэлектрика с пониженной степенью полимеризации, типа ФДИ-АП, с расположенными на нем печатными проводниками. Техпроцесс изготовления носителя с системой выводов известной конструкции сравнительно несложен. Кроме того, применение диэлектрика с пониженной степенью имидизации позволило использовать при травлении полиимида малотоксичный травитель - моноэталонамин t2j|.

Однако в процессе изготовления носителя с системой выводов наблюдаются усадочные явления, приводящие к

15 уходу габаритно-присоединительных размеров, следствием чего является рассовмещение проводников-выводов с контактными площадками полупроводникового кристалла, печатной платы

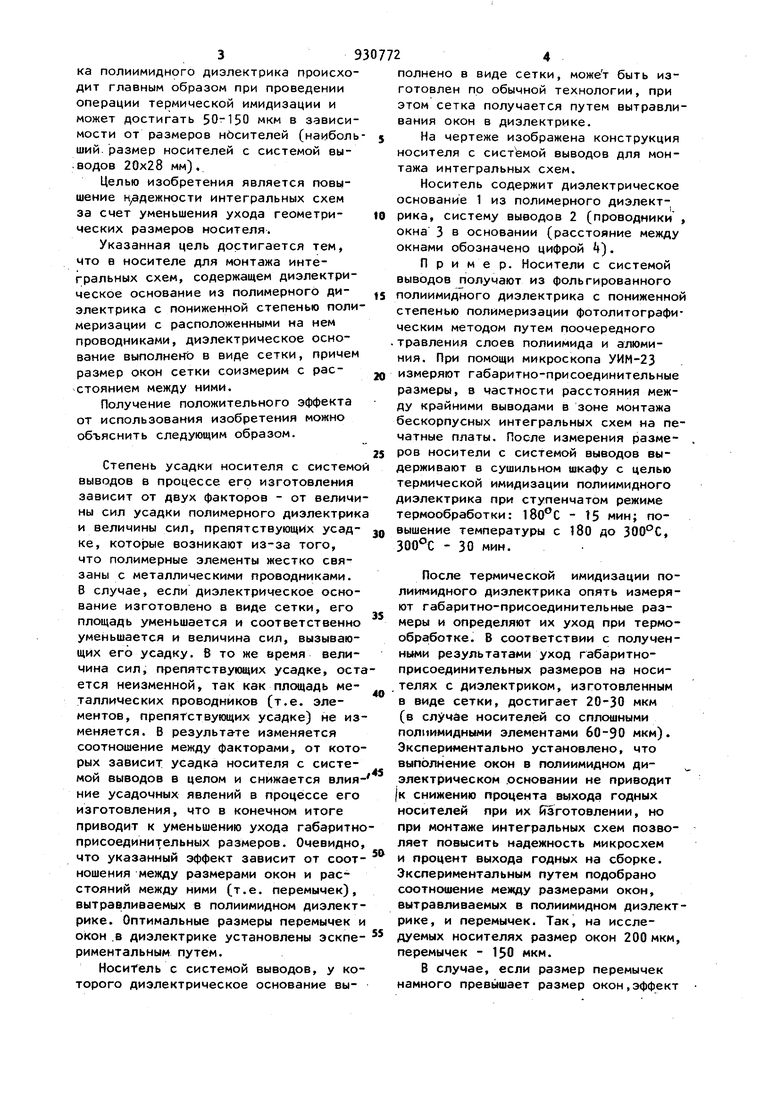

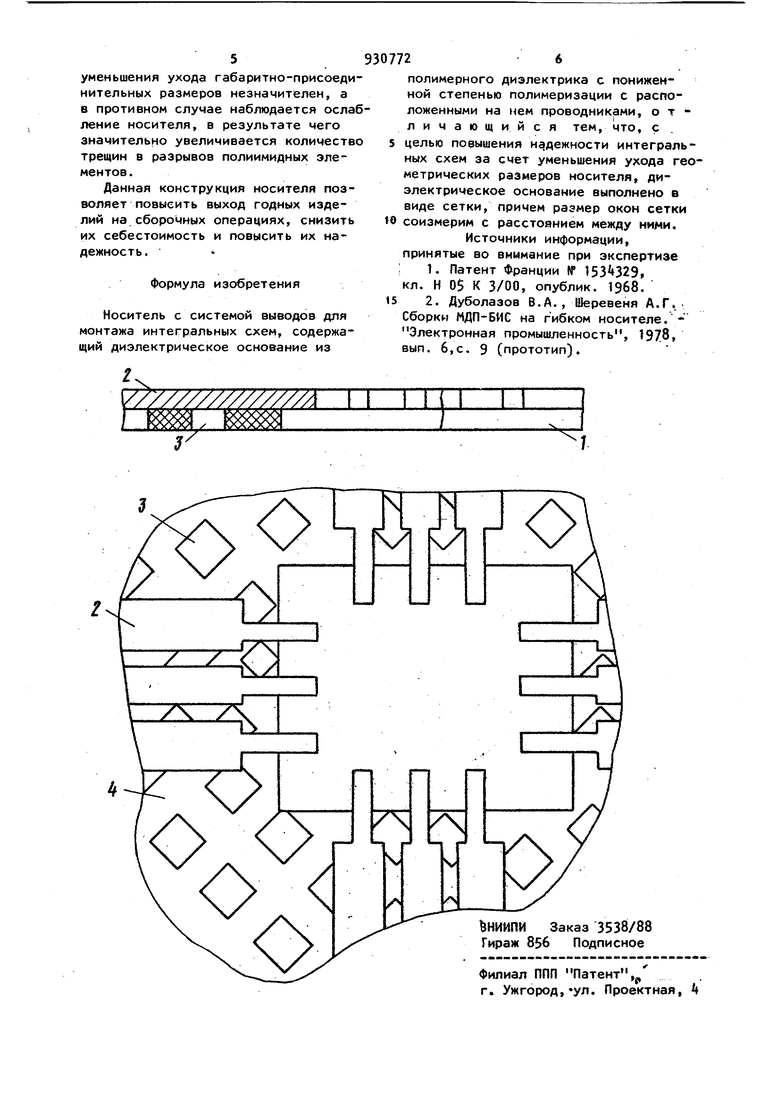

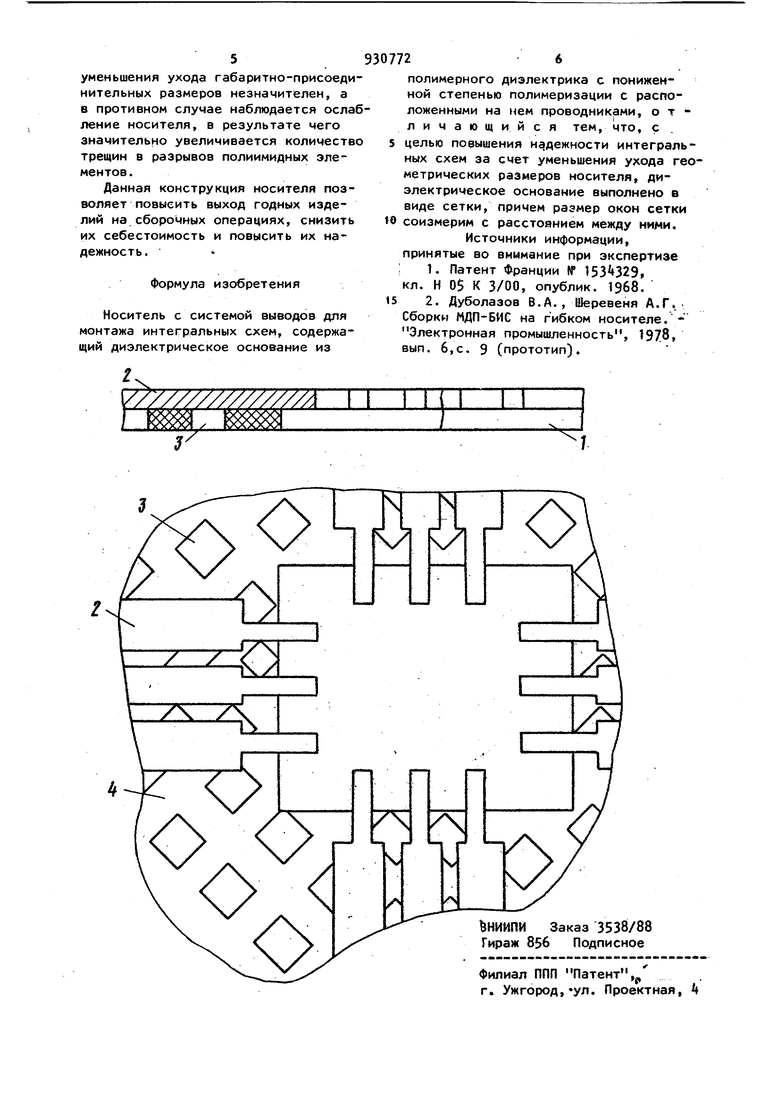

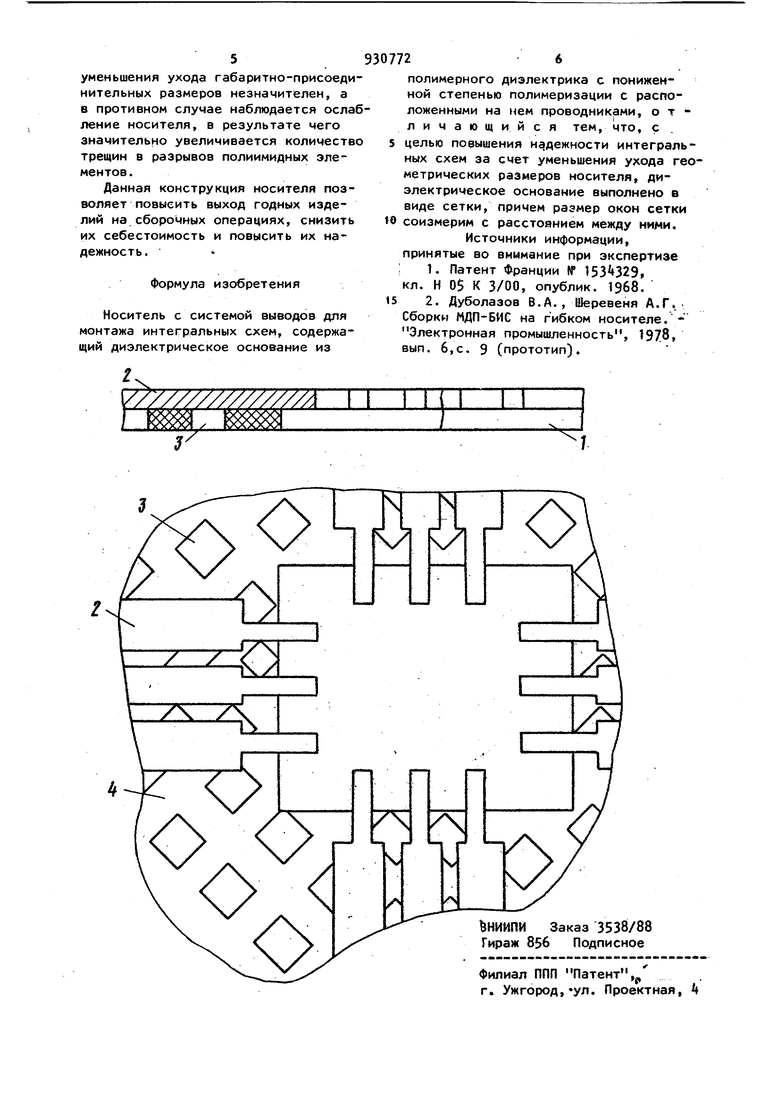

20 или жесткими выводами рамок. В результате при монтаже интегральных схем это приводит к браку и снижению процента выхода годных изделий. Усадка полиимидного диэлектрика происходит главным образом при проведении операции термической имидиэации и может достигать 50-150 мкм в зависимости от размеров нйсителей (наибольший.размер носителей с системой выводов 20x28 мм). Целью изобретения является повышение н,адежности интегральных схем за счет уменьшения ухода геометрических размеров носителя. Указанная цель достигается тем, что в носителе для монтажа интегральных схем, содержащем диэлектрическое основание из полимерного диэлектрика с пониженной степенью полимеризации с расположенными на нем проводниками, диэлектрическое основание выполнено в виде сетки, причем размер окон сетки соизмерим с расстоянием между ними. Получение положительного эффекта от использования изобретения можно объяснить следующим образом. Степень усадки носителя с системо выводов в процессе его изготовления зависит от двух факторов - от величи ны сил усадки полимерного диэлектрик и величины сил, препятствующих усадке, которые возникают из-за того, что полимерные элементы жестко связаны с металлическими проводниками. В случае, если диэлектрическое основание изготовлено в виде сетки, его площадь уменьшается и соответственно уменьшается и величина сил, вызывающих его усадку. 8 то же время величина сил, препятствующих усадке, ост ется неизменной, так как площадь металлических проводников (т.е. элементов, препятствующих усадке) не из меняется. В результате изменяется соотношение между факторами, от кото рых зависит усадка носителя с системой выводов в целом и снижается влия ние усадочных явлений в процессе его изготовления, что в конечном итоге приводит к уменьшению ухода габаритн присоединит ельных размеров. Очевидно что указанный эффект зависит от соот ношения между размерами окон и расстояний между ними (т.е. перемычек), вытравливаемых в полиимидном диэлект рике. Оптимальные размеры перемычек окон .8 диэлектрике установлены эскпе риментальным путем. Носитель с системой выводов, у ко торого диэлектрическое основание выполнено в виде сетки, может быть изготовлен по обычной технологии, при этом сетка получается путем вытравливания окон в диэлектрике. На чертеже изображена конструкция носителя с системой выводов для монтажа интегральных схем. Носитель содержит диэлектрическое основание 1 из полимерного диэлектрика, систему выводов 2 (проводники , окна 3 в основании (расстояние между окнами обозначено цифрой kj. Пример. Носители с системой выводов получают из фольгированного полиимидного диэлектрика с пониженной степенью полимеризации фотолитографическим методом путем поочередного травления слоев полиимида и алюминия. При помощи микроскопа УИМ-23 измеряют габаритно-присоединительные размеры, в частности расстояния между крайними выводами в зоне монтажа бескорпусных интегральных схем на печатные платы. После измерения разме- . ров носители с системой выводов выдерживают в сушильном шкафу с целью термической имидизации полиимидного диэлектрика при ступенчатом режиме термообработки: 180°C - 15 мин; повышение температуры с 180 до , 300°С - 30 мин. После термической имидизации полиимидного диэлектрика опять измеряют габаритно-присоединительные размеры и определяют их уход при термообработке. В соответствии с полученньн«1и результатами уход габаритноприсоединительных размеров на носителях с диэлектриком, изготовленным в виде сетки, достигает 20-30 мкм (в случае носителей со сплошными полиамидными элементами 60-90 мкм). Экспериментально установлено, что выполнение окон в полиимидном диэлектрическом .основании не приводит JK снижению процента выхода годных носителей при их изготовлении, но при монтаже интегральных схем позволяет повысить надежность микросхем и процент выхода годных на сборке. Экспериментальным путем подобрано соотношение между размерами окон, вытравливаемых в полиимидном диэлектрике, и перемычек. Так, на исследуемых носителях размер окон 200 мкм, перемычек - 150 мкм. В случае, если размер перемычек намного превышает размер окон,эффект

уменьшения ухода габаритно-присоединительных размеров незначителен, а в противном случае наблюдается ослабление носителя, в результате чего значительно увеличивается количество трещин в разрывов полиимидных элементов.

Данная конструкция носителя позволяет повысить выход годных изделий на сборочных операциях, снизить их себестоимость и повысить их надежность .

Формула изобретения

Носитель с системой выводов для монтажа интегральных схем, содержащий диэлектрическое основание из

полимерного диэлектрика с пониженной степенью полимеризации с расположенными на нем проводниками, отличающийся тем, что, с 5 целью повышения надежности интегральных схем за счет уменьшения ухода геметрических размеров носителя, диэлектрическое основание выполнено в виде сетки, причем размер окон сетки to соизмерим с расстоянием между ними.

Источники информации, принятые во внимание при экспертизе I 1. Патент Франции ff , кл. Н 05 К 3/00, опублик. 1968. 15 2. Дуболазов В.А., Шеревеня А.Г. Сборки МДП-БИС на гибком носителе. Электронная промышленность, 1978, вып. 6,с. 9 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ сборки интегральных схем | 1990 |

|

SU1781733A1 |

| Способ формирования контактных окон в слое защитного основания высоковольтного прибора | 2016 |

|

RU2645920C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНЫХ МНОГОУРОВНЕВЫХ ПЛАТ ДЛЯ МНОГОКРИСТАЛЬНЫХ МОДУЛЕЙ, ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ И МИКРОСБОРОК | 2011 |

|

RU2459314C1 |

| СПОСОБ ПОЛУЧЕНИЯ ГИБКОГО ЛАКОФАЛЬГОВОГО ПОЛИИМИДНОГО МАТЕРИАЛА | 2003 |

|

RU2240921C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2004 |

|

RU2264676C1 |

| ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2011 |

|

RU2478240C1 |

| МОНТАЖНАЯ ПЛАТА С ЭЛЕКТРИЧЕСКИМИ И ОПТИЧЕСКИМИ МЕЖСОЕДИНЕНИЯМИ И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ | 2012 |

|

RU2577669C2 |

| БЕСКОРПУСНАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1990 |

|

RU2068601C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНОЙ СХЕМЫ | 1990 |

|

RU2023329C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ РАДИОЭЛЕКТРОННЫХ УЗЛОВ | 2014 |

|

RU2575641C2 |

///////////////// т

Jи.

Авторы

Даты

1982-05-23—Публикация

1980-11-21—Подача