Изобретение относится к вычислительной технике и может быть использовано для контроля логических микросхем средней и большой степени интеграции.

Цель изобретения - повьпяение производительности контроля.

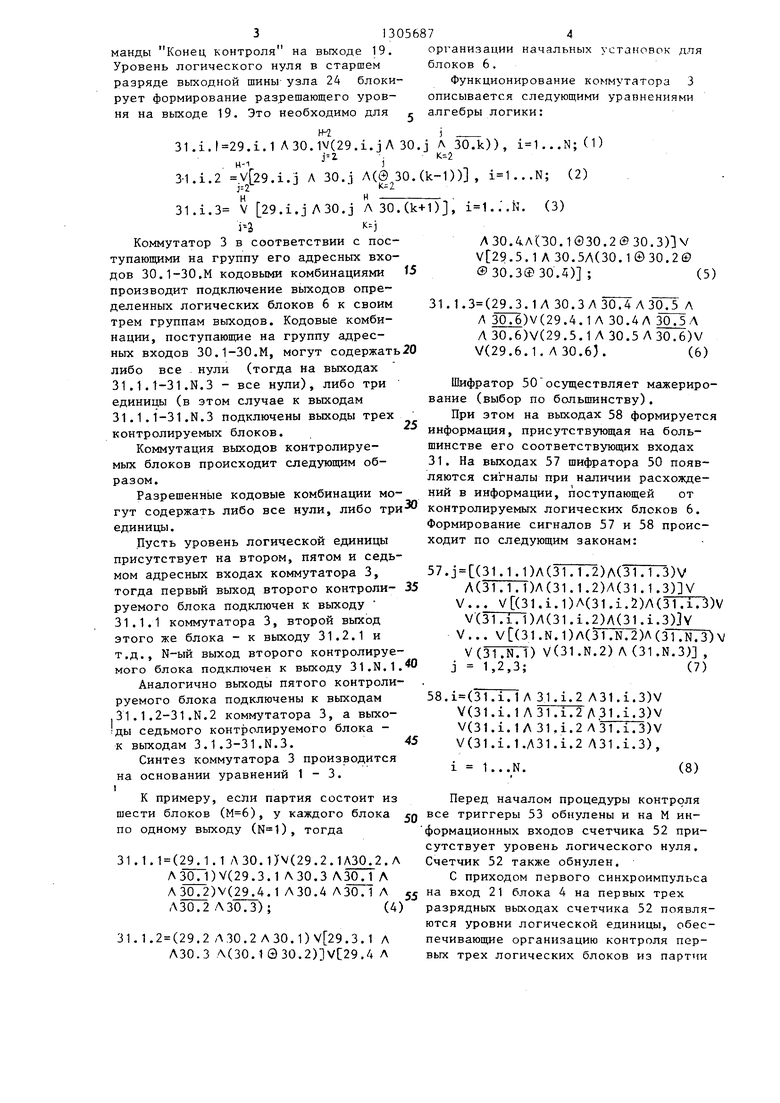

На фиг, 1 показана схема устройства; на фиг, 2 - блок управления; на фиг. 3 - генератор тестов; на фиг. 4 - коммутатор; на фиг. 5 - схема реализации коммутатора; на фиг.6- схема мажоритарного блока; на фиг.7 - схема анализатора сигнатур.

Устройство содержит блок 1 управления, генератор 2 тестов, коммутатор 3, мажоритарный блок 4 анализатор 5 сигнатур, контролируемые логические блоки 6.

,-25

вая элемент И 14 для пропуска синхроимпульсов на вход 20 к генератору 2.

При поступлении сигнала Канал контроля на вход 19 триггер 9 блоки рует работу генератора 12, а триггеры 10 и 11 обнуляются, и на выходе 22 формируется блокирующий сигнал

Блок управления содержит элементы 20 ня по входу 17 от блока 4 триггер 10 ИЛИ 7 и 8, триггеры 9-11, генератор устанавливается в единичное состоя- 12 синхроимпульсов, элемент НЕ 13, ние, закрывая элемент И 15 и откры- элементы И 14 и 15, вход 16 пуска, вход 17 разрешения, вход .18 начала контроля, вход 19 конца контроля,син хровыход 20, выход 21 задания режима работы, выход 22 блокировки.

Генератор тестов содержит узел 23 считывания, узел 24 памяти, буферный регистр 25, узел 26 контроля по -30 низкого уровня.

четности и элемент И 27, выходы гене- При поступлении синхроимпульса на Оратора 28.вход 20 узел 23 формирует адрес узла

,24 памяти и сигнал записи в буферный

Коммутатор представляет собой ком- регистр 25. С шины 24 параллельный. бинационную схему, имеющую N.M инфор- 35 код переписывается в регистр 25 по мационных входов 29.1.1-29.1.N, команде записи.

29.М.1-29.M.N (N - число контролиру- узел 26 контроля по четности фор- емых выходов одного логического блока мирует разрешающий уровень при сов- (), М - количество контролируе- падении выходов узла 24 памяти и ре- мых логических блоков в партии), М 40 гистра 25. При несовпадении выходов адресных входов 30.1-30.М, группу вы- .ходов коммутатора 31.1.1-31.1.3 - 31.N.1-31.N.3.

Коммутатор содержит элементы НЕ

узел 26 контроля по четности формирует запрещающий уровень, узел 23 блокируется на текущем адресе и по следующему синхроимпульсу по входу 20

узел 26 контроля по четности формиру ет запрещающий уровень, узел 23 бло кируется на текущем адресе и по сле дующему синхроимпульсу по входу 20

32, элементы И 33 - 37, элементы РАВ- 5 производится повторная запись в реНОЗНАЧНОСТЬ 38, элементы ИЛИ 39 - 41, выходы 42 - 49 внутренних ярусов коммутатора „

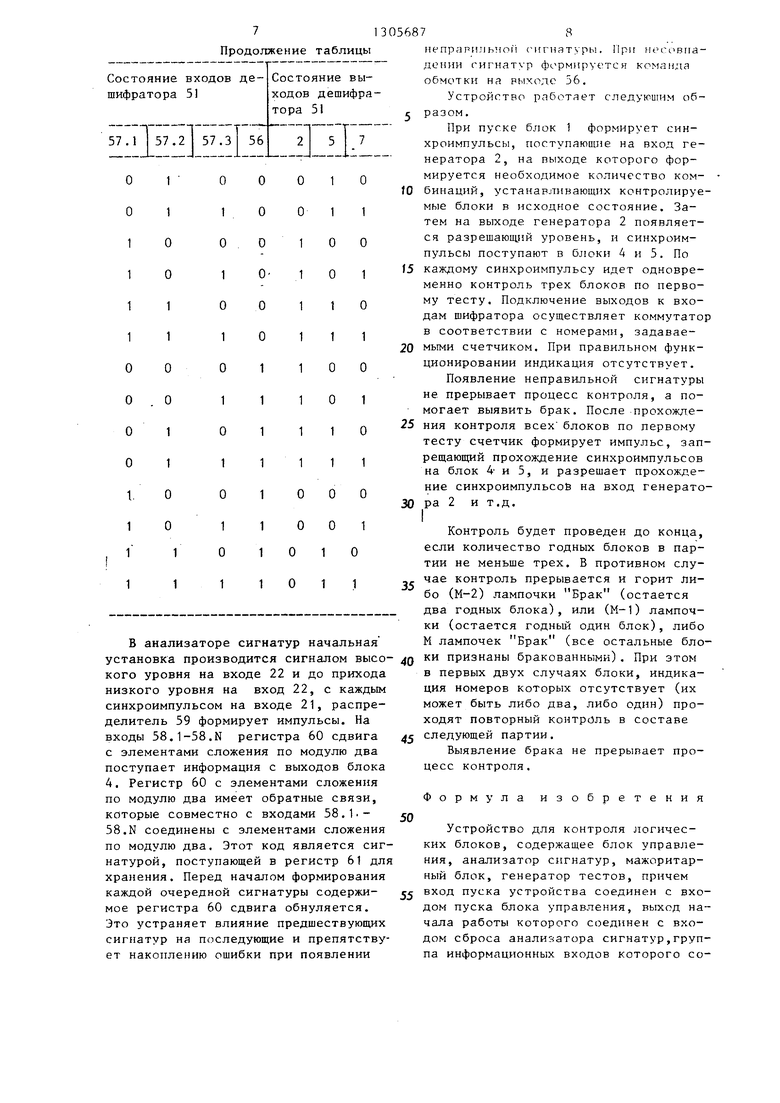

Мажоритарный блок содержит шифратор 50, дешифратор 51, счетчик 52, группу триггеров 53, узел 54 индикации, выходы 55 узла индикации, вход 56 разрешения, группы входов 57 и 58 шифратора.

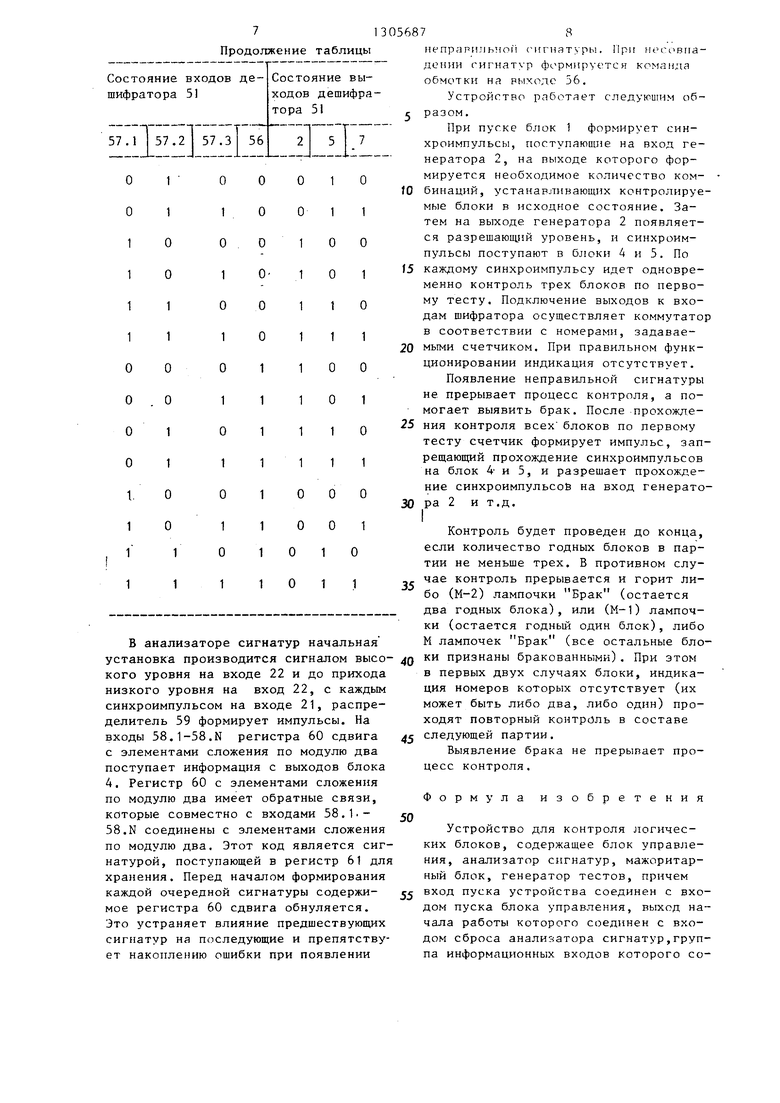

Анализатор сигнатур содержит распределитель 59 импульсов регистр 60 с сумматорами по модулю два, регистр 61 памяти, узел 62 сравнения, узел 63 памяти.

гистр 25. Этим же уровнем блокируется формирование разрешающего уровня на выходе 8 элемента И 27 .

50

Разрядность используемой двойной комбинации на выходной шине зависит от количества входов контролируемых логических блоков 6, Два старших ра 55 ряда выходной шины узла 24 выполняю следующие функции. При считывании по ледней тестовой комбинации появлени уровня логиче ского нуля в предпослед нем разряде соответствует выдаче ко

При подаче разрешающего уровня на вход 16 триггеры 9 и 10 устанавливаются в единичное состояние. При этом происходит запуск генератора 12, а через открытый элемент И 14 синхроимпульсы поступают на вход 20 к генератору 2.

При поступлении разрешающего уровня по входу 18 от генератора 2 тестов триггер 11 формирует сигнал выского уровня на выходе 22. Одновременно триггер 10 устанавливается в нулевое состояние, запрещая тем самым прохождение синхроимпульсов с выхода гене- ратора 12 через открытый элемент И 14 и разрешая прохождение импульсов через элемент И 15 на вход 21 к блоку 4 и анализатору 5.

При поступлении разрешающего уроввая элемент И 14 для пропуска синхроимпульсов на вход 20 к генератору 2.

При поступлении сигнала Канал контроля на вход 19 триггер 9 блоки рует работу генератора 12, а триггеры 10 и 11 обнуляются, и на выходе 22 формируется блокирующий сигнал

ня по входу 17 от блока 4 триггер 10 устанавливается в единичное состоя- ние, закрывая элемент И 15 и откры-

низкого уровня.

узел 26 контроля по четности фор- мирует разрешающий уровень при сов- падении выходов узла 24 памяти и ре- гистра 25. При несовпадении выходов

узел 26 контроля по четности формирует запрещающий уровень, узел 23 блокируется на текущем адресе и по следующему синхроимпульсу по входу 20

производится повторная запись в регистр 25. Этим же уровнем блокируется формирование разрешающего уровня на выходе 8 элемента И 27 .

Разрядность используемой двойной комбинации на выходной шине зависит от количества входов контролируемых логических блоков 6, Два старших раз- ряда выходной шины узла 24 выполняют следующие функции. При считывании последней тестовой комбинации появление уровня логиче ского нуля в предпоследнем разряде соответствует выдаче команды Конец контроля на выходе 19. Уровень логического нуля в старшем разряде выходной шины- узла 24 блокирует формирование разрешающего уровня на вьЕсоде 19. Это необходимо для

н

организации начальных установок для блоков 6.

Функционирование коммутатора 3 описывается следующими уравнениями алгебры логики:

)

(2)

31.1.,1.1 A30.1V(29.i.jA 30.j Л 30.k)), ...N;(1)

. -j

3-1.1.2 .i.j Л 30.j Л(® 30.(k-1)) , ...N; .1.3 V 29.i.jA30.j A30.(k+1), ...N. (3)

15

r-S

Коммутатор 3 в соответствии с поступающими на группу его адресных входов 30.1-ЗО.М кодовыми комбинациями производит подключение выходов определенных логических блоков 6 к своим трем группам выходов. Кодовые комбинации, поступающие на группу адресных входов 30.1-ЗО.М, могут содержать20 либо все нули (тогда на выходах 31.1.1-31.N.3 - все нули), либо три единицы (в этом случае к выходам 31.1.1-31.N.3 подключены выходы трех контролируемых блоков.

Коммутация выходов контролируемых блоков происходит следующим образом.

Разрешенные кодовые комбинации моA30.4A(30.1030.2®30.3)3v .5.1 Л30.5А(30.1©30.2© ® 30.3® 30.4) ;(5)

31.1.3(29.3.1 А 30.3 А30.4 А30.5 Л А 30.6)У(29.4.1А 30.4 А 30.5 А A30.6)V(29.5.1 А30.5 A30.6)V V(29.6.1. А 30.6).(6)

Шифратор 50 осуществляет мажериро- вание (выбор по большинству).

При этом на выходах 58 формируется информация, присутствующая на большинстве его соответствующих входах 31. На выходах 57 шифратора 50 появляются сигналы при наличии расхождений в информации, поступающей от гут содержать либо все нули, либо контролируемых логических блоков 6.

единицы.

Пусть уровень логической единицы присутствует на втором, пятом и седьмом адресных входах коммутатора 3, тогда первьй выход второго контроли- руемого блока подключен к выходу 31.1.1 коммутатора 3, второй выход этого же блока - к выходу 31.2.1 и т.д., N-ый выход второго контролируемого блока подключен к выходу 31.N.1.

Аналогично выходы пятого контролируемого блока подключены к выходам .31.1.2-31.N.2 коммутатора 3, а выхо- ;ды седьмого конт золируемого блока - к выходам 3.1.3-31.N.3.

Синтез коммутатора 3 производится на основании уравнений 1-3.

Перед началом процедуры контроля

К примеру, если партия состоит из

шести блоков (), у каждого блока Q все триггеры 53 обнулены и на М ин- по одному выходу (), тогда формационных входов счетчика 52 присутствует уровень логического нуля. 31 .1.1 (29.1.1 А 30.1)У(29.2.1А30.2.А Счетчик 52 также обнулен.

А 30.1)У(29.3.1 Л 30.3 Л30.1 Л С приходом первого синхроимпульса А30.2)У(29.4.1 А30.4 АЗО. 1 А 55 ° блока 4 на первых трех Д30.2ЛЗО.З);(4) разрядных выходах счетчика 52 появляются уровни логической единицы, обес31.1.2(29.2 А 30.2 Л 30.1) .3.1 А печивающие организацию контроля пер- АЗО.З Л(30.1030.2)3vC29.4 А вых трех логических блоков из партии

организации начальных установок для блоков 6.

Функционирование коммутатора 3 описывается следующими уравнениями алгебры логики:

)

Л

(2)

A30.4A(30.1030.2®30.3)3v .5.1 Л30.5А(30.1©30.2© ® 30.3® 30.4) ;(5)

31.1.3(29.3.1 А 30.3 А30.4 А30.5 Л А 30.6)У(29.4.1А 30.4 А 30.5 А A30.6)V(29.5.1 А30.5 A30.6)V V(29.6.1. А 30.6).(6)

Формирование сигналов 57 и 58 происходит по следующим законам:

57.(31.1.1)A(31.1.2)A(31.1.3)V

А(31.1.1)А(31.1.2)Д(31.1.3)У V... V(3.i.1)A(31.1.2)A(31.i.3)V

V(31.1.l)A(31.i.2)A(31.i.3)3v V... VC(31.N.1)A(31.N.2)A(31.N.3)V V(31.N.1) V(31.N.2) A(31.N.3) ,

j 1,2,3;

(7)

58

.i(31.1.1 A 31.1.2 A31.1.3)V V(31.i.1 A31.i.2 A31.1.3)V V(31.i.1 АЗЫ.2 A31.i.3)V V(31.i.1.A31.i.2 A31.i.3),

1 1...N.

Перед началом процедуры контроля

первой тестовой комбинации. По второму синхроимпульсу на входе 21 логическая единица присутствует на четвертом, пятом и шестом разрядных выходах счетчика, обеспечивая тем са- мым контроль логических блоков 4-6 |В партии по тестовой комбинации. Ана логично производится контроль всех М узлов. Коэффициент пересчета счетчик 52 равен М/3. Следует отметить, что число контролируемых блоков М не обязательно должно быть кратно трем. Б этом случае коэффициент пересчета счетчика 52 округляется до блютайше- го целого в большую сторону, а конт- роль остающегося одного (в данном случае М-го) или двух {(М-1)-го и М- го) блока производится соответственно с двумя или с одним наиболее близким к началу партии годным логичес- КИМ блоком. Так, если , а при контроле первой тестовой комбинации ни один из первых 31 логических блоков не оказывается бракованным, то при поступлении на вход 21 одиннад- цатого синхроимпульса уровни логической единицы устанавливаются на М-м, первом и втором разрядных выходах счетчика 52. Уровень логической единицы на М-м выходе счетчика 52 ука- зывает, что все логические блоки в партии прошли контроль по текущей тестовой комбинации. При этом очередной импульс на входе 21 устанавливает счетчик 52 в нулевое состояние, а на его выходе заема появляется импульс, который означает, что счетчик 52 готов к организации контроля блоков 6 по следующей тестовой комбинации .

Если отдельные блоки бракованы, соответствующие триггеры 53 устанавливаются в единичное состояние, что приводит к появлению на соответствую- щих установочных входах счетчика 52 уровней логической единицы. Тем самым логические блоки, признанные бра- кованнь ми, из дальнейшего контроля исключаются, т.е. на всех последующих тестовых комбинациях на выходах счетчика 52, соответствующих бракованным блокам, уровень логической единицы формироваться не будет.

Так, если при контроле по первой тестовой комбинации второй и пятый логические блоки оказываются бракованными, то при контроле по второй тестовой комбинации счетчик 52 орга-.

низует разбиение блоков 6 на триоды следующим образом:(1,3,4); (6,7,8) и т,д.

Контроль идет либо до полной проверки всех блоков по всем тестам, либо до того момента, когда остается не более двух годных логических блоков, В обоих случаях счетчик 52 устанавливается в нулевое состояние,-и при каждом импульсе по входу 21 формируется импульс на выходе 17 блока 4 до тех пор, пока на него не поступит импульс с входа 19.

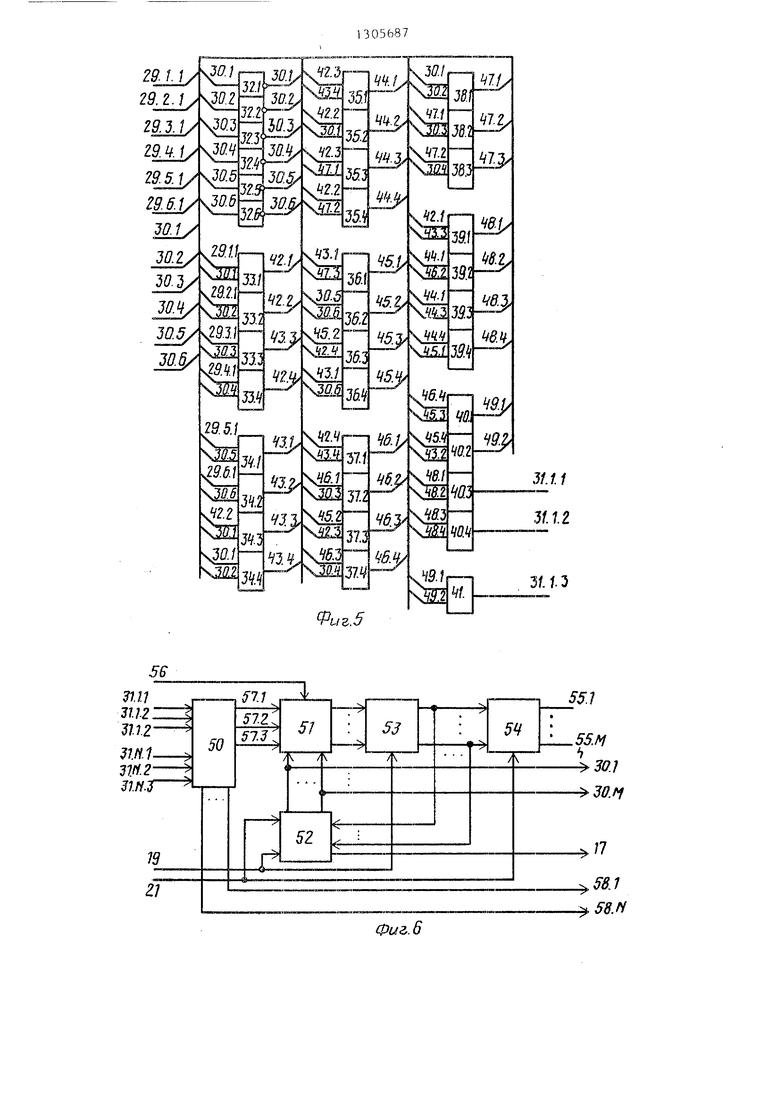

Дешифратор 51 представляет собой комбинационную схему. На одну из груп входов поступают номера трех логичес ких блоков, подвергающихся контролю в данный момент. Дешифратор 51 в зависимости от состояния на входах 57.1, 57.2, 57.3 и 56 признает все логические узлы годными либо указывает на брак одного или нескольких блоков.

Процедура функционирования дешифратора 51 в случае контроля второго, пятого и седьмого блоков в партии, что соответствует логической единице на втором, пятом и седьмом выходах счетчика 52, представлена в табл.1.

Единицы в графах состояния выходо дешифратора 51 означают брак соответствующих блоков. Состояние всех ос-- тальных выходов (кроме второго, пятого и седьмого) дешифратора 51 в- данном случае инеют уровень логического нуля. Работа дешифратора 51 при контроле любых трех логических блоков аналогична приведенной в таблице. При обнаружении дешифратора 51 бракованных блоков соответствующие триггеры 53 устанавливаются в,единичное состояние, фиксируя номера бракованных блоков.

Узел 54 индикации по приходу импульса на вход 21 блока 4 зажигает лампочки Брак, В конце контроля все триггеры 53 обнуляются по вхо- ду 19.

Продолжение таблицы

О О

1 о

о о

о о

1 о

о о

В анализаторе сигнатур начальная

Контроль будет проведен до конца, если количество годных блоков в партии не меньше трех, В противном случае контроль прерывается и горит либо (М-2) лампочки Брак (остается два годных блока), или (М-1) лампочки (остается годный один блок), либо М лампочек Брак (все остальные бло

установка производится сигналом высо- 40 признаны бракованными), При этом

кого уровня на входе 22 и до прихода низкого уровня на вход 22, с каждым синхроимпульсом на входе 21, распределитель 59 формирует импульсы. На входы 58.1-58.N регистра 60 сдвига с элементами сложения по модулю два поступает информация с выходов блока 4, Регистр 60 с элементами сложения по модулю два имеет обратные связи, которые совместно с входами 58,1.- 58.N соединены с элементами сложения по модулю два. Этот код является сигнатурой, поступающей в регистр 61 для хранения. Перед началом формирования каждой очередной сигнатуры содержи- мое регистра 60 сдвига обнуляется. Это устраняет влияние предшествующих сигнатур на последующие и препятствует накоплению ошибки при появлении

10

5

непрарильноп сигнатуры. При несовпадении сигнатур формируе тся команда обмотки на выходе 56,

Устройство работает следующим образом.

При пуске блок 1 формирует синхроимпульсы, поступаюи1ие на вход генератора 2, на выходе которого формируется необходимое количество комбинаций, устанавливающих контролируемые блоки в исходное состояние. Затем на выходе генератора 2 появляется разрешающий уровень, и синхроимпульсы поступают в блоки 4 и 5, По каждому синхроимпульсу идет одновременно контроль трех блоков по первому тесту. Подключение выходов к входам шифратора осуществляет коммутатор в соответствии с номерами, задавае20 мыми счетчиком. При правильном функционировании индикация отсутствует,

Появление неправильной сигнатуры не прерывает процесс контроля, а помогает выявить брак. После прохожде25 ния контроля всех блоков по первому тесту счетчик формирует импульс, запрещающий прохождение синхроимпульсов на блок 4 и 5, и разрешает прохождение синхроимпульсов на вход генератора 2 и т,д.

30

Контроль будет проведен до конца, если количество годных блоков в партии не меньше трех, В противном случае контроль прерывается и горит либо (М-2) лампочки Брак (остается два годных блока), или (М-1) лампочки (остается годный один блок), либо М лампочек Брак (все остальные блов первых двух случаях блоки, индикация номеров которых отсутствует (их может быть либо два, либо один) проходят повторный контроль в составе следующей партии.

Выявление брака не прерывает процесс контроля.

Формула изобретения

Устройство для контроля логических блоков, содержащее блок управления, анализатор сигнатур, мажоритарный блок, генератор тестов, причем вход пуска устройства соединен с входом пуска блока управления, выход начала работы которого соединен с входом сброса анализатора сигнатур,группа информационных входов которого соединена с первой группой выходов мажоритарного блока, вход пуска которого соединен с выходом анализатора сигнатур, вход синхронизации которого соединен с выходом задания режима работы блока управления и с входом синхронизации мажоритарного блока, выходы генератора тестов являются информационными выходами устройства для подключения к информационным вхо- дам п контролируемых логических блоков, вход синхронизации генератора тестов соединен с выходом признака синхронизации блока управления, вход начала контроля которого соединен с выходом признака начала контроля генератора тестов, выход признака конца контроля которого соединен с входом блокировки блока управления, при этом блок управления содержит генера- тор синхроимпульсов, первый и второй триггеры, первый злемент ИЛИ и первый элемент И, а мажоритарный блок содержит дешифратор, причем выход генератора синхроимпульсов соединен с первым входом первого-элемента И, выход которого соединен с выходом задания режима работы блока управления, в ход пуска которого соединен с входом установки первого триггера, выход ко- торого соединен с входом пуска генератора синхроимпульсов, вход установки второго триггера соединен с входом I начала контроля блока управления, выход признака конца контроля которого соединен с выходом второго триггера, вход сброса которого соединен с входом блокировки блока управления, о т- личающееся тем, что, с целью повышения производительности конт роля, устройство содержит коммутатор, мажоритарный блок содержит счетчик, шифратор, группу триггеров, а блок управления содержит третий триггер, элемент НЕ, второй элемент И и вто- рой элемент ИЛИ, причем n/k групп

информационных входов коммутатора являются n/k (k 3) группами информационных входов устройства для подключения к n/k групп выходов контролируемых логических блоков, выходы коммутатора соединены с информационными входами шифратора, группа разрядных выходов счетчика соединена с группой адресных входов коммутатора и с первой группой информационных входов дешифратора, выход признака конца контроля генератора тестов соединен с входом сброса счетчика и входами сброса триггеров группы, выход заема счетчика соединен с вторым входом первого элемента ИЛИ и с входом разрешения анализатора сигнатур,причем вход сброса первого триггера соединен с входом блокировки блока управления и с первым входом второго элемента ИЛИ, выход которого соединен с входом сброса третьего триггера, выход которого соединен с первым входом второго элемента И и через элемент НЕ с вторым входом первого элемента И, второй вход второго элемента И соединен с выходом генератора синхроимпульсов, выход второго элемента И соединен с выходом признака синхронизации блока управления, первый вход первого элемента ИЖ соединен с входом пуска блока управления, выход первого элемента ИЛИ соединен с входом установки третьего . триггера, второй вход второго элемента ИЛИ соединен с входом начала контроля блока управления, вторая группа выходов шифратора соединена с второй группой информационных входов дешифратора, выходы которого соединены с входами установки соответствующих триггеров группы, выходы которых соединены с информационными входами счетчика, вход синхронизации счетчика соединен с синхровходом мажоритарного блока.

te2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления дискретного преобразования Фурье | 1989 |

|

SU1781684A1 |

| Резервированное устройство для контроля и управления | 1991 |

|

SU1830535A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1981 |

|

SU1058097A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля микросхем средней и большой степени интеграции.Цель изобретения - повьппение производительности контроля. Устройство содержит блок Г управления, генератор 2 тестов, коммутатор 3, анализатор 5 сигнатур и мажоритарный блок 4, контролируемые логические блоки 6. В процессе контроля партии из однотипных блоков выявленные бракованные логические блоки автоматически исключаются из процесса контроля, и не требуется повторного контроля. 7 ил., 1 табл. € (Л

N.1.1

t9.I.H

I8.ft.t

2S.f1.ff

Фм

3U2

зи.з

Jt.ftf.i

1Г|г

--.

3f.ff.3

ЗП.2

3/. 1. Э

Фиг.. 6

Г Ч

27 «22

Фиг.7

| Устройство для контроля логических узлов | 1981 |

|

SU1024924A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических узлов | 1984 |

|

SU1188740A2 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-04-23—Публикация

1985-05-21—Подача