(5«) УСТРОЙСТВОСОГЛАСОВАНИЯ ТТЛ с МДП-ЭЛЕМЕНТАМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования ТТЛ-элементов с МДП-элементами | 1980 |

|

SU919089A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Быстродействующий преобразователь уровней напряжения на дополняющих мдп транзисторах | 1979 |

|

SU790330A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Устройство сопряжения биполярных и МДП логических устройств | 1974 |

|

SU591091A1 |

| Логический элемент И | 1981 |

|

SU951707A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Устройство для последовательного включения источников питания в МДП интегральных схемах | 1986 |

|

SU1406771A1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ИНТЕГРАЛЬНЫМ МОДУЛЕМ | 1987 |

|

RU2071636C1 |

Изобретение относится к импульсно технике и предназначено для согласования низковольтных, интегральных эле ментов на биполярных транзисторах с высоковольтными интегральными элементами на комплементарных МДП-тран зисторах. Известно устройство согласования элементов транзисторно-транзисторной логики (ТТЛ элементов) с элементами, выполненными на МДП-транзисторах, содержащее входной МДП-транзистор, включенный между входной шиной и шиной питания, и два МДП-транзистора, нагрузочный и переключающий, последовательно включенные между шиной пи тания и общей шиной, затвор переключающего транзистора подключен к вход ной шине TI . Недостатки известного устройства большая потребляемая мощность и зависимость параметров устройства от крутизны МДП-транзисторов, что снижает надежность устройства. Известно устройство coглa tэвaния ТТЛ с МДП-элементами, содеряи 4ее логический инвертор на комплементарных МДП-траИзисторах и ТТЛ-инвертор с открытым коллектором, включенные между первой низковольтной шиной питания и общей шиной, а также два дополнительных инвертора на МДП-транзисторах, включенных между второй высоковольтной шиной питания и общей шиной, у которых затворы нагрузочных р-канальных транзисторов перекрестно подключены к их выходам, являющимся выходами устройства, при этом вход ТТЛ-инвертора является входом устройства, а его выход подключен к входу логического инвертора и к первой низковольтной шине питания, через входной МДП-транзистор, затвор которого подключен к общей шине,затворы переключающих п-канальных транзисторов дополнительных инверторов подключены соответственно к входу и выходу логического инвертора 2. 3 9 Недостатками известного устройств также являются большая потребляемая мощность из-за протекания тока через входной МДП-транзистор и зависимость параметров устройства от крутизны МДП-транзисторов дополнительных инве торов, что снижает надежность устройства, особенно при изменении окру жающей температуры. Цель изобретения - уменьшение потребляемой мощности и повышение надежности устройства. Для достижения поставленной цели в устройство согласования ТТЛ с МДП-элементами, содержащее логический инвертор на комплементарных МДП-транзисторах и ТТЛ-инвертор с открытым коллектором, включенные между первой низковольтной шиной питания и общей шиной, а также два дополнительных инвертора на МДП-тран зисторах , включенных между второй высоковольтной шиной питания и общей шиной, у которых затворы нагрузочных р-каналъных транзисторов пет рекрестно подключены к их выходам, являющимся выходами устройства, при этом вход ТТЛ-инвертора является входом устройства, а его выход подключен к затвору переключающегоИ-ка- зо нем

нального транзистора первого дополнительного инвертора, введен второй ТТЛ-инвертор с открытым коллектором, включенный между первой низковольтной шиной питания и общей шиной, вход которого подключен к выходу логического инвертора, а выход к затвору переключающего И -канального транзистора второго дополнительного инвертора, при этом вход логического инвертора подключен к входу устройства и в каждом из дополнительных инверторов затворы переключающих И-канальных транзисторов подключены к затворам нагрузочных р -канальных транзисторов.

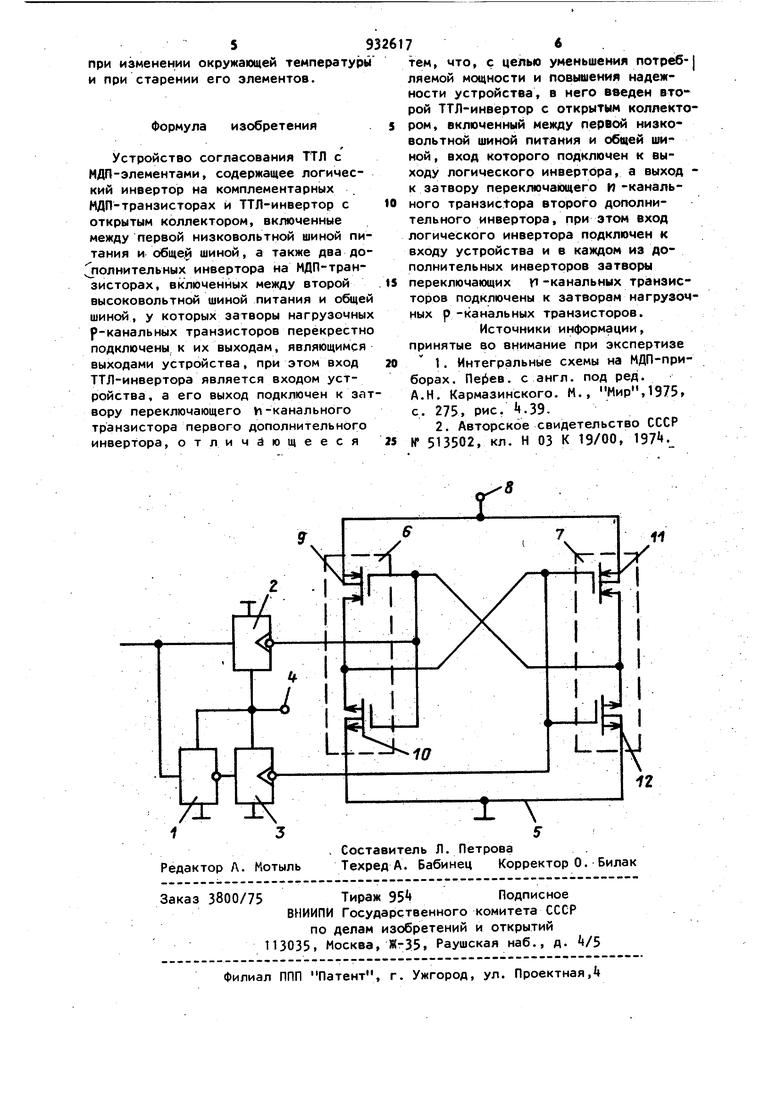

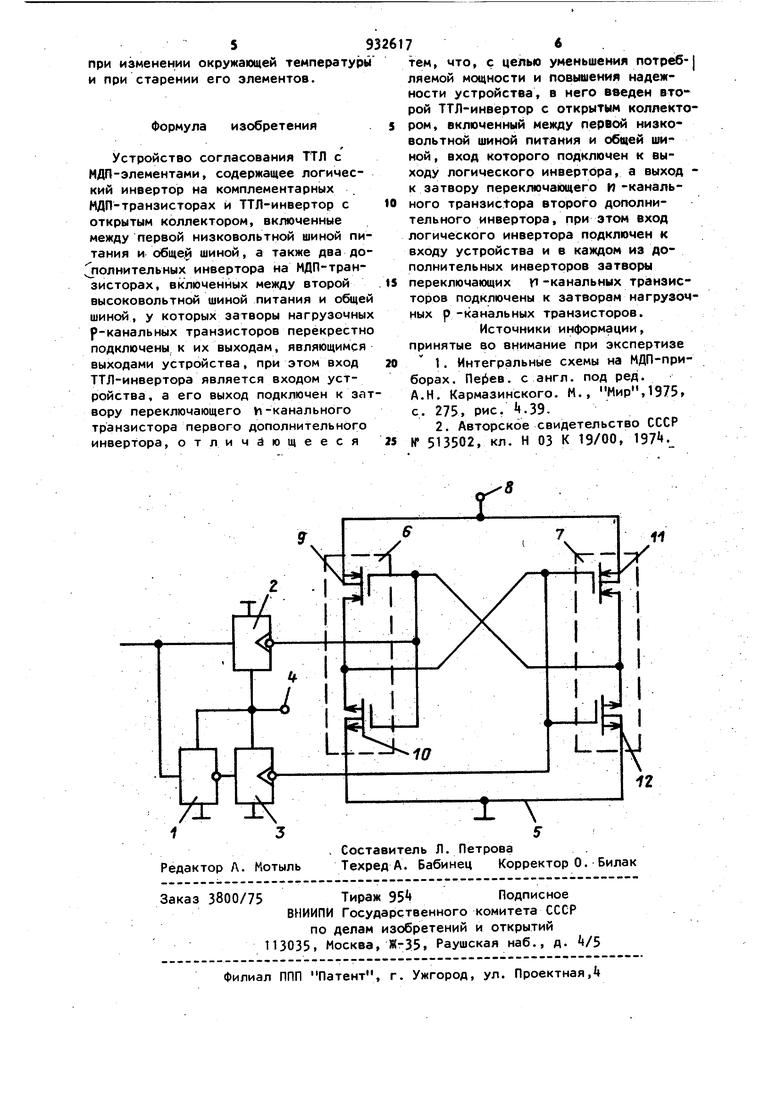

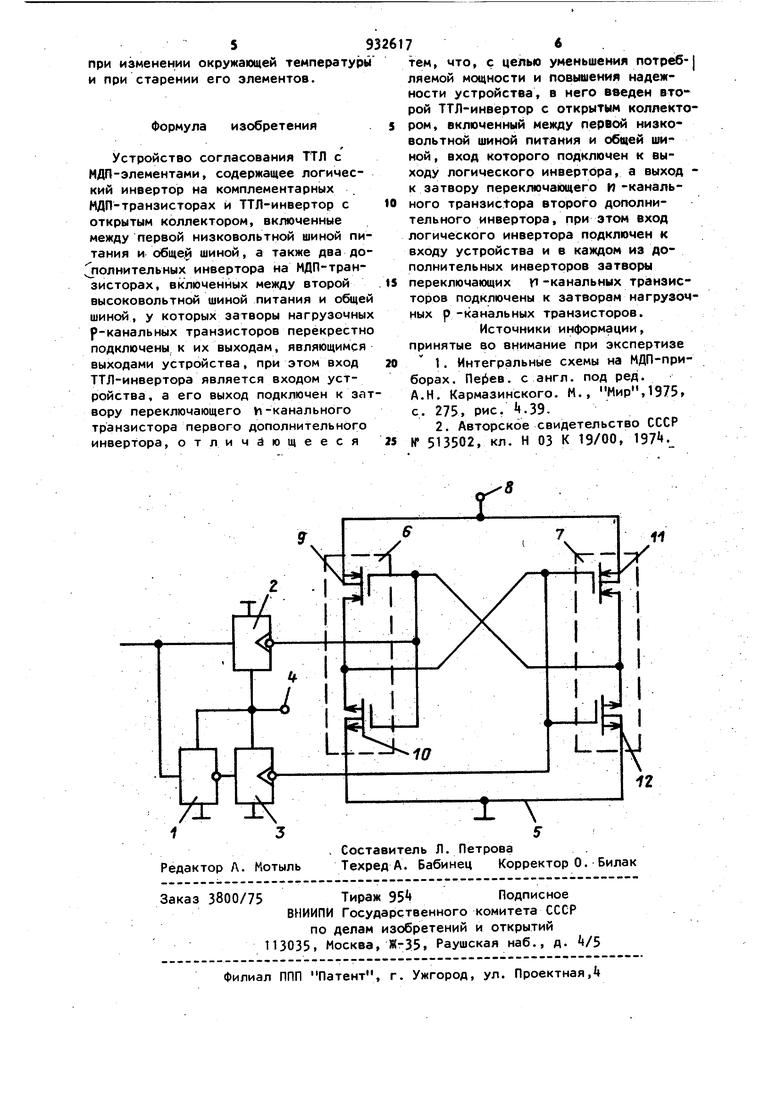

На чертеже представлена электрическая принципиальная схема устройства согласования.

Устройство включает логический инвертор 1 на комплементарных МДП-транзисторах и первый и второй ТТЛ-инверторы 2 и 3 с открытым коллектором и включены между первой низковольтной шиной Ц Питания и общей шиной 5 а два дополнительных инвертора 6 и 7 на МДП-транзисторах включены

сопротивления на выходе инвертора 7, то на выходе инвертора 7 устанавливается низкий логический уровень напряжения. На выходе инвертора 6

устанавливается высокий логический уровень напряжения, так как вход инвертора 6 подключен к выходам ТТЛ-инвертора 2 и инвертора 7, имеющим Низкие логические уровни напряжения.

При этом потребляемая мощность минимальна, так как в инверторах 6 и 7 транзисторы 10 и 11 закрыты, а в инверторах 2 и 3 ток через выходные транзисторы не протекает. Потреблемие мощности происходит только в момент переключения устройства.

Работоспособность устройства сохраняется при любых соотношениях крутизны транзисторов 3 1 и 10, 12,

так как выходное сопротивление ТТЛ-инвертора на несколько порядков меньше выходного сопротивления МДП-инвертора. Кроме того, инверторы 6 и 7 образуют триггер, что значительно ускоряет процесс переключения и делает его независимым от крутизны транзисторов. Это обеспечивает высокую надежность предлагаемого устройства между второй высоковольтной шиной 8 питания и общей шиной 5. Затворы нагрузочного р-канального НДП-транзистора 9 и переключающего И -канального МДП-транзистора 10 инвертора 6 подключены к выходу инвертора 7, а затворы нагрузочного р-канального МДП-транзистора 11 и переключающего и -канального МДП-транзистора 12 инвертора 7 подключены к выходу инвертора 6. Выходы инверторов 6 и 7 являются выходами устройства. Вход инвертора 2, который является входом устройства, и вход инвертора 3 подключены соответственно к входу и выходу инвертора 1. Устройство работает следующим образом. При поступлении на вход логического инвертора 1 и ТТЛ-инвертора 2 сигнала с высоким логическим уровнем напряжения на выходе ТТЛ-инвертора 2 будет низкий логический уровень напряжения, а на выходе ТТЛ-инвертора 3 - высокий логический уровень напряжения. Поскольку сопротивление на выходе ТТЛ-инвертора 2 в состоянии с низким логическим уровнапряжения значительно меньше

Авторы

Даты

1982-05-30—Публикация

1980-06-05—Подача