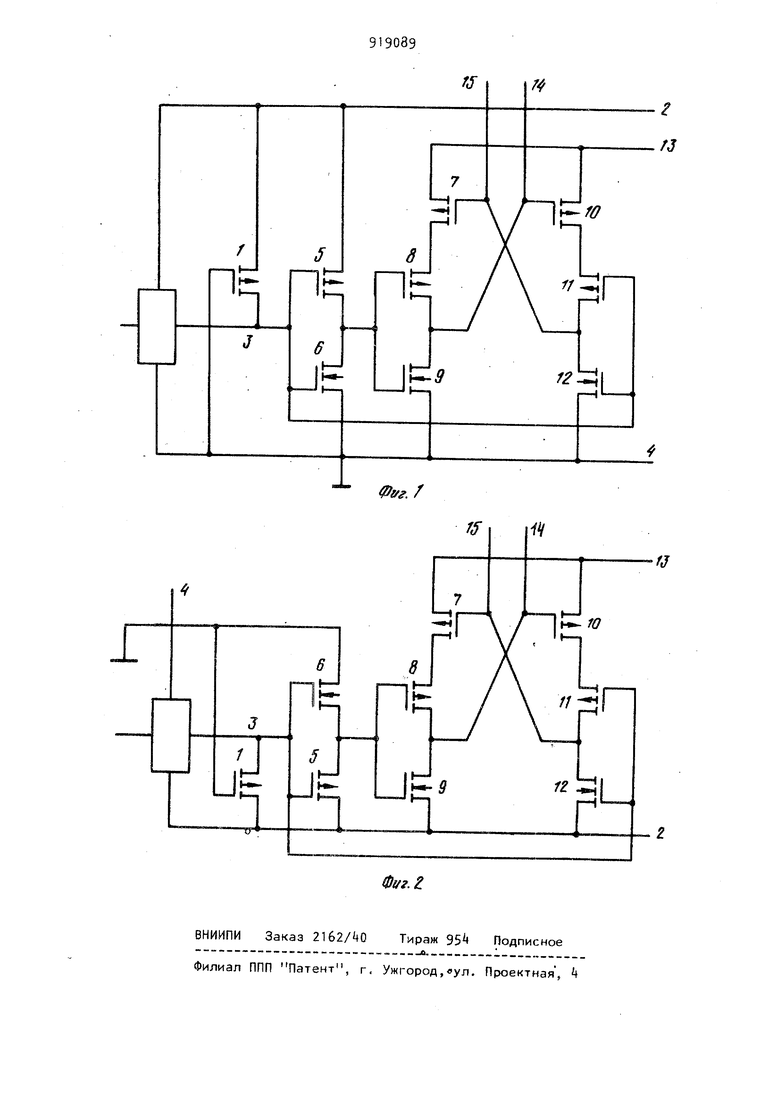

(54) УСТРОЙСТВО СОГЛАСОВАНИЯ ТТЛ ЭЛЕМЕНТОВ Изобретение относится к автоматике и вычислительной технике и может быть использовано для согласования диодно-транзисторных и транзис торно-транзисторных (ДТЛ и ТТЛ) логи ческих элементов с элементами на дополняющих МДП-транзисторах. Известно устройство согласования ТТЛ элементов с МДП элементами, выполненное на дополняющих {-ШП-транзис торах, содержащее входной транзистор первый и второй инверторы Tl . Недостатком такого устройства явл ется невозможность согласования ТТЛ элементов с ЩП элементами, напряжение питания которых превышает напряжение питания ТТЛ элементов. Известно устройство согласования ТТЛ элементов с элементами на дополняющих МДП-транзисторах, напряжение питания которых превышает напряжение питания ТТЛ элементов, содержащее входной транзистор, включенный между первой шиной питания и входной шиной С МДП ЭЛЕМЕНТАМИ устройства, затвор которого подключен к общей шине, первый инвертор, включенный между первой шиной питания и общей шиной, вход которого подключен к входной шине устройства, и второй и третий инверторы, истоки нагрузочных транзисторов которых подключены к второй шине питания, а затворы образуют перекрестные связи с выходами этих инверторов, входами второго и третьего инверторов являются затворы переключающих транзисторов, которые подключены соответственно к входу и выходу первого инвертора 2 . Недостатками известного устройства являются сравнительно низкое быстродействие и большая потребляемая мощность в режиме переключения. Это обусловлено тем, что при открывании переключающего транзистора во втором или третьем инверторе нагрузочный транзистор инвертора еще открыт, и через оба транзистора кратковременно протекает сравнительно большой сквоз ной, ток. Уменьшение сквозных токов уменьшения крутизны нагрузочны транзисторов во втором и третьем инверторах приводит к снижению быстродействия. Цель изобретения - повышение быст родействия и уменьшение потребляемой мощности. Для достижения поставленной цели в устройство согласования ТТЛ элемен с МДП элементами, выполненное на дополняющих МДП-транзисторах, содержащее входной транзистор, включенный между первой шиной питания и входной шиной устройства, затвор которого подключен к общей шине, первый инвер |тор, включенный между первой шиной п }тания и общей шиной, вход которого подключен к входной шине устрой- ства, и второй и третий инверторы, истоки нагрузочных транзисторов которых подключены к второй шине питания, истоки переключающих транзисторов - к общей шине, стоки переключающих транзисторов и затворы нагрузочных транзисторов образуют перекрестные связи и подключены к соот аетсТвующим выходным шинам, а затворы переключающих транзисторов подключены соответственно к выходу и входу первого инвертора, введены два дополнительных транзистора с каналом того же типа, что и у нагрузочных транзисторов, первый дополнительный транзистор включен между нагрузочным и переключающим транзисторами второго инвертора, а второй - между нагрузочным и переключающим транзисторами третьего инвертора, затвор дополнительного транзистора в каждом инверторе подключен к затвору переключающего транзистора. На фиг. 1 представлена электрическая принципиальная схема устройства, выполненного на дополняющих МДП-транзисторах; на фиг. 2 то же, вариант (напряжение питания на шинах 2 и 13 разной полярности). Входной транзистор 1 включен между первой шиной 2 питания и входной шиной 3 устройства, его затвор Подключен к общей шине Д. Первый инвертор образован транзисторами 5 6 и включен между шинами 2 и , его вход подклнэчен к шине 3 Второй и третий инверторы образованы соответственно, последовательно включенными транзисторами 7s 8s 9 и 10, 11, 12о Истоки нагрузочных транзисторов 7 и 10 подключены к второй шине 13 питания, истоки переключающих транзисторов 9 и 12 - к шине k, стоки транзисторов 9 и 12 и затворы транзисторов 7 и 10 образуют перекрестные связи и подключены к соответствующим выходным шинам 1ч и 15. Затворы первого дополнительного транзистора 8 и переключающего транзистора 9 подключены к выходу первого инвертора, а затворы второго дополнительного транзистора 11 и переключающего транзистора 12 к входу первого инвертора. Устройство работает следующим образом. Входной транзистор 1 предназначен ДЛЯ повышения уровня напряжения логической единицы на входе устройства и находится в открытом состоянии во всех режимах работы устройства. Пусть в исходном состоянии уровень напряжения на входной шине 3 устройства соответствует логическому (0-0,5)В. При этом на выходе первого инвертора устанавливается напряжение, равное напряжению шины 2 питания (Е;() Уровень напряжения затворах транзисторов 8 и 9 и нулевой уровень напряжения на затворах транзисторов 11 и 12 обеспечивают формирование на первой выходной шине 1 нулевого уровня напряжения, а на второй выходной шине 15 уровня напряжения,соответствующего напряжению шины 13 питания (Е,) . При поступлении на вход 3 устройства уровня логической единицы, на выходе первого инвертора формируется нулевой уровень напряжения, который обеспечивает запирание транзистора 9 и полностью открывает транзистор 8. Входной сигнал (уровень логической единицы), поступающий на затворы транзисторов 11 и 12, обеспечивает открывание транзистора 12 и уменьшает проводимость канала транзистора 11, так как напряжение затвор-исток транзистора 11 уменьшается за счет входного сигнала. При этом независимо от напряжения на затворе транзистора 10 из-за модуляции сопротивления канала транзистора 11 на выходе третьего инвертора (на второй выходной шине 15) быстро формируется уровень напряжения, близкий к нулевому, что, в свою очередь, обеспечивает открывание транзистора 7. Через транзисторы 7 и 8 на первой выходной тпйне 14 формируется уровень напряже |Ния, равный Ejj. По мере повышения напряжения на первой выходной шине Т усиливается действие положительной обратной связи с выхода второго инвертора (с первой выходной ыины 1 на затвор транзистора 10, который постепенно закрывается, и сквозной ток в третьем инверторе быстро исчезает. Таким образом, процесс пере хода устройства согласования в ново состояние проходит лавинообразно. Модуляция сопротивления канала транзисторов 8 и 11 нр только позволяет уменьшить сквозной ток во вт ром и третьем инверторах, но также и увеличить крутизну транзисторов 7 и 10, что, в свою очередь, позволяет ускорить перезаряд емкостей, подключенных к выходным шинам, и, следовательно, повысить быстродейст вие устройства. Работа второго варианта устройст (фиг 2) практически не отличается от работы первого варианта устройст ства (фиг. 1) с учетом соответствую |1цего изменения типа проводимости канала у транзисторов во втором и третьем инверторах. Введение дополнительных транзисторов и увеличение крутизны нагрузочных транзисторов позволяет повысить быстродействие почти в 1,7 раз и уменьшить потребляемую мощность по сравнению с прототипом почти на 30. Формула изобретения Устройство согласования ТТЛ элементов с 1ДП элементами, выполненно 9 на дополняющих МДП-транзисторах, содержащее входной транзистор, включенный между первой шиной питания и входной шиной устройства, затвор которого подключен к общей шине, первый инвертор, включенный между первой шиной питания и общей шиной, вход которого подключен к входной шине устройства, и второй и третий инверторы, истоки нагрузочных транзисторов которых подключены к второй шине питания, истоки переключающих транзисторов - к общей шине,стоки переключающих транзисторов и затворы нагрузочных транзисторов образуют перекрестные связи и подключены к соответствующим выходным шинам, а затворы переключающих транзисторов подключены соответственно к выходу и входу первого инвертора, отличающееся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, в него введены два дополнительных транзистора с каналом того же типа, что и у нагрузочных транзисторов, первый дополнительный транзистор включен между нагрузочным и переключающим транзисторами второго инвертора, а второй - между нагрузочным и переключающим транзисторами третьего инвертора, затвор дополнительного транзистора в каждом инверторе подключен к затвору переключающего транзистора. Источники информации, принятые во внимание при экспертизе 1.Заявка Франции N 2373921, кл. Н 03 К 19ЛО, 1978. 2.Авторское свидетельство СССР № 513502, кл. Н 03 К 19/00, 197.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство согласования ТТЛ с МДП элементами | 1980 |

|

SU932617A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Устройство согласования ТТЛ-элементов с МДП-интегральными элементами | 1982 |

|

SU1064469A1 |

| Устройство согласования ттл-схемС Мдп-иНТЕгРАльНыМи СХЕМАМи | 1979 |

|

SU818015A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Логический элемент на мдп-транзисторах | 1977 |

|

SU664297A1 |

| Быстродействующий преобразователь уровней напряжения на дополняющих мдп транзисторах | 1979 |

|

SU790330A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Формирователь выходного сигнала на МДП-транзисторах | 1986 |

|

SU1338055A1 |

Авторы

Даты

1982-04-07—Публикация

1980-06-04—Подача