1

Изобретение относится к электронике, в частности к импульсной технике, и может быть использовано в ин-тегральных цифровых схемах.

Известно устройство преобразования уровней напряжения, содержащее входной МДП транзистор и инвертор на дополнякщих гадп транзисторах, вход и выход которого подключены соответственно к затворам п-канальных транзисторов первого и второго дополнительных инверторов, у которых затворы р-канальных транзисторов подключены перекрестно к выходам

1 .

Недостатком устройства является

большая потребляемая мощность и низкое быстродействие.

-Известен преобразователь уровней напряжения на дополняющих МДП транзисторах, содержа пий тву ктактный инвертор на трех транзисторах (двух последовательно включенных нагрузочных р-канальных транзисторах и переключающем п -канальному , включенный между первой шиной питания и общей шиной, и двухтактный повторитель на двух транзисторах, нагрузочном р-канальном и переключающем h-канальноМ, затвор которого подключен к второй шине питания, включенный между первой шиной питания и входной шиной, к которой подключен также затвор переключающего тран5 зистора инвертора, шину прямого выхода , к которой подключены стоки транзисторов повторителя и затвор первого нагрузочного транзистора инвертора, и шину инверсного выхода,

10 к которой подключен затвор нагрузочного транзистора повторителя, сток переключающего транизистора инвертора и сток второго погрузочного транзистора инвертора, затвор которого подключен ко входной шине 2 .

Недостатком известного преобразователя уровней напряжения является низкое быстродействие,которое обусловлено различными размерами перек20 лючаюсцих и нагрузочных транзисторов инвертора и повторителя,что необходимо для обеспечения условий работоспособности устройства в статическом режиме .

25 Цель изобретения - повышение быстродействия устройства.

Для достижения поставленной цели в быстродействующий преобразователь уровней напряжения на дополняющих .

30 МДП транзисторах, срдержрлсий двухтактный инвертор на двух транзисторах, нагрузочном р-кянальном и переключающем п-канальиом,включенный между первой шиной питания и общей шиной,и двухтактный повторитель на двух транзисторах , нагрузочном р-канальном и переключагачем п-канальном,затвор которого подключен ко второй шине питания, включенный между первой шиной питания и входной шиной, к которой подключен также затвор переключающег транзистора инвертора, шину прямого выхода, к которой подключены стоки транзисторов повторителя и затвор нагрузочного транзистора инвертора, и шину инверсного выхода, к которой подключены стоки транзисторов инвертора и затвор нагрузочного транзистора повторителя, введены два форсирующих р-канальных транзистора,первый из них подключен параллельно нагрузочному транзистору инвертора, а второй параллельно нагрузочному транзистору повторителя,и два двухвходовых элемента ИЛИ с задержкой по первому входу, выход первого элемента ИЛИ подключен к затвору первого форсирующего транзистора, а его первый и второй входы - соответственно к шинам инверсного и прямого выхода, выход второго элемента ИЛИ подключен к затвору второго форсирующего транзистора, а его первый и второй входы - соответственно к шинам прямого и инверсного выхода. Кроме того, двухвходовый элемент ИЛИ с задержкой по первому входу содержит два каскадно включенных однотактных инвертора, подключенных между первой шиной питания и общей шиной, двунаправленный ключ, включенный между вторым входом и выходом элемента,и р-канальный транзистор фиксации уровня, включенный между выходом элемента и первой шиной питания, причем вход первого инвертора подключен к первому входу элемента, его выход - к затворам транзистора фиксации уровня и п-канального транзистора двунаправленного ключа, выход второго инвертора подключен к затвору р-канального транзистора двунаправленного ключа.

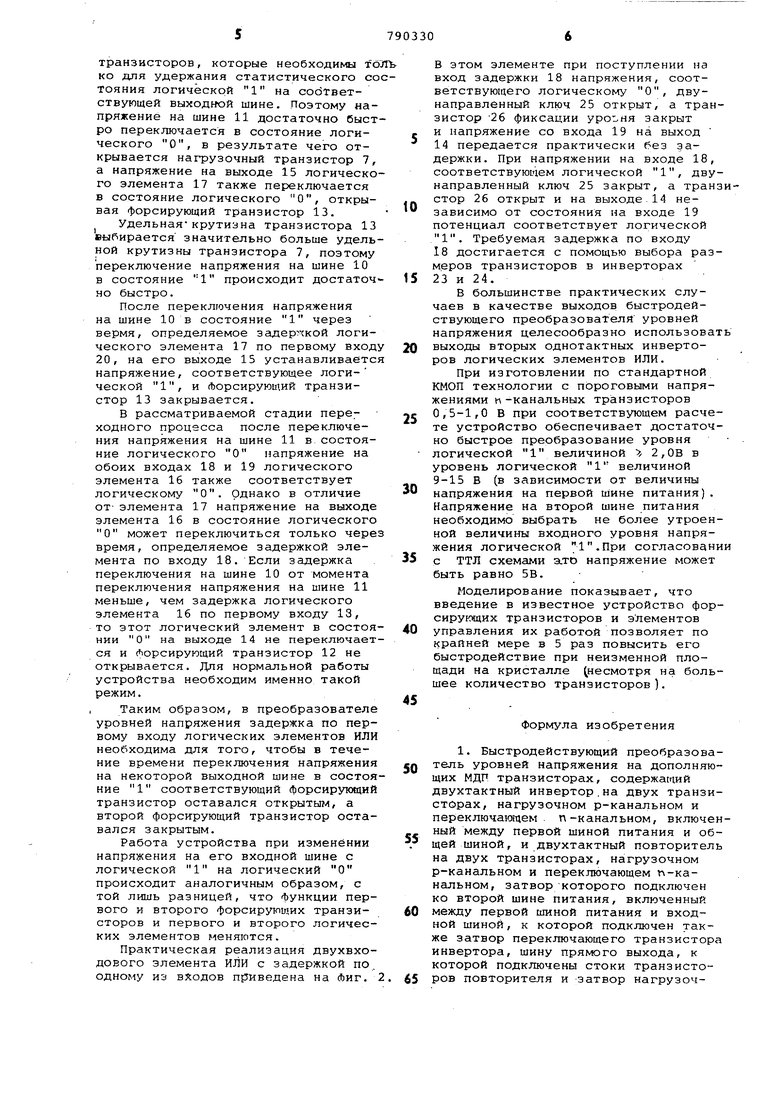

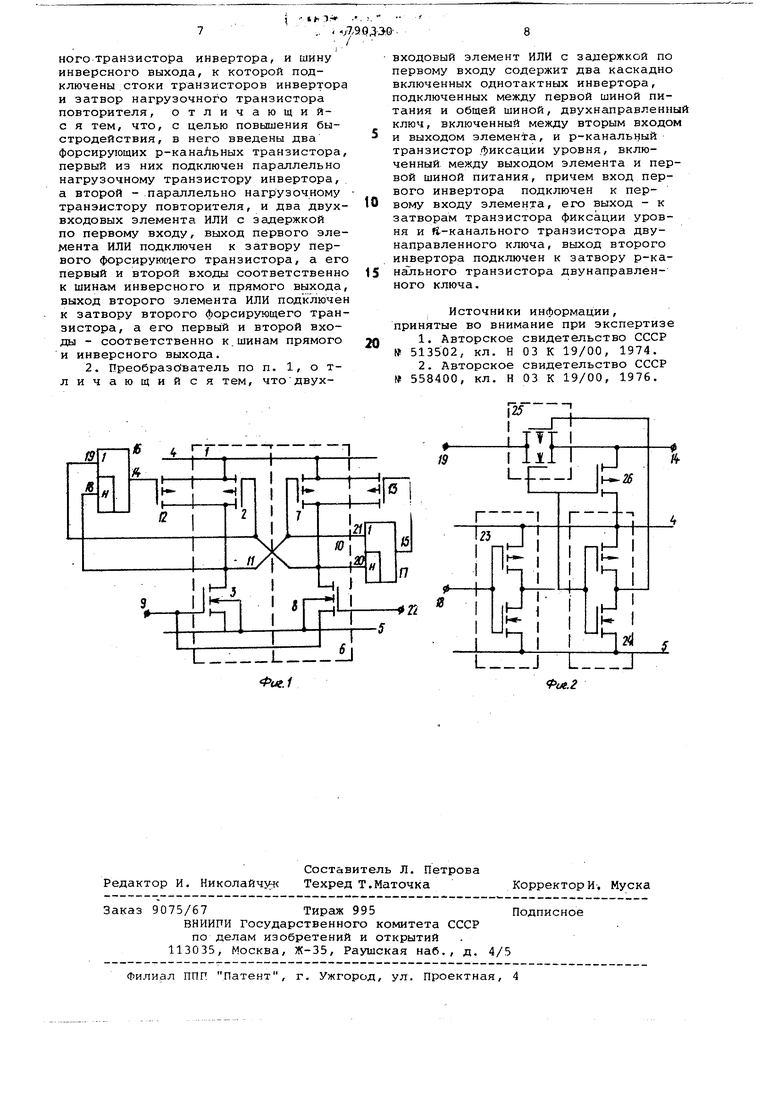

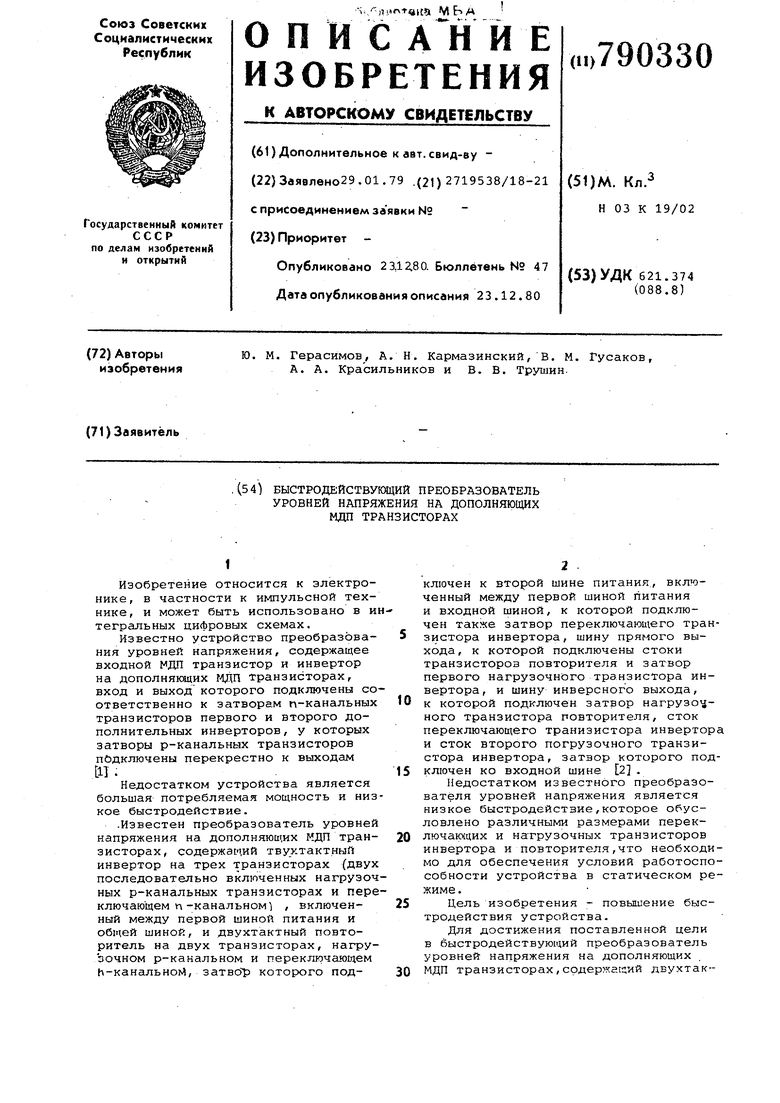

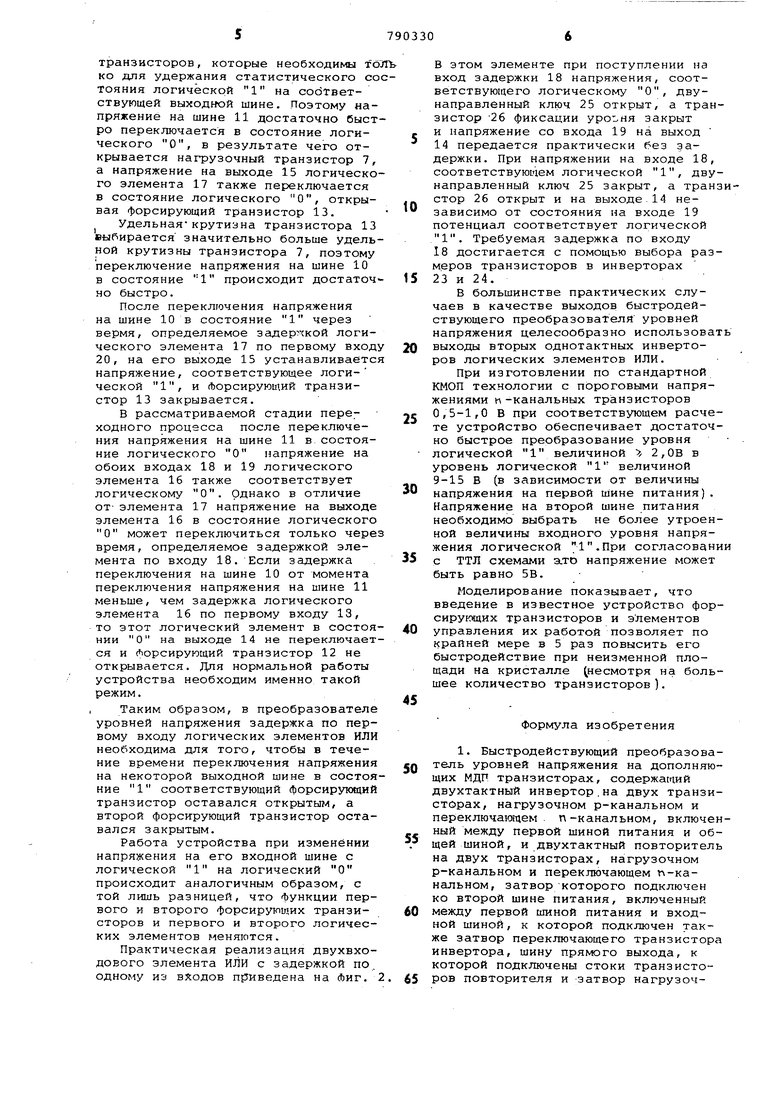

На фиг. 1 представлена электрическая принципиальная схема быстродействующего преобразователя уровней напряжения на дополняющих МДП транзисторах; на фиг. 2 - то же, э;|емента, ИЛИ.

Преобразователь содержит двухтактньдй инвертор 1 на двух транзисторах, нагрузочном р-канальном транзисторе 2 и переключсишцем м-канальном транзисторе 3, включенный между первой шиной 4 питания и общей шиной 5, двухтактный повторитель 6на двух транзисторах, нагрузочном р-канальном 7 и переключающем Vi-канальном 8, включенный между шиной

4 и входной шиной 9,к которой подклчен также затвор транзистора 3,шину прямого выхода 10, подключенную к стокам транзисторов 7 и 8 к затвору транзистора 2, шину инверсн го выхода 11, подключенную к стокам транзисторов 2 и 3 и к затвору транзистора 7, параллельно транзисторам 2 и 7 включены соответственно форсирующие транзисторы 12 и -13, затворы которых подключены соот1ветственно к выходу 14 или 15 элементов ИЛИ 16 и 17 с задержкой по первому входу, первый и второй входы 18 и 19 элемента 16 подключены соответственно к шинам 11 и 10, а первый и второй входы 20 и 21 элемента 17 подключены соответственно к шинам 10 и 11. Затвор транзистора 3 подключен ко второй шине 22 питания.

Элемент ИЛИ 16 с задержкой по первому входу 18 содержит два каскадно включенных однотактных инвертора 23 и 24, подключенных между шиной 4 питания и общей шиной 5, двунаправленный клю.ч 25, включенный между вторым входом 19 и выходом 14 элемента, и р-канальный транзистор 26 фиксации уровня, включенный между выходом 14 и шиной 4, вход первого инвертора подключен к первому входу элемента 18, а его выход к затворам транзистора 26 и и-каналного транзистора двунаправленного ключа 25, второго инв.ертора 24 подключен к затвору р-канальноро транзистора двунаправленного ключа 25.

Устройство работает следующим образом.

В исходном состоянием напряжение на входной шине 9 соответствует логическому О. Тогда транзисторы

8и 2 открыты./, ;а транзисторы 3 и 7 закрыты, напряжение на шине 10 соответствует логическому О, на шине 11 - 1. Поскольку на одном из входов логических элементов 16,и 17 напряжение соответствует логической 1, то такое напряжение поддерживается и на выходах этих элементов,

в результате чего формирующие транзисторы 12 и 13 закрыты и не влияют на работу устройства в стационарном состоянии.

При изменении напряжения на шине

9с логического О на логическую 1 переключающий транзистор 3 открывается, а транзистор 8 закрывается по истоку.в дв хтактном повторителе 6 оба транзистора 7 и 8 закрыты, и напряжение на шине 10 не изменяется. В двухтактном инверторе 1 переключающий и нагрузочный транзисторы 3 и 2 открыты. Удельная крутизна переключающих транзисторов выбирается значительно большей по отношению к крутизнам нагрузочных транзисторов, которые необходимы то ко для удержания статистического со тояния логической 1 на соответствующей выходной шине. Поэтому напряжение на шине 11 достаточно быст ро переключается в состояние логического О, в результате чего открывается нагрузочный транзистор 7, а напряжение на выходе 15 логическо го элемента 17 также переключается в состояние логического О, открывая форсирующий транзистор 13. Удельная-крутизна транзистора 13 выбирается значительно больше удель ной крутизны транзистора 7, поэтому переключение напряжения на шине 10 в состояние происходит достаточ но быстро. После переключения напряжения на шине 10 в состояние 1 через вермя, определяемое задер -ской логического элемента 17 по первому вход 20, на его выходе 15 устанавливаетс напряжение, соответствующее логической 1, и Лорсирующий транзистор 13 закрывается. В рассматриваемой стадии переходного процесса после переключения напряжения на шине 11 в состояние логического О напряжение на обоих входах 18 и 19 логического элемента 16 также соответствует логическому О. Однако в отличие от- элемента 17 напряжение на выходе элемента 16 в состояние логического О может переключиться только чере время, определяемое задержкой элемента по входу 18. Если задержка переключения на шине 10 от момента переключения напряжения на шине 11 меньше, чем задержка логического элемента 16 по первому входу 13, то этот логический элемент в состоя нии О на выходе 14 не переключает ся и форсирующий транзистор 12 не открывается. Для нормальной работы устройства необходим именно такой режим. , Таким образом, в преобразователе уровней напряжения задержка по первому входу логических элементов ИЛИ необходима для того, чтобы в течение времени переключения напряжения на некоторой выходной шине в состоя ние 1 соответствующий форсирующий транзистор оставался открытым, а второй форсирующий транзистор оставался закрытым. Работа устройства при изменении напряжения на его входной щине с логической 1 на логический О происходит аналогичным образом, с той лишь разницей, что функции первого и второго форсирующих транзисторов и первого и второго логических элементов меняются. Практическая реализация двухвходового элемента ИЛИ с задержкой по. одному из входов приведена на Фиг. в этом элементе при поступлении на вход задержки 18 напряжения, соответствующего логическому О, двунаправленный ключ 25 открыт, а транзистор 26 фиксации уровня закрыт и напряжение со входа 19 на выход 14 передается практически без задержки. При напряжении на входе 18, соответствующем логической 1, двунаправленный ключ 25 закрыт, а транзистор 26 открыт и на выходе.14 независимо от состояния на входе 19 потенциал соответствует логической 1. Требуемая задержка по входу 18 достигается с помощью выбора размеров транзисторов в инверторах 23 и 24. В большинстве практических случаев в качестве выходов быстродействующего преобразователя уровней напряжения целесообразно использовать выходы вторых однотактных инверторов логических элементов ИЛИ. При изготовлении по стандартной КМОП технологии с пороговыми напряжениями п-канальных транзисторов 0,5-1,0 В при соответствующем расчете устройство обеспечивает достаточно быстрое преобразование уровня логической 1 величиной / 2,0В в урювень логической 1 величиной 9-15 В (в зависимости от величины напряжения на первой шине питания). Напряжение на второй шине питания необходимо выбрать не более утроенной величины входного уровня напряжения логической 1.При согласовании с ТТЛ схемами а.то напряжение может быть равно 5В. Моделирование показывает, что введение в известное устройство форсирующих транзисторов и элементов управления их работой позволяет по крайней мере в 5 раз повысить его быстродействие при неизменной площади на кристалле (несмотря на большее количество транзисторов). Формула изобретения 1. Быстродействующий преобразователь уровней напряжения на дополняющих МДП транзисторах, содержащий двухтактный инвертор.на двух транзисторах, нагрузочном р-канальном и переключающем, п-канальном, включенный между первой шиной питания и общей шиной, и двухтактный повторитель на двух транзисторах, нагрузочном р-канальном и переключающем п-канальном, затвор которого подключен ко второй шине питания, включенный между первой шиной питания и входной шиной, к которой подключен также затвор переключающего транзистора инвертора, шину прямого выхода, к которой подключены стоки транзисторов повторителя и затвор нагрузочного транзистора инвертора, и шину инверсного выхода, к которой подключены стоки транзисторов инвертора и затвор нагрузочного транзистора повторителя, отличающийс я тем, что, с целью повышения быстродействия, в него введены два форсирующих р-канаЛьных транзистора, первый из них подключен параллельно нагрузочному транзистору инвертора, а второй - параллельно нагрузочному транзистору повторителя, и два двухвходовых элемента ИЛИ с задержкой по первому входу, выход первого элемента ИЛИ подключен к затвору первого форсирую1т1его транзистора, а его первый и второй входы соответственно к шинам инверсного и прямого выхода, выход второго элемента ИЛИ подключен к затвору второго форсирующего транзистора, а его первый и второй входы - соответственно к.шинам прямого и инверсного выхода.

2. Преобразователь по п. 1, о тличающийся тем, чтодвух входовый элемент ИЛИ с задержкой по первому входу содержит два каскадно включенных однотактных инвертора, подключенных между первой шиной питания и общей шиной, двухнаправленный ключ, включенный между вторым входом 5 и выходом элемента, и р-канальный транзистор .фиксации уровня, включенный между выходом элемента и первой шиной питания, причем вход первого инвертора подключен к первому входу элемента, его выход - к затворам транзистора фиксации уровня и 1-канального транзистора двунаправленного ключа, выход второго инвертора подключен к затвору р-каS нального транзистора двунаправленного ключа.

Источники информации, принятые во внимание при экспертизе 0 1. Авторское свидетельство СССР № 513502, кл. Н 03 К 19/00, 1974.

2. Авторское свидетельство СССР № 558400, кл. Н 03 К 19/00, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Преобразователь уровней напряжения | 1986 |

|

SU1358088A1 |

| Устройство преобразования уровней напряжения | 1976 |

|

SU558400A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Устройство задержки импульсов | 1977 |

|

SU680163A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Элемент с тремя состояниями | 1978 |

|

SU725235A1 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

Фиг.1

fue.2

Авторы

Даты

1980-12-23—Публикация

1979-01-29—Подача