2.Устройство согласования уровней напряжения, содержащее два р-канальных нагрузочных МДП-транзистора, затвор каждого из которых перекрестно подключен к стоку противоположного транзистора, и два п-канальных переключающих МДП-транзнстора, сток ка едого из которых подключен к стоку соответствующего нагрузочного МДП-транзистора и к соответствующему выходу устройства, а исток первого переключающего ЦДЛ-транзистора подключен к входу устройства, отличающееся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, в него введены пять дополнительных МДП-транзисторов, первый и второй дополнительные р-канальные МДП-транзисторы, соединенные параллельно, которые включены между шиной питания и затвором первого переключающего ЩП-тpaнзиcтopa, а их затворы соответственно подключены к первому выходу устройства и к затвору первого переключающего МДП-транзистора, истоки третьего и четвертого дополнительных р-канальных МДТ-транзисторов подключены к шине питания, стоки - к истокам соответствующих нагрузочных МДП-транзисторов, а затворы - к затворам соответствующих переключающих МДП-транзисторов пятьм дополнительный п-канальннй ЦЦП-транзистор включен между затвором первого переключающего МДП-транзистора и входом устройства, а его затвор подключен к затвору второго переключающего МДП-транзистора и к общей шине, исток второго переключающего МДП-транзистора подключен к входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Быстродействующий преобразователь уровней напряжения на дополняющих мдп транзисторах | 1979 |

|

SU790330A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Устройство согласования ТТЛ-элементов с МДП-элементами | 1980 |

|

SU919089A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Преобразователь уровней напряжения на дополняющих МДП-транзисторах | 1983 |

|

SU1129739A1 |

| Устройство преобразования уровней напряжения | 1976 |

|

SU558400A1 |

| Устройство согласования ттл-схемС Мдп-иНТЕгРАльНыМи СХЕМАМи | 1979 |

|

SU818015A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

I. Устройство согласования .уровней напряжения, содержащее два р-канапьных нагрузочных МДП-транзистора, затвор каждого из которых перекрестно подключеи к стоку противоположного транзистора, и два п-канальных переключающих МДП-транзистора, сток каждого из которых подключен к стоку соответствующего нагрузочного ЩЩ-траизистора и к соответствующему выходу устройства, исток первого переключающего МДПтранзистора подключен к входу yqT/ройства и к затвору второго прреключающего ЩЩ транзистора, исток /А которого подключен к общей шине, отличающееся тем, что, с целью повышения быстродействия и уменьшения потребляемой мощности, в него введены пять дополнительных МДИ-транзисторов, первый и второй дополнительные р-канальные МДП-транзисторы, соединенные параллельно, которые включены между шиной питания и затвором первого пере шючающего МДП-транзистора, а. их затворы соответственно подключены к первому выходу устройства и к затвору пе1 яого переключающего МДП-транзистора, истоки третьего и четвертого дополнительных р-канальных МДП-транзйс«о торов подключены к щине питания, стоки - к истокам соответствующих нагрузочных МДП-транзисторов, а затворы - к затворам соответст Ующих переключающих МДП-транзисторов, пятый дополнительный п-канальный МДП-транзистор включен между затвором первого переключающего Ц Ц1-транзистора и общей шиной, а его затвор &0 подключен к входу устройства. эо ;о 4

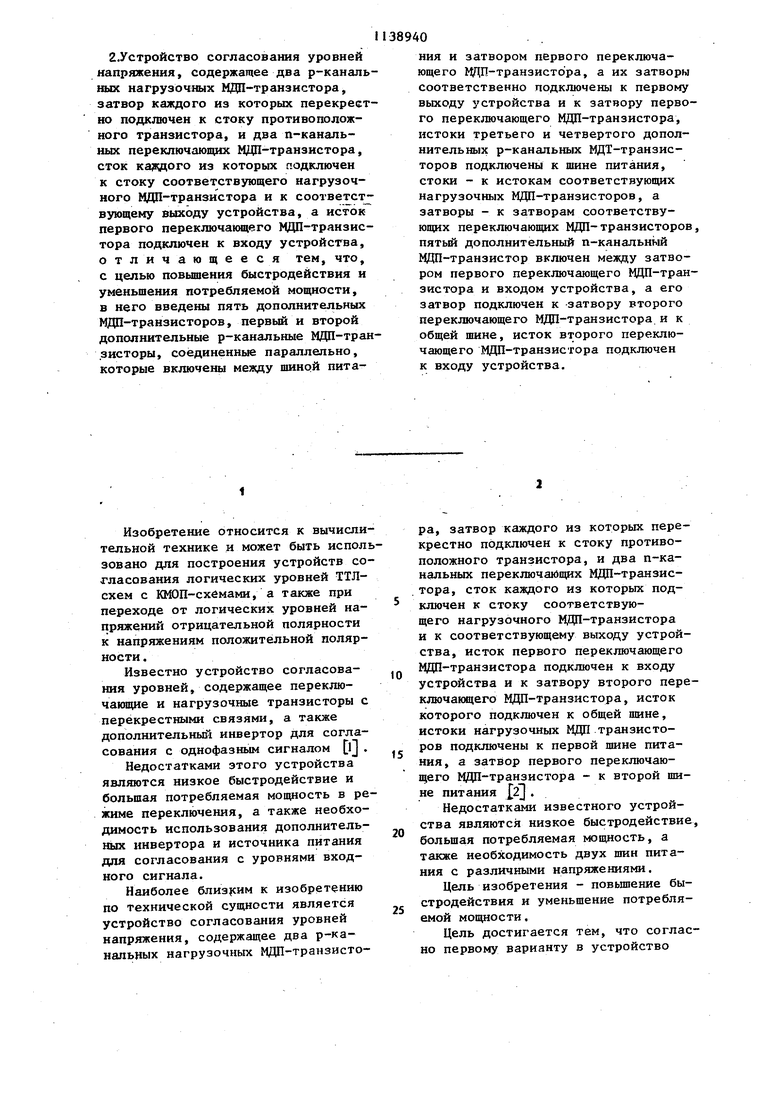

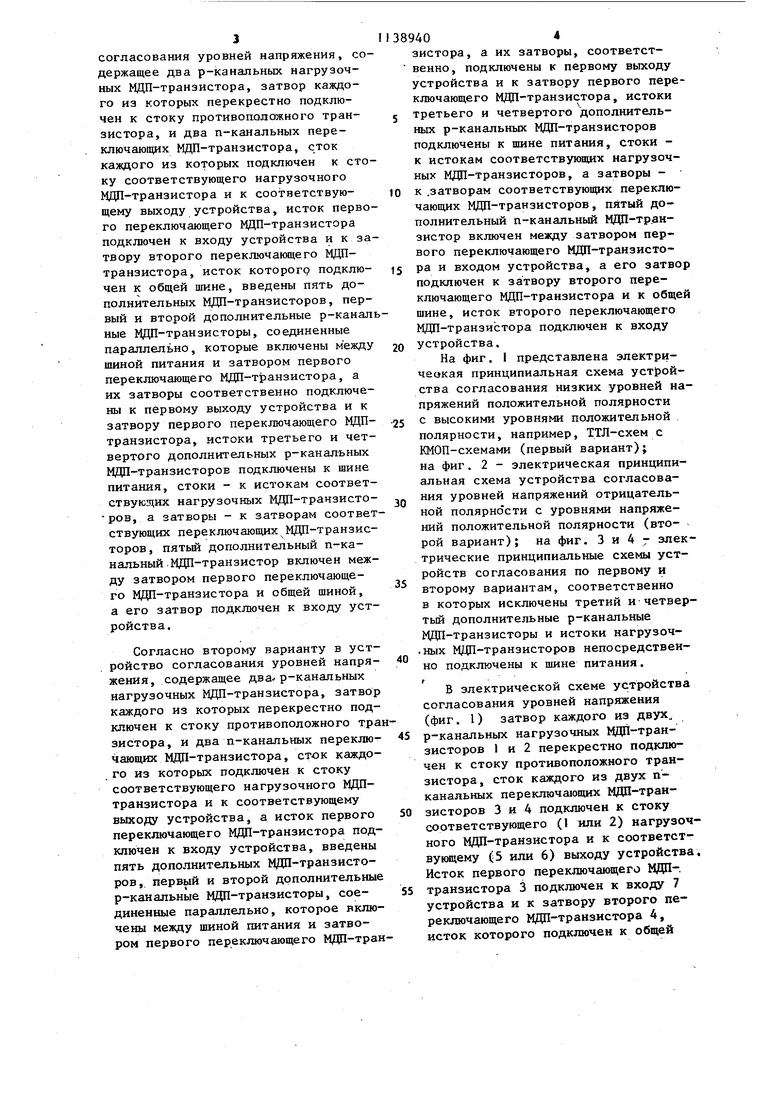

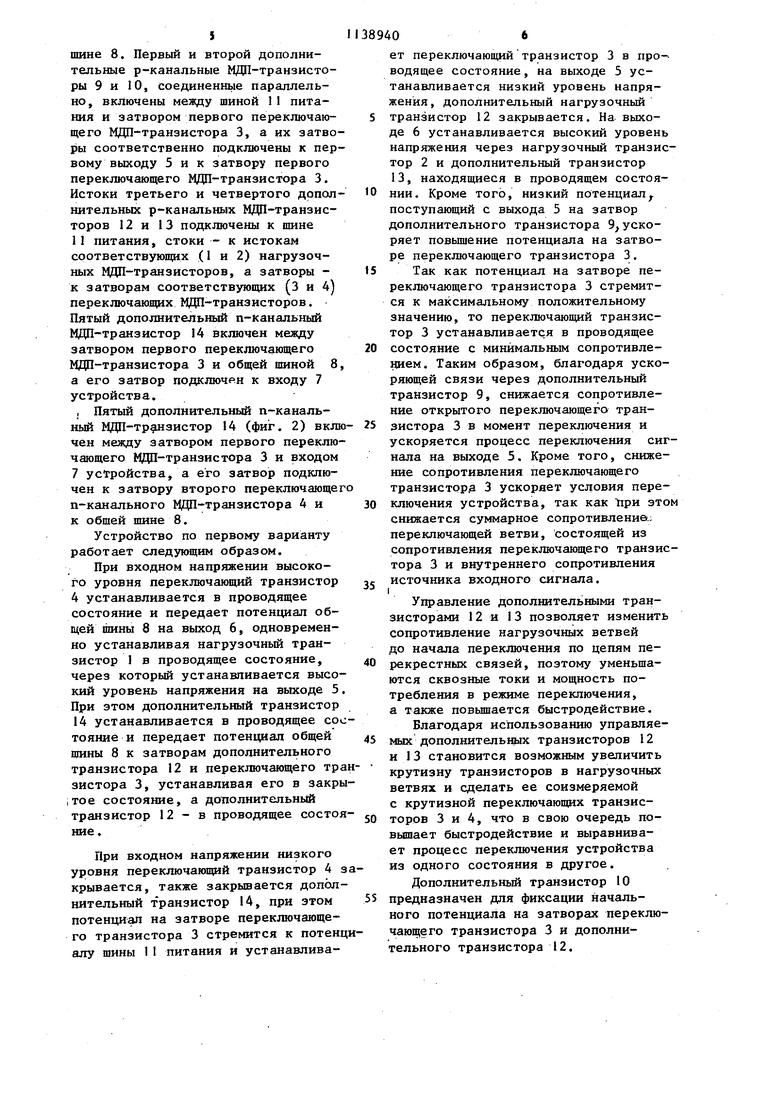

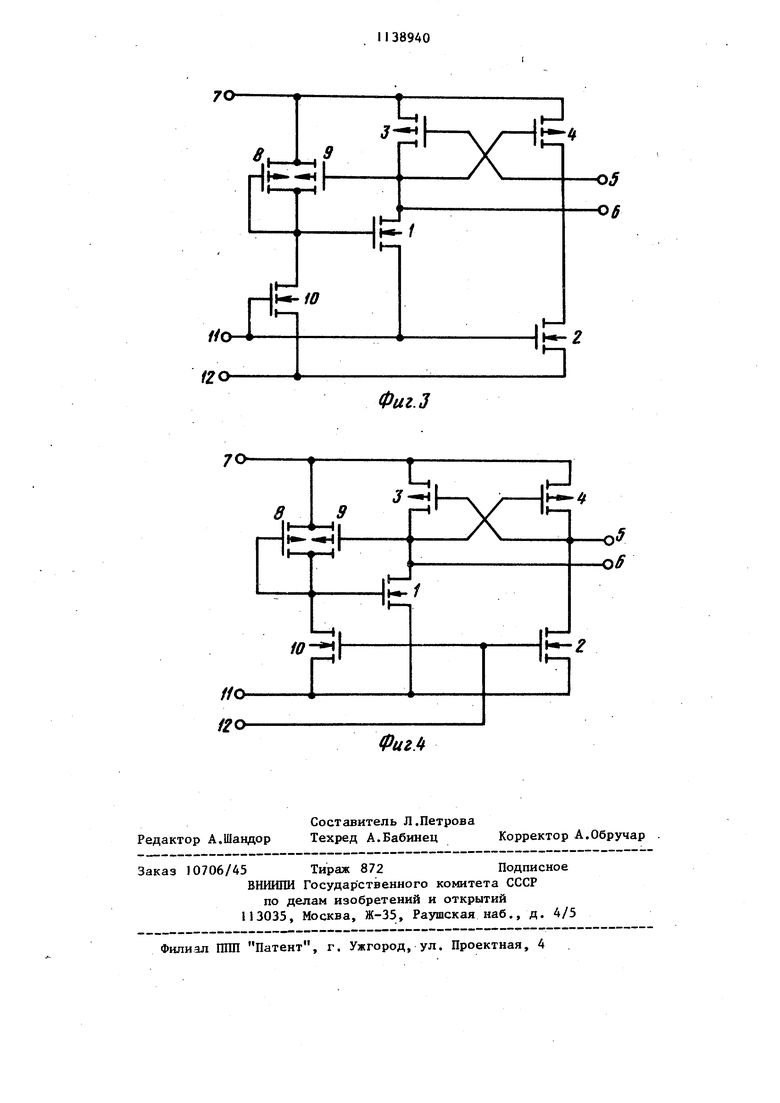

Изобретение относится к вычисли тельной технике и может быть испол зовано для построения устройств со гласования логических уровней ТТЛсхем с КМОП-схбмами, а также при переходе от логических уровней напряжений отрицательной полярности к напряжениям положительной полярности . Известно устройство согласования уровней, содержащее переключающие и нагрузочные транзисторы с перекрестными связями, а также дополнительный инвертор для согласования с однофазным сигналом ij . Недостатками этого устройства являются низкое быстродействие и большая потребляемая мощность в ре жиме переключения, а также необходимость использования дополнительных инвертора и источника питания для согласования с уровнями входного сигнала. Наиболее к изобретению по технической сущности является устройство согласования уровней напряжения, содержащее два р-канальных нагрузочных МДП-транзистора, затвор каждого из которых перекрестно подключен к стоку противоположного транзистора, и два п-канальных переключающих МДП-транзистора, сток каждого из которых подключен к стоку соответствующего нагрузочного МДП-транзистора и к соответствующему выходу устройства, исток первого переключающего МДП-транзистора подключен к входу устройства и к затвору второго переключающего МДП-транзистора, исток которого подключен к общей шине, истоки нагрузочных МДП транзисторов подключены к первой шине питания, а затвор первого переключающего МДП-транзистора - к второй шине питания 2 . Недостатками известного устройства являются низкое быстродействие, большая потребляемая мощность, а также необходимость двух шин питания с различными напряжениями. Цель изобретения - повьш1ение быстродействия и уменьшение потребляемой мощности. Цель достигается тем, что согласно первому варианту в устройство 3 согласования уровней напряжения, содержащее два р-канальных нагрузочных МДП-транзистора, затвор каждого из которых перекрестно подключен к стоку противоположного транзистора, и два п-канальных переключающих МДП-транзистора, сток каждого из которых подключен к сто ку соответствующего нагрузочного МДП-транзистора и к соответствующему выходу устройства, исток перво го переключающего МДП-транзистора подключен к входу устройства и к за твору второго переключающего МДПтранзистора, исток которогр подключен к общей шине, введены пять дополнительных МДП-транзисторов, первый и второй дополнительные р-канал ные МДП-транзисторы, соединенные параллельно, которые включены между шиной питания и затвором первого переключающего МДП-транзистора, а их затворы соответственно подключены к первому выходу устройства и к затвору первого переключающего МДПтранзистора, истоки третьего и четвертого дополнительных р-канал-ьных МДП-транзисторов подключены к шине питания, стоки - к истокам соответствующих нагрузочных МДП-транзисторов, а затворы - к затворам соответ ствующих переключающих МДП-транзисторов, пятый дополнительный п-канальный.МДП-транзистор включен между затвором первого переключающего МДП-транзистора и общей щиной, а его затвор подключен к входу устройства. Согласно второму варианту в устройство согласования уровней напряжения, содержащее два р-канальных нагрузочных МДП-транзистора, затвор каждого из которых перекрестно подключен к стоку противоположного тра зистора, и два п-канальных переключающих МДП-транзистора, сток каждого из которых подключен к стоку соответствующего нагрузочного МДПтранзистора и к соответствующему выходу устройства, а исток первого переключающего МДП-транзистора подключен к входу устройства, введены пять дополнительных МДП-транзисторов, первый и второй дополнительные р-канальные МДП-транзисторы, соединенные параллельно, которое включены между шиной питания и затвором первого переключающего МДП-тран 404 зистора, а их затворы, соответственно, подключены к первому выходу устройства и к затвору первого переключающего МДП-транзистора, истоки третьего и четвертого дополнительных р-канапьных МДП-транзисторов подключены к шине питания, стоки к истокам соответствующих нагрузочных МДП-транзисторов, а затворы к .затворам соответствующих переключающих МДП-транзисторов, пятый дополнительный п-канальный МДП-тр.анзистор включен между затвором первого переключающего МДП-транзистора и входом устройства, а его затвор подключен к затвору второго переключающего МДП-транзистора и к общей шине, исток второго переключающего МДП-транзистора подключен к входу устройства. На фиг, 1 представлена электричеокая принципиальная схема устройства согласования низких уровней напряжений положительной полярности с высокими уровнями положительной . полярности, например, ТТЛ-схем с КМОП-схемами (первый вариант); на фиг. 2 - электрическая принципиальная схема устройства согласоваНИН уровней напряжений отрицательной полярности с уровнями напряжений положительной полярности (вто- рой вариант); на фиг. 3 и 4 j электрические принципиальные схемы устройств согласования по первому и второму вариантам, соответственно в которых исключены третий и-четвертый дополнительные р-канальные МДП-транзисторы и истоки нагрузочных МДП-транзисторов непосредствеино подключены к шине питания. В электрической схеме устройства согласования уровней напряжения (фиг. 1) затвор каждого из двух, р-канальных нагрузочных МДП-транзисторов 1 и 2 перекрестно подключен к стоку противоположного транзистора , сток каждого из двух пканальных переключающих МДП-транзисторов 3 и 4 подключен к стоку соответствующего (I или 2) нагрузочного МДП-транзистора и к соответствующему (5 или 6) выходу устройства. Исток первого переключающего МДП-. транзистора 3 подключен к входу 7 устройства и к затвору второго переключающего МДП-транзистора 4, исток которого подключен к общей S тине 8. Первый и второй дополнительные р-канальные МДП-транзисторы 9 и 10, соединеннь1е параллельно, включены между шиной I1 питания и затвором первого переключающего МДП-транзистора 3, а их затво ры соответственно подключены к пер вому выходу 5 и к затвору первого переключающего МДП-транзистора 3. Истоки третьего и четвертого допол нительных р-канальных МДП-транзисторов 12 и 13 подключены к шине 11 питания, стоки - к истокам соответствующих (1 и 2) нагрузочных ЬЩП-транзисторов, а затворы к затворам соответствующих (З и 4) переключающих МДП-транзисторов. Пятый дополнительный п-канальный МДП-транзистор 14 включен между затвором первого переключающего МДП-транзистора 3 и общей шиной 8 а его затвор подключен к входу 7 устройства. , Пятый дополнительный п-канальиый МДП-тр нзистор 14 (фиг, 2) вкл чен между затвором первого переклю чающего МДП-транзистора 3 и входом 7 устройства, а его затвор подключен к затвору второго переключающе п-канального МЦП-транзистора 4 и к обшей шине 8. Устройство по первому варианту работает следующим образом. При входном напряжении высокого уровня переключающий транзистор 4 устанавливается в проводящее состояние и передает потенциал общей пшны 8 на выход 6, одновременно устанавливая нагрузочньй транзистор 1 в проводящее состояние, через который устанавливается высо кий уровень напряжения на выходе 5 При этом дополнительный транзистор 14 устанавливается в проводящее со тояние и передает потенциал общей шины 8 к затворам дополнительного транзистора 12 и переключающего тр зистора 3, устанавливая его в закр iToe состояние, а дополнительный транзистор 12 - в проводящее состо ние. При входном напряжении низкого уровня переключающий транзистор 4 крывается, также закрывается допол нительный транзистор 14, при этом потенциал на затворе переключающего транзистора 3 стремится к потен алу шины 11 питания и устанавлива06ет переключающий транзистор 3 в про-водящее состояние, на выходе 5 устанавливается низкий уровень напряжения , дополнительный нагрузочный транзистор 12 закрывается. На выходе 6 устанавливается высокий уровень напряжения через нагрузочный транзистор 2 и дополнительный транзистор 13, находящиеся в проводящем состояНИИ. Кроме того, низкий потенциал,. поступающий с выхода 5 на затвор дополнительного транзистора 9 ускоряет повышение потенциала на затворе переключающего транзистора 3. Так как потенциал на затворе переключающего транзистора 3 стремится к максимальному положительному значению, то переключающий транзистор 3 устанавливается в проводящее состояние с минймальньм сопротивлением. Таким образом, благодаря ускоряющей связи через дополнительный транзистор 9, снижается сопротивление открытого переключающего транзистора 3 в момент переключения и ускоряется процесс переключения сигнала на выходе 5. Кроме того, снижение сопротивления переключающего транзисторд 3 ускоряет условия переключения устройства, так как при этом снижается суммарное сопротивление ; переключающей ветви, состоящей из сопротивления переключающего транзистора 3 и внутреннего сопротивления источника входного сигнала, Управление дополнительными транзисторами 12 и 13 позволяет изменить сопротивление нагрузочных ветвей до начала переключения по цепям перекрестных связей, поэтому уменьшаются сквозные токи и мощность потребления в режиме переключения, а также повышается быстродействие. Благодаря использованию управляемых дополнительщих транзисторов 12 и 13 становится возможным увеличить крутизну транзисторов в нагрузочных ветвях и сделать ее соизмеряемой с крутизной переключающих транзисторов 3 и 4, что в свою очередь повышает быстродействие и выравнивает процесс переключения устройства из одного состояния в другое. Дополнительный транзистор 10 предназначен для фиксации начального потенциала на затворах переключающего транзистора 3 и дополниельного транзистора 12.

71

Устройство по второму варианту работает аналогичным образом.

При входном напряжении отрицательной полярности высокого уровня (отрицательная логика) переключение устройства происходит через цепь переключающего транзистора 4. При входном напряжении низкого уровня переключающий транзистор 4 и дополнительный транзистор 14 находятся в закрытом состоянии. При этом переключение устройства происходит через цепь переключающего транзистора 3, на затвор которого поступает потенциал шины 11 питания через дополнительный транзистор 10, а через дополнительный транзистор

1389408

9 ускоряется процесс установления этого потенциала, включение пере-г ключающего транзистора 3 и выключение дополнительного транзистора 12.

Таким образом, технико-экономический эффект заключается в повьшении быстродействия и уменьшении потребляемой мощности благодаря введению положительной обратной связи

на дополнительных транзисторах , а также благодаря введению дополнительных транзисторов, которые позволяют уменьшить мощность потребления, ускорить процесс переключения и повысить надежность в работе.

Фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3801831 , кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

Авторы

Даты

1985-02-07—Публикация

1983-10-10—Подача