го блока оперативной памяти и третье му входу ключа, третий вход вычислительного блока и третий вход блока управления являются управляющим входом устройства.

2. Устройство по п.1, о т л и чающееся тем, что вычислительный блок содержит буферный регистр, сумматоры, регистры, квадратор, вычитатели и перемножитель, выход первого су 1атора через первый регистр подключен к первому входу первого вычитателя, выход которого подключен к первому входу буферного регистра, первый выход которого подключен к первому входу перемножителя, выход которого подключен к первому входу второго сумматора, выход второго сумматора подключен к первому входу второго вычитателя, выход КОТОРОГО подключен к первому входу второго регистра, второй выход буферного регистра подключен к второму входу перемножителя и через квадратор к первому входу третьего сумматора, выход которого подключен к второму входу второго вычитателя объединенные первый вход первого сумматора и второй вход первого вычитателя являются первым входом вычислительного блока, объединенные вторые входы сумматоров и второй вход буферного регистра являются вторым входом вычислительного блока,объединенные третьи входы сумматоров и третий вход буферного регистра являются третьим входом вычислительного блока, выход регистра является выходом вычислительного блока.

9641

3. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, счетчики, триггеры, элементы И и элемент ИЛИ, выход генератора тактовых импульсов подключен к первым входам первого и втррого элемента И, выход первого элемента И подключен к первым входам третьего и четвертого элементов И, выходы которых через соответствующие счетчики подключены к первому и второму входу первого триггера, третий вход которого подключен к выходу элемента ИЛИ, первый и второй выходы первого триггера подключены к входам соответственно второго и третьего триггера, первый выход второго триггера подключен к второму входу первого элемента И и первым входам пятого и шестого элементов И, второй выход второго триггера подключен к второму входу второго элемента И и первым входам седьмого и восьмого элементов И, - первый выход третьего триггера подключен к второму входу третьего элемента И и вторым входам шестого и восьмого элементов И, второй выход третьего триггера подключен к второму входу четвертого элемента И и вторым входам пятого и седьмого элементов И, первый, второй и третий входы элементов ИЛИ являются соответственно первым, вторым и третьим входами блока управления, выход генератора тактовых импульсов, выходы шестого, пятого, восьмого, седьмого и второго элементов И являются соответственно первым - шестьпч выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

| Устройство для сжатия информации | 1983 |

|

SU1142855A1 |

| Устройство для обнаружения сигналов и измерения их параметров | 1987 |

|

SU1478145A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Устройство для сжатия информации | 1986 |

|

SU1365107A1 |

| Устройство для обнаружения движущихся объектов | 1989 |

|

SU1817256A2 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Устройство для кодирования сигналов звукового вещания | 1990 |

|

SU1774500A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

I. УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ТЕЛЕМЕТРИЧЕСКОЙ ИНФОРМАЦИИ, содержащее аналого-цифровой преобразователь, первый вход которого является информационным входом устройства, блок сравнения, выход которого подключен к первому входу счетчика блок управления, первый выход которого подключен к второму входу аналого-цифрового преобразователя, второй выход блока управления подключен к второму входу счетчика, первый блок оперативной памяти, отличающее с я тем, что, с целью повышения пропускной способности, в него введены буферные блоки памяти, блок ортогонального преобразования, вычислительный блок, второй блок оперативной памяти, квадратор, сумматор, вычитатель и ключ, выход аналого-цифрового преобразователя подключен к первому входу первого буферного блока памяти, выход которого подключен к первому входу второго блока оперативной памяти и первому входу блока вьмислительного блока, выход которого подключен к первому входу вычитателя, второй вход вычитателя подключен к выходу первого блока оперативной памяти, выход вычитателя подключен к первому входу блока сравнения, выход которого подключен к первому входу блока управления, первый выход второго блока оперативной памяти подключен к первому входу ключа, первый выход ключа подключен к первому входу квадратора, выход которого подключен к первому входу сумматора, выход сумматора подклю- чен к второму входу блока сравнения, второй выход ключа подключен к первому входу второго буферного блока памяти, выход которого является выходом устройства, второй вход второго буферного блока памяти подключен к первому выходу счетчика, второй выход которого подключен к второму входу блока управления, первый выход блока управления подключен к второму входу первого буферного блока памяти и второму входу квадратора, третий вькод блока управления подключен к третьему входу первого буферного блока памяти и второму входу второго блока оперативной памяти, второй выход и третий вход которого подключены соответственно к первому входу и выходу блока ортогонального преобразования, третий вход которого подключен к четвертому выходу блока управления, пчтый выход блока управления подключен к четвертому входу второго блока оперативной памяти, второму входу вычислительного блока, второму входу сумматора, второму входу ключа и третьему входу второго буферного блока памяти, шестой выход блока управления подключен к пятому входу второ

Изобретение относится к устройствам связи и может быть использовано в системах телеметрических данных.

Известно устройство передачи телеметрической информации, состоящее на передающей стороне из последовательно соединенных датчиков, блока прямого ортогонального преобразователя Уолша, коммутатора, аналого-цифрового преобразователя, блока считываиия и передатчика. Приемная сторона состоит из блока промежуточной памяти, цифро-аналогового преобразователя, дешифратора адреса и блока обратного ортогонального преобразователя Уолша ij .

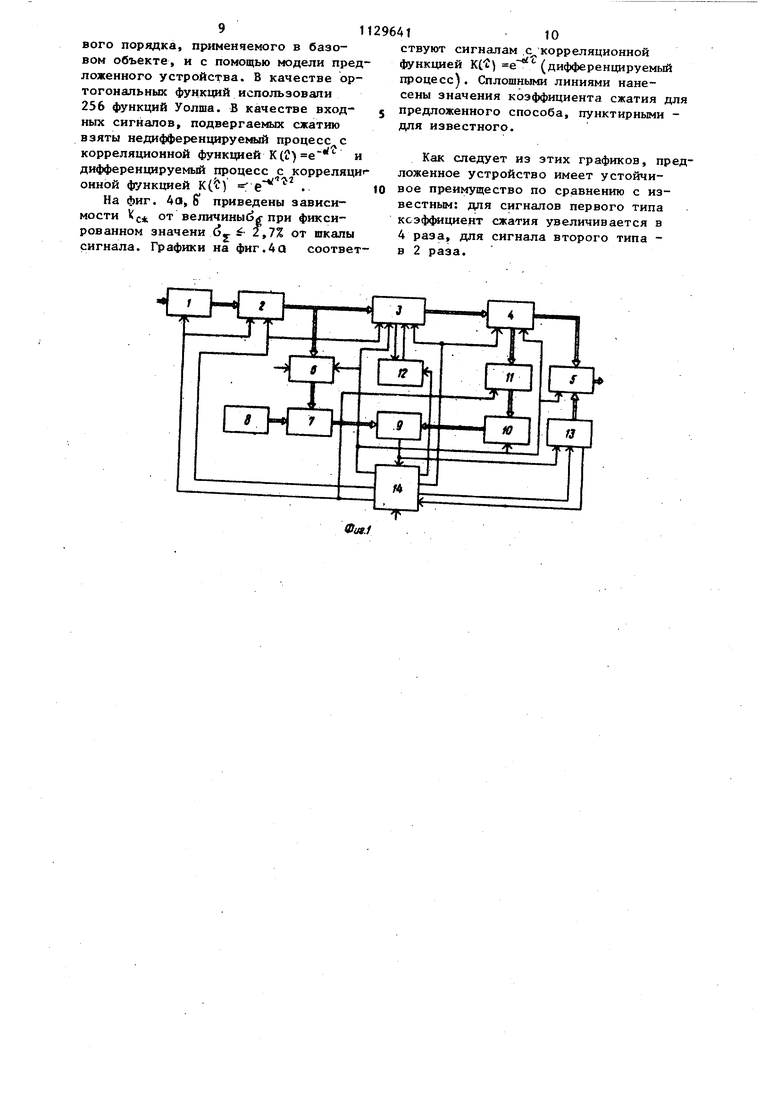

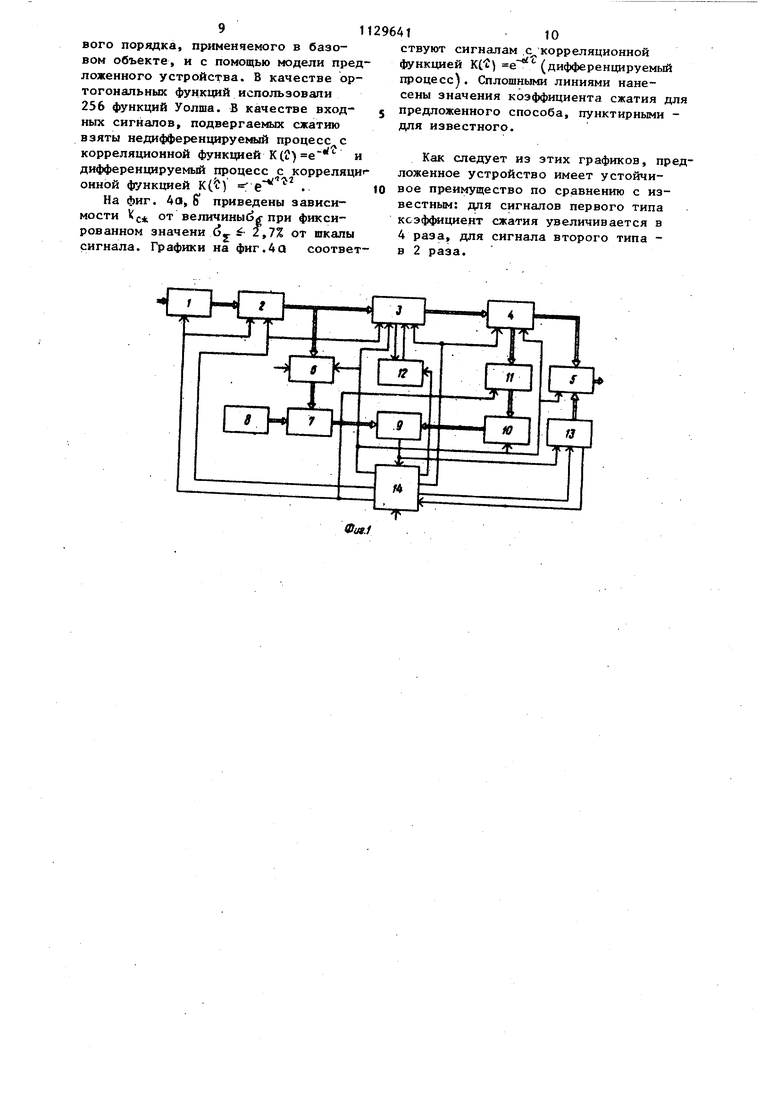

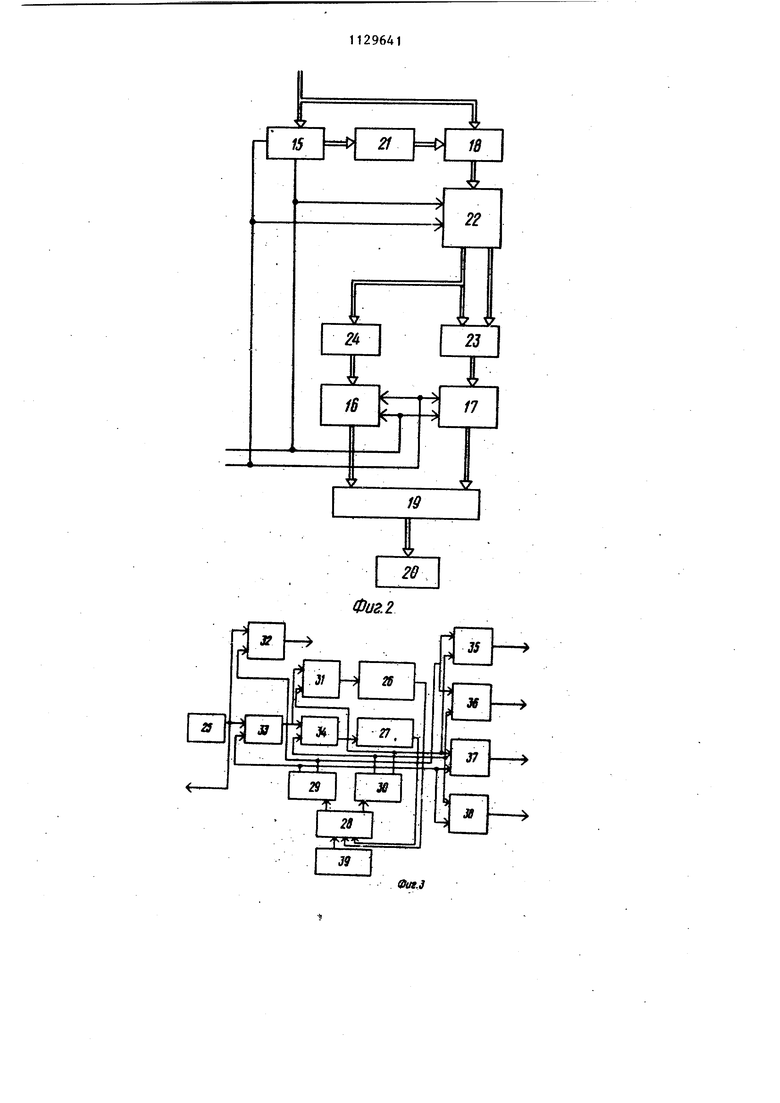

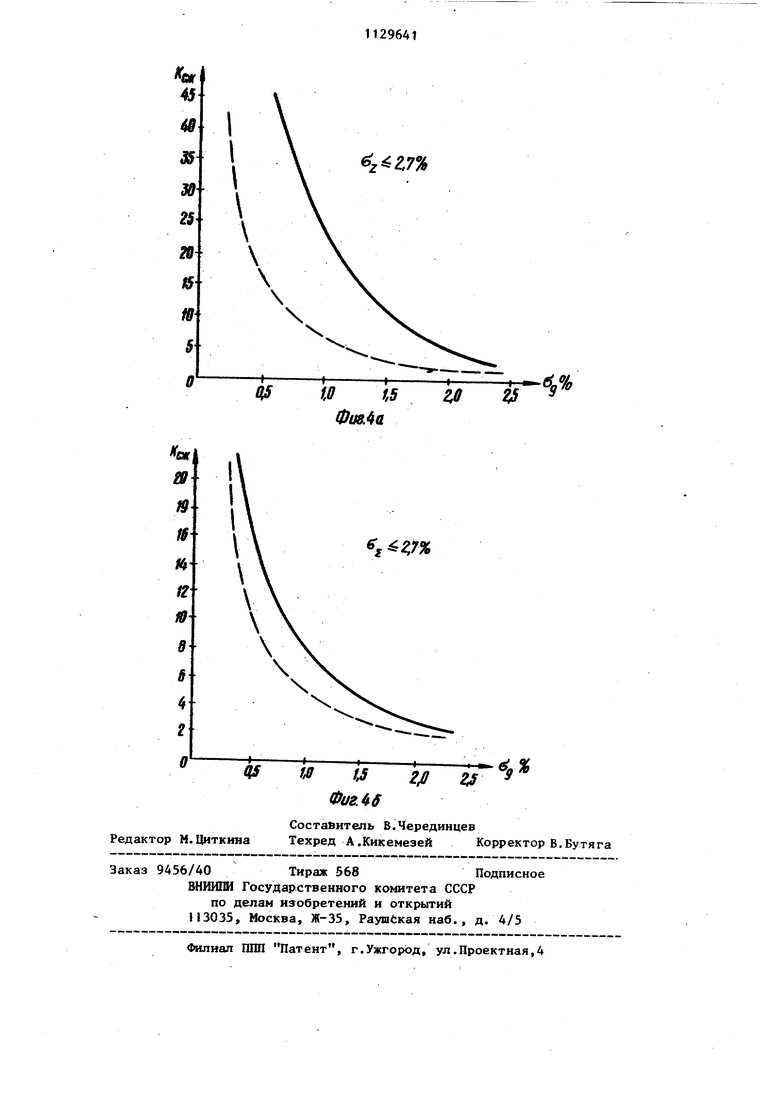

Недостаток этого устройства - избыточность передаваемых данных, так как количество передаваемых сигналов спектральных компонент постоянно и не Зависит от динамичности исходного процесса. Наиболее близким к предлагаемому является устройство для передачи телеметрической информации содержаще последовательно соединенные коммутатор, аналого-цифровой преобразоваталь и блок считывания, выходы аналого-цифрового преобразователя подключены к первым входам схемы сравнения, а также через блок памяти к вторым входам схемы сравнения, выход которой через счетчик подключен к вторым входам блока считывания.и первому входу блока управления, выход которого подключен к второму входу аналого-цифрового преобразователя и cxeNbi запуска, выход которой подключен к вторым входам коммутатора и блока памяти, вторые выходы блока считывания и схемы сравнения подключены соответственно к второму и третьему входам схемы запуска 2 Недостаток известного устройства малая пропускная способность,обусловленная избыточностью передаваемых данных. Целью изобре.тения является, повышение пропускной способности устройства. Поставленная цель достигается тем, что в устройство, содержащее аналого-цифровой преобразователь, первый выход которого является информационным входомчустройства, блок сравнения, выход которого подключен к первому входу счетчика, блок управления, первый выход которого подключен к второму входу аналого-1лифрового преобразователя, вто рой выход блока управления подключе к второму входу счетчика, первый блок оперативной памяти, введены буферные блоки памяти, блок ортоГог нального преобразования, вьтчислительный блок, второй блок оперативной памяти, квадратор, сумматор, вычитатель и ключ, выход аналого-цифрового преобразователя подключен к первому входу первого буферного блока памяти, выход которого подключен к первому входу второго блока оперативной памяти и первому входу , блока вычислительного блока, выход которого подключен к первому входу вычитателя, второй вход вычитателя подключен к выходу первого блока оперативной памяти, выход вычитателя подключен к первому вход блока сравнения, выход которого подключен к первому входу блока управления, первый выход второго блока оперативной памяти подключен к первому входу ключа, первый выход ключа подключей к первому входу квадратора, выход которого подключен к первому входу сумматора, выход сумматора подклочен к второму входу блока сравнения, второй выход ключа подключен к первому входу второго буферного блоблока памяти, выход которого является выходом устройства, второй вход второго буферного блока памяти подключен к первому выходу счетчика, второй выход которого подключен к второму входу блока управления, первый выход блока управления подключен к второму входу первого буферного . блока памяти и второму входу квадратора, третий выход блока управления подключен к третьему входу первого буферного блока памяти и второму входу второго блока оперативной памяти, второй выход и третий вход которого подключены соответственно к первому входу и выходу блока ортогонального преобразования, третий вход которого подключен к четвертому выходу блока управления, пятый выход блока управления под1 лючен к четвертому входу второго блока оперативной памяти, второму входу вычислительного блока, второму входу сумматора, второму входу ключа и третьему входу второго буферного блока памяти, шестой выход блока управления подключен к пятому входу второго блока оперативной памяти и третьему входу ключа, третий вход вычислительного блока и третий вход блока управления являются управляющим входом устройства. При этом в вычислительный блок введены буферный регистр, сумматоры, регистры, квадратор, вычитатели и перемножитель, выход первого сумматора через первый регистр подключен к первому входу первого вычитателя, выход которого подключен к первому входу первого буферного регистра, первый выход.которого подключен к первому входу перемножителя, выход которого подключен к первому входу второго сумматора, выход второго сумматора подключен к первому входу второго вычитателя, выход которого подключен к первому входу второго регистра, вто5рой выход буферного регистра подключён к второму входу перемножителя и через квадратор к первому вх ду третьего сумматора, выход которого подключен к второму входу второго вычитатепя, объединенные первый вход первого сумматора и второй вход первого вычитателя являются первым входом вычислительного блока объединенные вторые входы сумматоров и второй вход буферного регистра являются вторьм входом вычислительного блока, объединенные третьи входы сумматоров и третий вход буферного регистра являются третьим входом вычислительного блока, выход регистра является выходом вычислительного блока. Кроме того, в блок управления введены генератор тактовых импульсов, счетчики, триггеры, элементы И и элемент ИЛИ, выход генератора тактовых импульсов подключен к первым входам первого и второго элемен та И, выход первого элемента И подключен к первым входам третьего и четвертого элементов И, выходы которых через соответствующие счетчики подключены к первому и второму входу первого триггера, третий вход которюго подключен к выходу элемента ИЛИ, первый и второй выходы первого триггера подклихчеиы к входам соответственно второго и третьего триггера, первый выход второго триг гера подключен к второму входу первого элемента И и первым входам пятого и шестого элементов И, второй выход второго триггера подключен к второму входу второго элемента И и первым входам седьмого и восьмого элементов И, первый выход третьего триггера подключен к второму входу третьего элемента И и вторым входам шестого и jBocbMoro элементов И, вто рой выход третьего триггера подклкг чен к второму входу четвертого элемента И и вторым входам пятого и седьмого элементов И, первый, второй и третий входы элементов ИЖ являются соответственно первым, вто рым и третьим входами блока управле ния, выход генератора тактовых импульсов, выходы шестого, пятого, восьмого, седьмого и второго элемен тов И являются соответственно первым - шестым выходами блока управления. 4J6 На фиг.1 изображена структурная схема устройства для передачи телеметрической информации; на фиг.2 схема вычислительного блока; на фи/ фиг. 3 - схема блока управления; на фиг. 4 - зависимости коэффициентов сжатия Устройство содержит аналого-цифровой преобразователь (.ЩЩ) 1 , буферный блок 2 памяти, блок 3 оперативной памяти, ключ 4, буферный блок 5 памяти, вычислительный блок 6, вьгчитатель 7, блок 8 оперативной памяти, блок 9 сравнения, сумматор 10, квадратор П, блок 12 ортогонального преобразования, счетчик 13, блок 14 управления, сумматоры 1517, вычитатели I8 и 19, регистры 20 и 21, буферный регистр 22, перемножитель 23, кгадратор 24, генератор 25 тактовых импульсов, счетчики 26 VI 21 триггеры 28 - 30, элементы 31 38 И и элемент 39 ИЛИ. Вычислительный блок 6 ошибки дискретизации состоит из последовательно соединенных сумматора 15. регистра 21 сдвига, вычитателя 18, буферного регистра 22, перемножителя 23, второго накапливающего сумматора 17, второго вычитателя 19, вькодного регистра 20 и последовательно соединенных квадратора 24 и третьего накапливающего сумматора 16. Выход сумматора 16 соединен с другим входом второго вычитателя 19, вход квадратора 24 подключен к другому выходу буферного регистра и другому входу перемножителя 3, вход первого накапливающего сумматора 15 соединен с другим входом вычитателя 8, причем управляющие входы накапливающих сумматоров 15 - 17 и буферного регистра соединены с соответствующими входами блока управления. Структура приемного устройства определяется форматом передаваемого группового сигнала. Приемное устройство состоит из приемника, буферного запоминающего устройства и обратного ортогонального преобразелштеля. Предложенное устройство работает следующим обра.зом. Перед нач.алом работы сигнал.ом Сброс от синхронизатора производят установку нулевых начальных условий в буферных запоминающих устройствах, оперативном запоминающем устройстве, блоке вычисления ошибки дискретизации, накапливакяцем сумматоре и реверсивном счетчике. Затем на вход аналого-цифрового преобразователя (АЦП) 1 подают выборки непрерьшного случайного процесса x(t) . На выход АЦП частотой тактирующих импульсов поступающих с синхронизатора, получают N цифровых отсчетов сигнала XJ в виде параллельного кода. Шаг дискретизации выбирают, исходя из максимальной ожидаемой частоты в спектре сигнала. N цифровых отсчетов сигнала записывают в буферный блок 2 памяти, откуда по сигналу считывания от синхронизатора передают в ортогональный преобразователь, где определяют Ц сигналов ортогональных спектральных компонент Со , С,, . . .., С и В блоке 3 оперативной памяти эти сигналы запоминают и через двухпозиционный ключ 4 передают либо в квадратор 11 (первое, положение ключа 4), либо в буферный блок 5 памяти. С выхода бу ферного блока 2 памяти цифровые отсчеты сигнала XJ.подают также на вычислительньш блок 6 ошибки дискретизации, на выходе которого сигнал пропорционален квадрату текущей ошибки дискретизации б1 : , где (j д - дисперсия сигнала; R(A) - значение нормированной кор реляционной функции сигнала при зна чении аргумента, равном шагу дискре тизации U . На вычитатель 7 подают сигнал б полной допустимой ошибки восст новления от блока 8 оперативной пам ти, выполненного в виде клавишного запоминающего устройства, и d3- - с нал текущей ошибки дискретизации от вычислительного блока 6 ошибки дискретизации. На выходе вычитателя 7 получают сигнал, пропорциональный квадрату допустимой ошибки преобразования. Этот сигнал б подают на вход бло ка 9 сравнения, на другой вход кото рого поступают текущие суммы квадраторов сигналов спектральнь1х компонент Cj, полученных после прохождения сигнала Cj через ключ 4, квадратор 11 и накапливающий сумматор 10. Сравнение сигнала допустимой ошибки преобразования б о с j в блоке 9 сравнения сигналом Z С проводят до тех пор, пока не будет вьшолняться условие N-M 2 1 .5: cb.cin. После этого ключ 4 переключают на второй выход - к буферному блоку 5 памяти - сигналом управления блока 14 управления и на выходе реверсивного счетчика 13, соединенном с входом буферного блока 5 памяти, получают сигнал пропорциональный числу (N-M+I) существенных спектральных компонент. С выхода блока сравнения 9 получают сигнал, поступающий на блок 14 управления, где вырабатывают сигналы считывания (N-M+1) первых сигналов спектральных компонент из блока 3 опера-пивной памяти и передачи их через ключ 4 в буферный блок 5 памяти. В канал .связи передают групповой сигнал, состоящий из сигнала числа (N-M+l) и сигналов (N-M+I) спектральных компонент, После записи сигналов (N-M+1) спектральных компонент в буферный блок 5 памяти реверсивный счетчик 13 обнуляют сигналом из блока 14 управления. Затем начинается цикл обработки следующей реализации. Сигналом начала следукмцего цикла является сигнал, приходящий с реверсивного счетчика на блок 14 управления. В качестве базового объекта взято устройство передачи данных 3j , предназначенное для использования на борту космического корабля. Это устройство реализует способ сокращения избыточности на предсказателе нулевого порядка. Технико-экономическая эффективность предложенного технического решения по отношению к известному оценивается значениями их коэффициентов сжатия G где N - количество передаваемых данных без сокращения избыточности; N-M - количество передаваемых данных при сокращении избыточности. Для сопоставления проведен расчетный эксперимент. С помощью ЭВМ генерировался -случайный сигнал с заданными корреляционными и динамическими свойствами. Этот сигнал подвергали сжатию с помощью интерполятора кулевого порядка, пряменчемого в базовом объекте, и с помощью модели предложенного устройства. В качестве ортогональных функций использовали 256 функций Уолша, В качестве входных сигналов, подвергаемых сжатию взяты недифференцируемый процесс с корреляционной функцией K()е и дифференцируемый процесс с корреляциг онной функцией К(«) Г е На фиг. 40, приведены зависимости Vr от величиныdtf при фиксированном значени dj. f.7% от шкалы сигнала. Графики на фиг.4а соответ 11 1 ствуют сигналам .с корреляционной функцией КС) (дифференцируемый процесс). Сплошными линиями нанесены значения коэффициента сжатия для предложенного способа, пунктирными для известного. Как следует из этих графиков, предложенное устройство имеет устойчивое преимущество по сравнению с известным: для сигналов первого типа ксэф4«циент сжатия увеличивается в 4 раза, для сигнала второго типа в 2 раза.

IJ

0aeJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Телеизмерительная система | 1979 |

|

SU805380A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Адаптивные телеизмерительные системы | |||

| Энергоиздат, 1981, с | |||

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| : | |||

Авторы

Даты

1984-12-15—Публикация

1983-08-03—Подача