Изобретение относится к области связи и может быть применено для согласования работы многоканального приемника с удаленными передатчикам

Цепью изобретения является повышение достоверности.

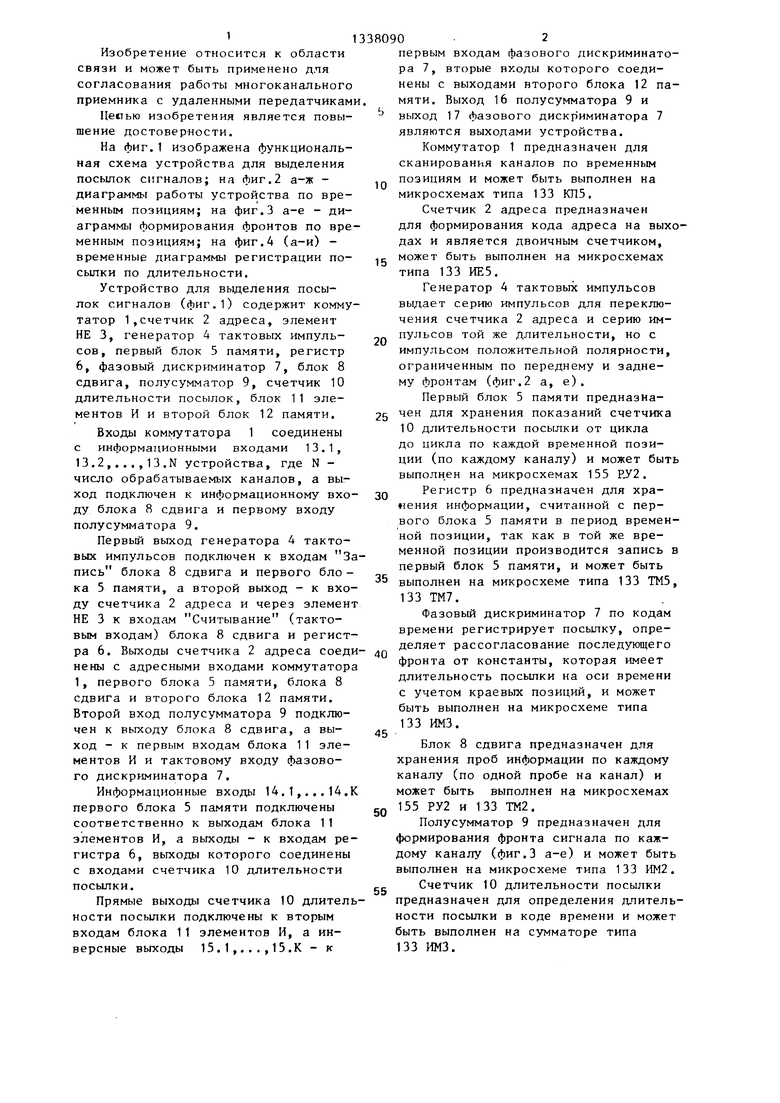

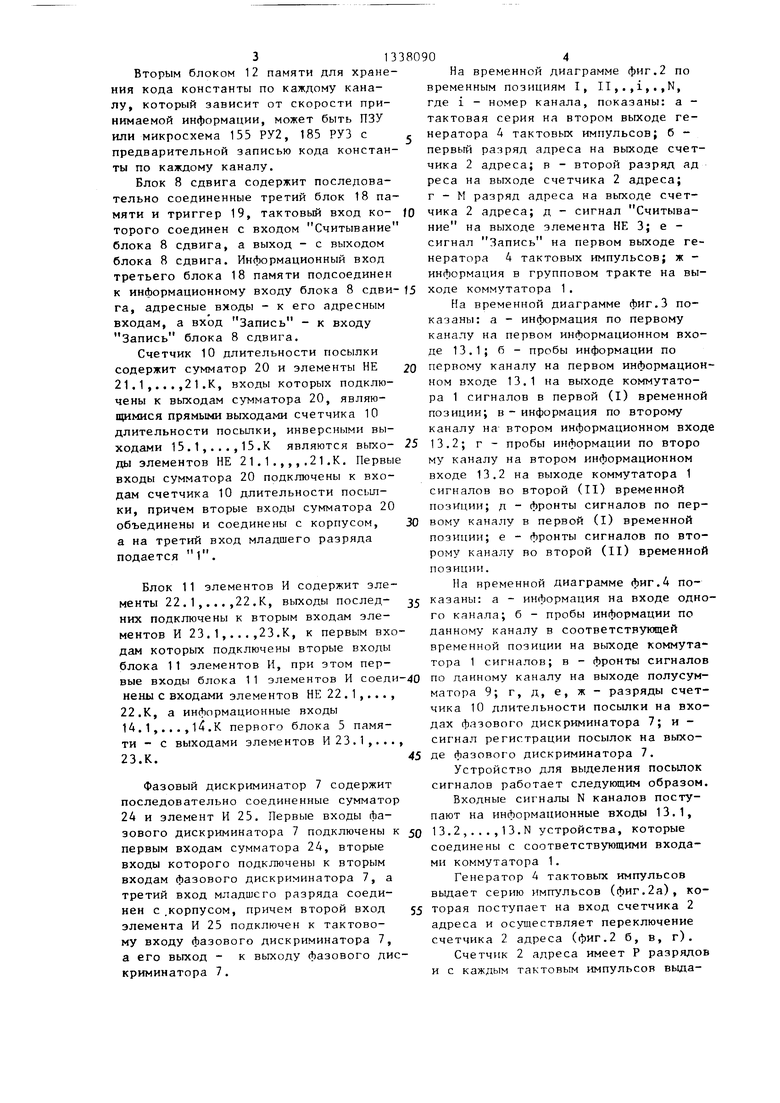

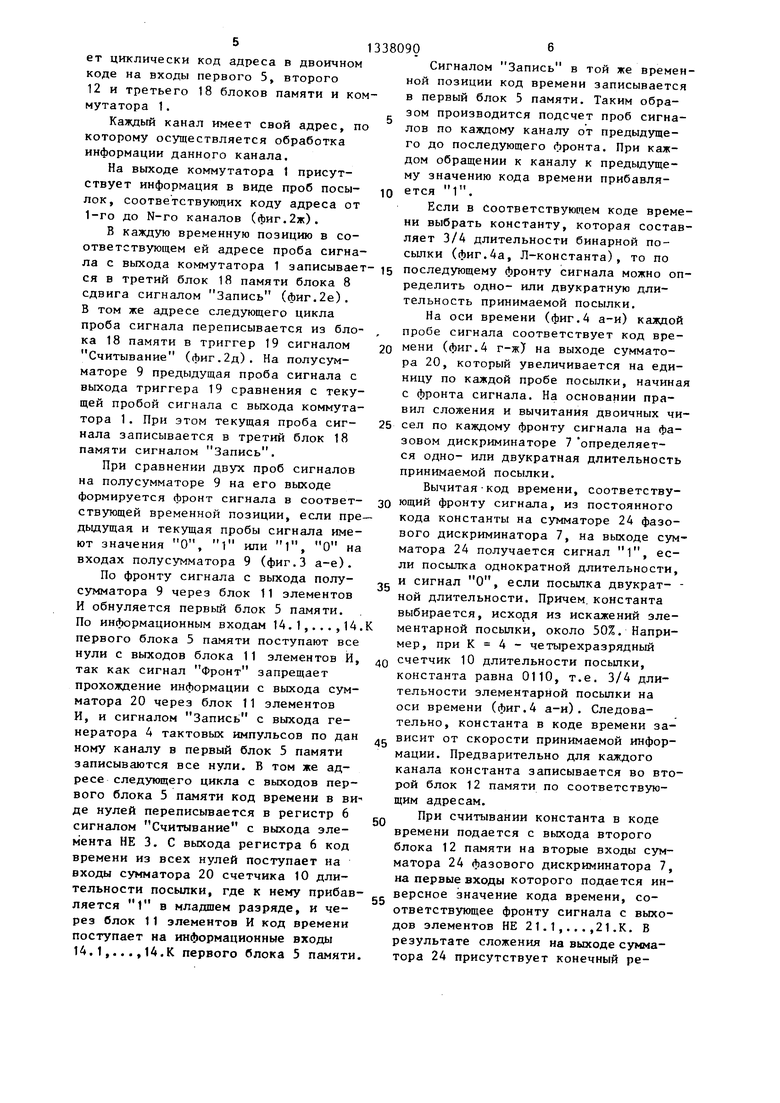

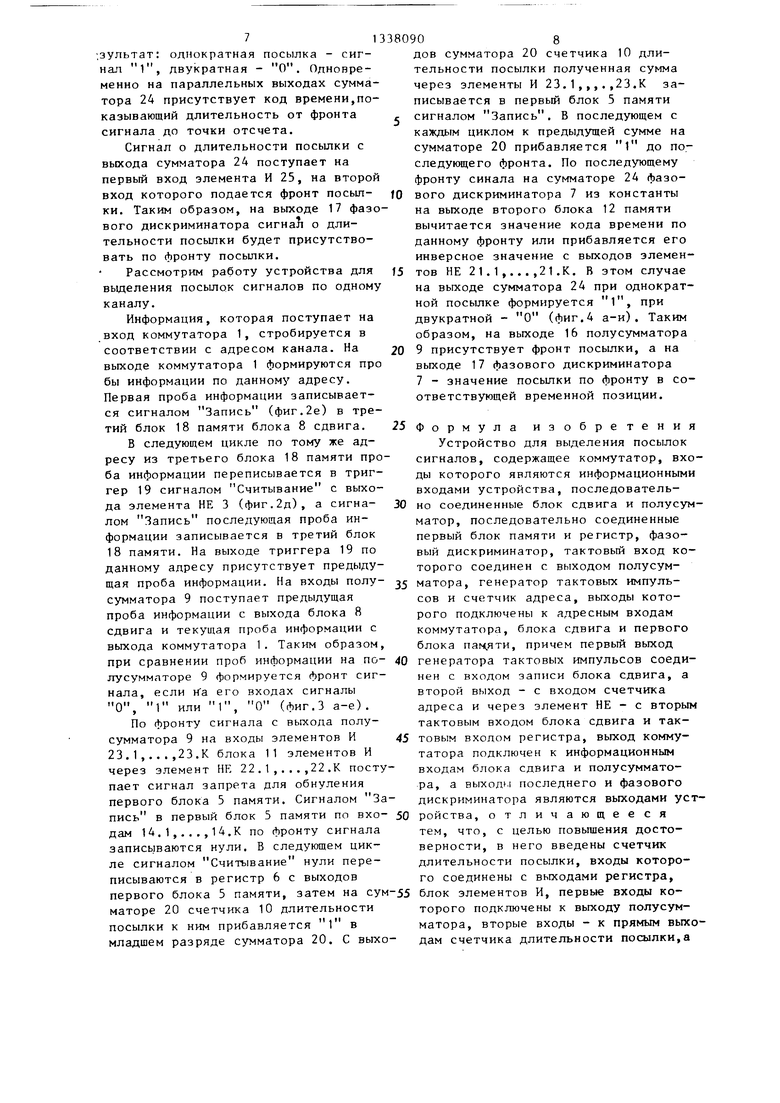

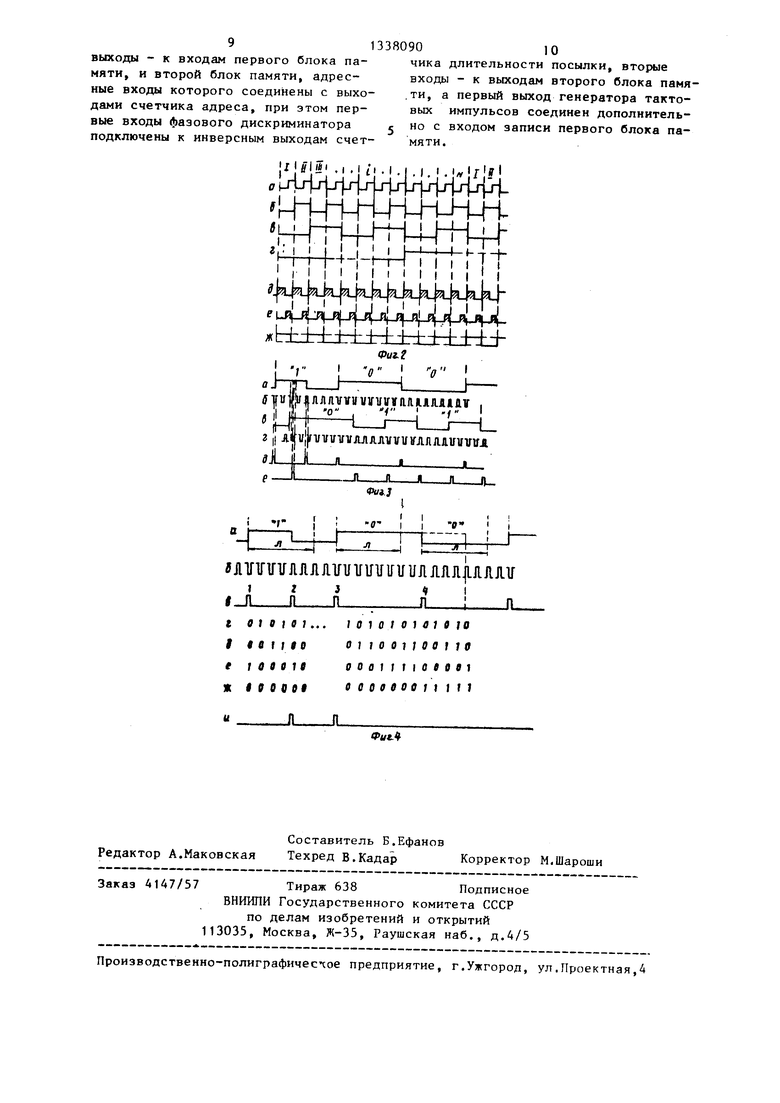

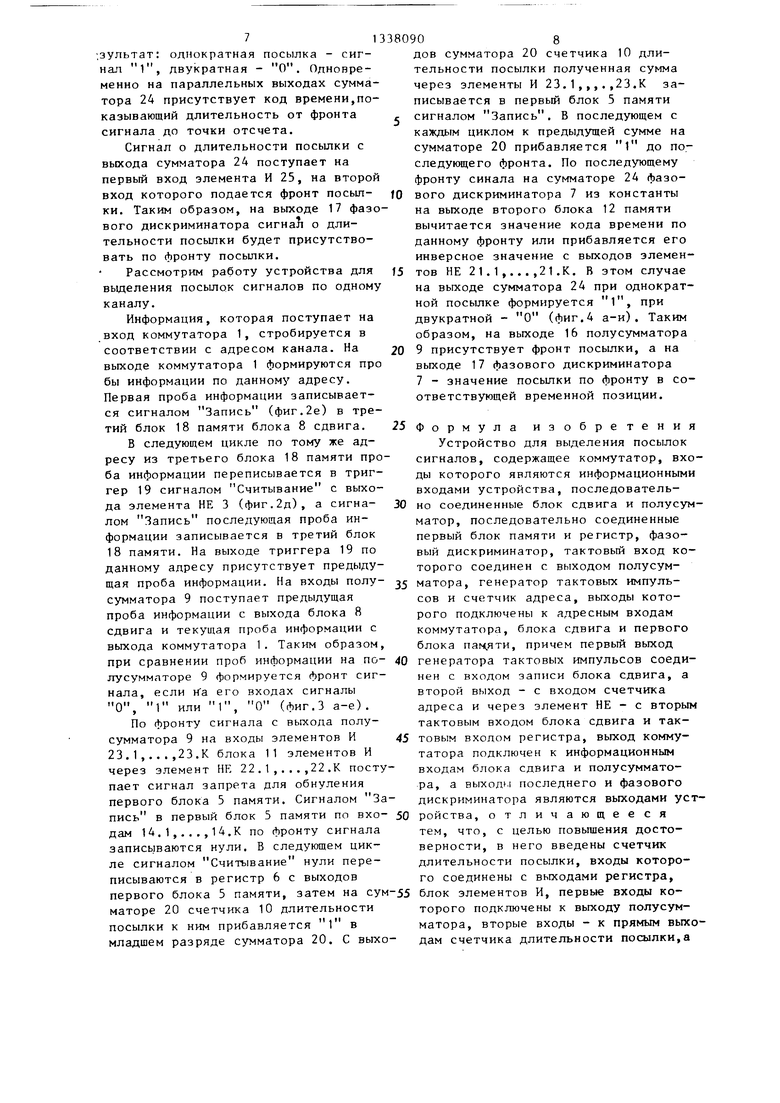

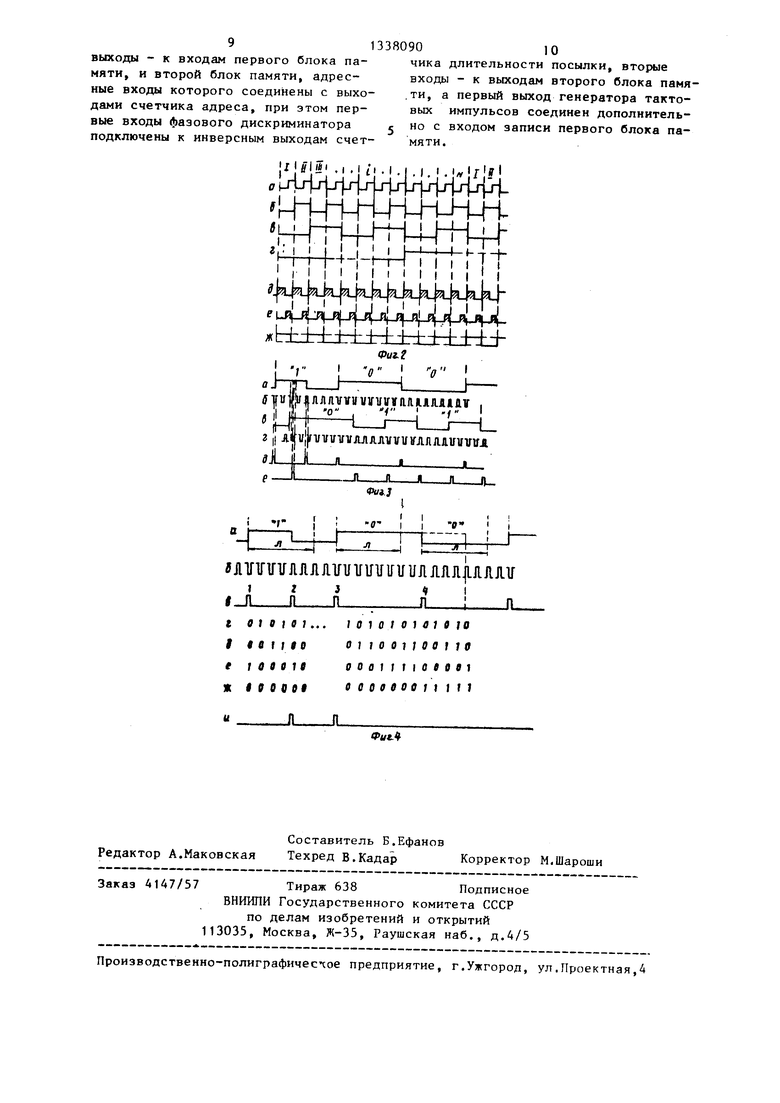

На фиг.1 изображена функциональная схема устройства для выделения посылок сигналов; на фиг.2 а-ж - диаграммы работы устройства по временным позициям; на фиг.З а-е - диаграммы формирования фронтов по временным позициям; на фиг.4 (а-и) - временные диаграммы регистрации посылки по длительности.

Устройство для выделения посылок сигналов (фиг.1) содержит коммутатор 1,счетчик 2 адреса, элемент НЕ 3, генератор 4 тактовых импульсов, первый блок 5 памяти, регистр 6, фазовый дискр1-гминатор 7, блок 8 сдвига, полусумматор 9, счетчик 10 длительности посылок, блок 11 элементов И и второй блок 12 памяти.

Входы коммутатора 1 соединены с информационными входами 13.1, 13.2,...,13.N устройства, где N - число обрабатываемых каналов, а выход подключен к информационному входу блока 8 сдвига и первому входу полусумматора 9.

Первый выход генератора 4 тактовых импульсов подключен к входам Запись блока 8 сдвига и первого бло - ка 5 памяти, а второй выход - к входу счетчика 2 адреса и через элемент НЕ 3 к входам Считывание (тактовым входам) блока 8 сдвига и регистра 6. Выходы счетчика 2 адреса соединены с адресными входами коммутатора 1, первого блока 5 памяти, блока 8 сдвига и второго блока 12 памяти. Второй вход полусумматора 9 подключен к выходу блока 8 сдвига, а выход - к первым входам блока 11 элементов И и тактовому входу фазового дискриминатора 7.

Информационные входы 14.1,...14.К первого блока 5 памяти подключены соответственно к выходам блока 11 элементов И, а выходы - к входам регистра 6, выходы которого соединены с входами счетчика 10 длительности посылки.

Прямые выходы счетчика 10 длительности посылки подключены к вторым входам блока 11 элементов И, а инверсные выходы 15.1,...,15.К - к

0

5

0

5

0

5

0

5

0

5

первым входам фазового дискриминатора 7, вторые входы которого соединены с выходами второго блока 12 памяти. Выход 16 полусумматора 9 и выход 17 фазового дискриминатора 7 являются выходами устройства.

Коммутатор 1 предназначен для сканирования каналов по временным позициям и может быть выполнен на микросхемах типа 133 КП5.

Счетчик 2 адреса предназначен для формирования кода адреса на выходах и является двоичным счетчиком, может быть выполнен на микросхемах типа 133 ИЕ5.

Генератор 4 тактовых импульсов выдает серию импульсов для переключения счетчика 2 адреса и серию импульсов той же длительности, но с импульсом положительной полярности, ограниченным по переднему и заднему фронтам (фиг.2 а, е).

Первый блок 5 памяти предназначен для хранения показаний счетчика 10 длительности посылки от цикла до цикла по каждой временной позиции (по каждому каналу) и может быть выполнен на микросхемах 155 Р.У2.

Регистр 6 предназначен для хранения информации, считанной с первого блока 5 памяти в период временной позиции, так как в той же временной позиции производится запись в первый блок 5 памяти, и может быть выполнен на микросхеме типа 133 ТМ5, 133 ТМ7.

Фазовый дискриминатор 7 по кодам времени регистрирует посылку, определяет рассогласование последующего фронта от константы, которая имеет длительность посылки на оси времени с учетом краевых позиций, и может быть выполнен на микросхеме типа 133 ИМЗ.

Блок 8 сдвига предназначен для хранения проб информации по каждому каналу (по одной пробе на канал) и может быть выполнен на микросхемах 155 РУ2 и 133 ТМ2.

Полусумматор 9 предназначен для формирования фронта сигнала по каждому каналу (фиг.З а-е) и может быть выполнен на микросхеме типа 133 ИМ2.

Счетчик 10 длительности посылки предназначен для определения длительности посылки в коде времени и может быть выполнен на сумматоре типа 133 ИМЗ.

Вторым блоком 12 памяти для хранения кода константы по каждому каналу, который зависит от скорости принимаемой информации, может быть ПЗУ или микросхема 155 РУ2, 185 РУЗ с предварительной записью кода константы по каждому каналу.

Блок 8 сдвига содержит последовательно соединенные третий блок 18 памяти и триггер 19, тактовый вход ко- торого соединен с входом Считывание блока 8 сдвига, а выход - с выходом блока 8 сдвига. Информационный вход третьего блока 18 памяти подсоединен

к информационному входу блока 8 сдви- 15 ходе коммутатора 1.

га, адресные входы - к его адресным входам, а вход Запись - к входу Запись блока 8 сдвига.

Счетчик 10 длительности посылки содержит сумматор 20 и элементы НЕ 21.1,..,,21.К, входы которых подключены к выходам сумматора 20, являющимися прямыми выходами счетчика 10 длительности посылки, инверсными выходами 15.1,...,15.К являются выхо- 25 13.2; г - пробы информации по второ ды элементов НЕ 2 1.1 .,,, .21.К. Первые му каналу на втором информационном входы сумматора 20 подключены к входам счетчика 10 длительности посылки, причем вторые входы сумматора 20

30

объединены и соединены с корпусом, а на третий вход младшего разряда подается 1.

Блок 11 элементов И содержит элевходе 13.2 на выходе коммутатора 1 сигналов во второй (II) временной позиции; д - фронты сигналов по первому каналу в первой (I) временной позиции; е - фронты сигналов по второму каналу во второй (II) временной позиции.

На временной диаграмме фиг.4 по- менты 22.1,...,22.К, выходы послед- 35 казаны: а - информация на входе одно- них подключены к вторым входам эле- го канала; б - пробы информации по ментов И 23.1,...,23.К, к первым вхо- данному каналу в соответствующей дам которых подключены вторые входы временной позиции на выходе коммута- блока 11 элементов И, при этом пер- тора 1 сигналов; в - фронты сигналов вые входы блока 11 элементов И соеди-40 по данному каналу на выходе полусумнены С входами элементов НЕ 22.1 матора 9; г, д, е, ж - разряды счет22.К, а информационные входы 14.1,...,14.К первого блока 5 памяти - с выходами элементов И 23.1,..., 23.К.

чика 10 длительности посылки на входах фазового дискриминатора 7; и - сигнал регистрации посылок на выхо- 45 де фазового дискриминатора 7.

Устройство для выделения посылок

Фазовый дискриминатор 7 содержит сигналов работает следующим образом, последовательно соединенные сумматор Входные сигналы N каналов посту- 24 и элемент И 25. Первые входы фа- пают на информационные входы 13.1, эового дискриминатора 7 подключены к fO 13.2,...,13.N устройства, которые

первым входам сумматора 24, вторые входы которого подключены к вторым входам фазового дискриминатора 7, а третий вход младшего разряда соединен с .корпусом, причем второй вход элемента И 25 подключен к тактовому входу фазового дискриминатора 7, а его выход - к выходу фазового дискриминатора 7.

На временной диаграмме фиг.2 по временным позициям I, II,.,i,.,N, где i - номер канала, показаны: а - тактовая серия на втором выходе генератора 4 тактовых импульсов; б - первый разряд адреса на выходе счетчика 2 адреса; в - второй разряд ад реса на выходе счетчика 2 адреса; г - М разряд адреса на выходе счетчика 2 адреса; д - сигнал Считывание на выходе элемента НЕ 3; е - сигнал Запись на первом выходе генератора 4 тактовых импульсов; ж - информация в групповом тракте на выНа временной диаграмме фиг.З показаны: а - информация по первому каналу на первом информационном входе 13.1; б - пробы информации по первому каналу на первом информационном входе 13.1 на выходе коммутатора 1 сигналов в первой (I) временной позиции; в - информация по второму каналу на втором информационном входе

соединены с соответствующими входами коммутатора 1.

Генератор 4 тактовых импульсов выдает серию импульсов (фиг.2а), ко- 55 торая поступает на вход счетчика 2 адреса и осуществляет переключение счетчика 2 адреса (фиг.2 б, в, г).

Счетчик 2 адреса имеет Р разрядов и с каждым тактовым импульсов выда51

ет циклически код адреса в двоичном коде на входы первого 5, второго 12 и третьего 18 блоков памяти и коммутатора 1.

Каждый канал имеет свой адрес, по которому осуществляется обработка информации данного канала.

На выходе коммутатора 1 присутствует информация в виде проб посылок, соответствующих коду адреса от 1-го до N-ro каналов (фиг.2ж).

В каждую временную позицию в соответствующем ей адресе проба сигнала с выхода коммутатора 1 записывается в третий блок 18 памяти блока В сдвига сигналом Запись (фиг.2е). В том же адресе следующего цикла проба сигнала переписывается из блока 18 памяти в триггер 19 сигналом Считывание (фиг.2д). На полусумматоре 9 предыдущая проба сигнала с выхода триггера 19 сравнения с текущей пробой сигнала с выхода коммутатора 1. При этом текущая проба сигнала записывается в третий блок 18 памяти сигналом Запись.

При сравнении двух проб сигналов на полусумматоре 9 на его выходе формируется фронт сигнала в соответствующей временной позиции, если предыдущая и текущая пробы сигнала имеют значения О, l ипи 1, О на входах полусумматора 9 (фиг.З а-е).

По фронту сигнала с выхода полусумматора 9 через блок 11 элементов И обнуляется первый блок 5 памяти. По информационным входам 14.1,...,14. первого блока 5 памяти поступают все нули с выходов блока 11 элементов И, так как сигнал Фронт запрещает прохождение информации с выхода сумматора 20 через блок 11 элементов И, и сигналом Запись с выхода генератора 4 тактовых импульсов по дан ному каналу в первый блок 5 памяти записываются все нули. В том же адресе следующего цикла с выходов первого блока 5 памяти код времени в виде нулей переписывается в регистр 6 сигналом Считывание с выхода элемента НЕ 3. С выхода регистра 6 код времени из всех нулей поступает на входы сумматора 20 счетчика 10 длительности посылки, где к нему прибавляется 1 в младшем разряде, и через блок 11 элементов И код времени поступает на информационные входы 14.1,...,14.К первого блока 5 памяти

380906

Сигналом Запись в той же временной позиции код времени записывается в первый блок 5 памяти. Таким образом производится подсчет проб сигналов по каждому каналу от предыдущего до последующего фронта. При каждом обращении к каналу к предыдущему значению кода времени прибавля- 10 ется 1.

Если в соответствующем коде времени выбрать константу, которая составляет 3/4 длительности бинарной посылки (фиг.4а, Л-константа), то по

15 последующему фронту сигнала можно определить одно- или двукратную длительность принимаемой посылки.

На оси времени (фиг.4 а-и) каждой пробе сигнала соответствует код вре20 мени (фиг.4 г-ж) на выходе сумматора 20, который увеличивается на единицу по каждой пробе посылки, начиная с фронта сигнала. На основании правил сложения и вычитания двоичных чи25 сел по каждому фронту сигнала на фазовом дискриминаторе 7 определяется одно- или двукратная длительность принимаемой посылки.

Вычитая-код времени, соответству30 ющий фронту сигнала, из постоянного

кода константы на сумматоре 24 фазового дискриминатора 7, на выходе сумматора 24 получается сигнал 1, если посылка однократной длительности,

„ и сигнал О, если посылка двукрат- - ной длительности. Причем, константа выбирается, исхо;;я из искажений эле- ментарной посылки, около 50%. Например, при К 4 - четырехразрядный 0 счетчик 10 длительности посылки, константа равна 0110, т.е. 3/4 длительности элементарной посылки на оси времени (фиг.4 а-и). Следовательно, константа в коде времени за- .g висит от скорости принимаемой информации. Предварительно для каждого канала константа записывается во второй блок 12 памяти по соответствую- щим адресам.

При считывании константа в коде

50

55

времени подается с выхода второго блока 12 памяти на вторые входы сумматора 24 фазового дискриминатора 7, на первые входы которого подается инверсное значение кода времени, соответствующее фронту сигнала с вько- дов элементов НЕ 21.1,...,21.К. В результате сложения на выходе сумматора 24 присутствует конечный ре:зультат: однократная посылка - сигнал 1, двукратная - О. Одновременно на параллельных выходах сумматора 24 присутствует код времени,показывающий длительность от фронта сигнала до точки отсчета.

Сигнал о длительности посылки с вькода сумматора 24 поступает на первый вход элемента И 25, на второй вход которого подается фронт посыл- ки. Таким образом, на выходе 17 фазового дискриминатора сигна о длительности посылки будет присутствовать по фронту посыпки.

Рассмотрим работу устройства для выделения посылок сигналов по одному каналу.

Информация, которая поступает на вход коммутатора 1, стробируется в соответствии с адресом канала. На выходе коммутатора 1 формируются про бы информации по данному адресу. Первая проба информации записывается сигналом Запись (фиг.2е) в третий блок 18 памяти блока 8 сдвига.

В следующем цикле по тому же адресу из третьего блока 18 памяти проба информации переписывается в триггер 19 сигналом Считывание с выхода элемента НЕ 3 (фиг.2д), а сигна- лом Запись последующая проба информации записывается в третий блок 18 памяти. На выходе триггера 19 по данному адресу присутствует предыдущая проба информации. На входы полу- сумматора 9 поступает предыдущая проба информации с выхода блока 8 сдвига и текущая проба информации с выхода коммутатора 1. Таким образом при сравнении проб информации на по- лусуммпторе 9 формируется фронт сигнала, если н а его входах сигналы

О, 1 или

О (фиг.З а-е).

По фронту сигнала с выхода полусумматора 9 на входы элементов И 23.1,...,23.К блока 11 элементов И через элемент НЕ 22.1,...,22.К поступает сигнал запрета для обнуления первого блока 5 памяти. Сигналом Запись в первый блок 5 памяти по вхо- дам 14.1,...,14.К по фронту сигнала записываются нули. В следующем цикле сигналом Считывание нули переписываются в регистр 6 с выходов первого блока 5 памяти, затем на сумматоре 20 счетчика 10 длительности посылки к ним прибавляется 1 в младшем разряде сумматора 20. С выходов сумматора 20 счетчика 10 длительности посылки полученная сумма через элементы И 23. 1 ,,,.,23.К записывается в первый блок 5 памяти сигналом Запись. В последующем с каждым циклом к предыдущей сумме на сумматоре 20 прибавляется 1 до последующего фронта. По последующему фронту синала на сумматоре 24 фазового дискриминатора 7 из константы на выходе второго блока 12 памяти вычитается значение кода времени по данному фронту или прибавляется его инверсное значение с выходов элементов НЕ 21.1,...,21.К. В этом случае на выходе сумматора 24 при однократной посылке формируется 1, при двукратной - О (фиг,4 а-и), Таким образом, на выходе 16 полусумматора 9 присутствует фронт посылки, а на выходе 17 фазового дискриминатора 7 - значение посылки по фронту в соответствующей временной позиции.

Формула изобретения

Устройство для выделения посылок сигналов, содержащее коммутатор, входы которого являются информационными входами устройства, последовательно соединенные блок сдвига и полусумматор, последовательно соединенные первый блок памяти и регистр, фазовый дискриминатор, тактовый вход которого соединен с выходом полусумматора, генератор тактовых импульсов и счетчик адреса, выходы которого подключены к адресным входам коммутатора, блока сдвига и первого блока памяти, причем первый выход генератора тактовых импульсов соединен с входом записи блока сдвига, а второй выход - с входом счетчика адреса и через элемент НЕ - с вторым тактовым входом блока сдвига и тактовым входом регистра, выход коммутатора подключен к информационным входам блока сдвига и полусумматора, а выходы последнего и фазового дискриминатора являются выходами устройства, отличающееся тем, что, с целью повышения достоверности, в него введены счетчик длительности посылки, входы которого соединены с выходами регистра, блок элементов И, первые входы которого подключены к выходу полусумматора, вторые входы - к прямым выходам счетчика длительности посылки,а

выходы - к входам первого блока памяти, и второй блок памяти, адресные входы которого соединены с выходами счетчика адреса, при этом первые входы фазового дискриминатора подключены к инверсным выходам счет| 1 -I I- -

. А44444Н44ФЖ

.| -ц-|4Ч-Яп 1-И

6 I

г I М I I I I I

9.

e unl-fjpf - Wjll

Д ddrdiiri±bb±±iФиг.

I .,., I „« I /,

гЛ 1ПГ АЛЛЯ У1 и 1ГииЛМЯ 1ЛЛМ j г }

f П nПЛ1a.

t0 t 0 t 0 1 ...

I« 0 r r f 0

e1 0 i с 1 в

жt о о о 01

ил

Составитель Б.Ефанов Редактор А.Маковская Техред В.Кадар Корректор М.Шароши

Заказ 4147/57Тираж 638Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/3

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

чика длительности посылки, вторые входы - к выходам второго блока памя- ,ти, а первый выход генератора тактовых импульсов соединен дополнительно с входом записи первого блока памяти.

-4-i I I

. , .

1 о 1 о 1 о J а 1 о 10

011001100110

oooiiiictoei с о о о о о о 1 1 I 11

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Многоканальный приемник частотно-модулированных сигналов | 1983 |

|

SU1172066A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Способ тактовой синхронизации и регенерации телеграфных сигналов и устройство для его осуществления | 1991 |

|

SU1830188A3 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1338094A1 |

| Устройство для моделирования процесса синхронизации коротковолновой радиолинии | 1982 |

|

SU1073892A1 |

Изобретение относится к области связи и может быть применено для согласования работы многоканального приемника с удаленными передатчиками. Целью изобретения является повышение достоверности. Устройство для выделения посылок сигналов содержит коммутатор 1, счетчик 2 адреса, элемент НЕ 3, генератор 4 тактовых импульсов, первый блок 5 памяти, регистр 6, фазовый дискриминатор 7,блок 8 сдвига, полусумматор 9, счетчик 10 длительности посылки, блок 11 элементов И и второй блок 12 памяти. При этом входная информация подается на N входов устройства и в каждом канале формируются фронты сигналов с разделением во времени, определяется длительность между значащими моментами путем синхронного отсчета времени от предыдущего до последующего фронта, и на выходах устройства по адресу канала на каждый фронт сигнала выдается значение посылки, краевые искажения которой при приеме менее 50%. 4 ил. i (Л со СО 00 о со фиг

| Устройство групповой тактовой синхронизации (его варианты) | 1982 |

|

SU1096760A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-15—Публикация

1984-01-09—Подача