1

Изобретение относится к вычислительной технике и предназначено для организации многомашинных вычислительных систем.

Известно устройство, содержащее генератор, регистры, дешифраторы, схему сравнения, счетчик ll.

Недостатками известного устройства являются низкая производительность и надежность.

Наиболее близким по сущности к предлагаемому является устройство, содержащее два буферных регистра, регистр управления, регистр состояния, два регистра, две схемы сравнения, распределитель, группы эле- . ментов ИЛИ, группы элементов И, триггер J,

Недостатками известного устройства являются недостаточная надежность и производительность устройства.

Целью изобретения является повышение надежности и быстродействия.

Поставленная цель достигается тем, что в устройстве для сопряжения вычислительных машин, содержащее первую схемы сравнения, первая группа входов которой и группы входов первого буферного регистра и регистра управления соединены с первым информационным входом устройства, первый регистр, выходы котот рого соединены с второй группой

10 входов первой схемы сравнения, выход которой соединен с первым входом распределителя, выходы которого соединены с первыми входами элементов И первой и второй групп и входами

ts первого буферного регистра и регистра управления, выходы которого соединены с вторыми входами элементов И первой группы, выходы которых соединены с первыми входами элементов

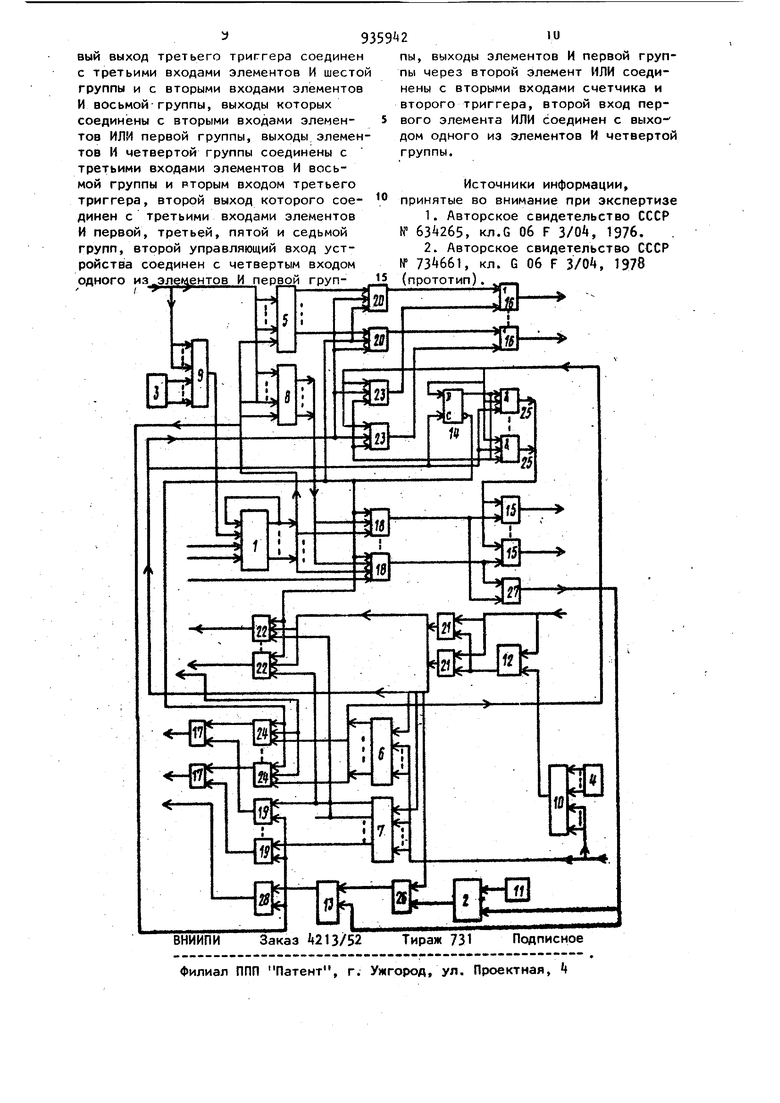

20 ИЛИ первой группы, выходы которых соединены с первой группой управляющих выходов устройства, выходы первого буферного регистра соедийены с первыми входами элементов И третьей группы, выходы которых соединены с первыми входами элементов И второй группы, выходы которых сое динены с первой группой информацион ных выходов устройства, второй информационный вход которого соединен с группами входов второго буферного регистра и регистра состояний и с первой группой входов второй схемы сравнения, вторая группа входов которой соединена с выходами второго регистра, выход второй схемы сравнения соединен с первым входом первого триггера, выход которого соеди нен с первыми входами элементов И четвертой группы, вторые входы которых и первоготриггера соединены с первым управляющим входом устройства, второй управляющий вход которого соединен с вторым и третьим входами распределителя, один из выходов которого соединен с одним из своих входов, выходы элементов И четвертой группы соединены с первыми входами элементов И пятой, шес той и седьмой групп, вторыми входами элементов И третьей группы, второго буферного регистра и регистра состояний и одним из управляющих вы ходов второй группы устройства, дру гие управляющие выходы которой соединены с выходами элементов И пятой группы, вторые входы которых и элементов И второй группы соединены с соответствующими выходами регистра состояний, выходы второго буферного регистра соединены с вторыми входами элементов И второй и шестой груп выходы элементов И шестой группы соединены с вторыми входами элементов ИЛИ второй группы, выходы элементов И второй и седьмой групп через элементы ИЛИ третьей группы соединены с второй группой информационных выходов устройства, генератор, введены счетчик, два триггера, группа элементов И, элемент И, два элемента ИЛИ, причем выход генератора соединен с первым входом счетчика, выход которого соединен с пер вым входом первого элемента ИЛИ, выход которого соединен с первым вх дом второго триггера, выход которог соединен с первым входом элемента И выход которого соединен с информационным выходом второй группы устро ства, второй вход элемента И соединен с одним из выходов распределителя первые входы элементов И восьмой группы и третьего триггера соединены с выходами второго буферного регистра первый выход третьего триггера соединен с третьими входами элементов И шестой группы и со вторыми входами элементов И восьмой группы, выходы которых соединены с вторыми входами элементов ИЛИ первой группы, выходы элементов И четвертой группы соединены с третьими входами элементов И восьмой группы и вторым входом третьего триггера, второй выход которого соединен с третьими входами элементов И первой, третьей пятой и седьмой групп, второй управляющий вход устройства соединен с четвертым входом одного из элементов И первой группы, выходы элементов И первой группы через второй элемент ИЛИ соединены с вторыми входами счетчика и второго триггера, второй вход первого элементу ИЛИ соединен с выходом одного из элементов И четвертой группы. На чертеже приведена блок-схема устройства-. Устройство, содержит распределитель 1, счетчик 2, регистры 3 и 4,буферные регистры 5 и 6,регистр 7 состояния, регистр 8 управления, схемы Э и 10 сравнения, генератор 11, триггеры 12-1, группы элементов ИЛИ 15-17, группы элементов И 18-25 элементы ИЛИ 26 и 27, элемент И 28. ЭВМ-диспетчер управляющим сигналом, поступающим на первый управляющий вход, обнуляет распределитель 1. Затем выдается математический адрес устройства со стороны интерфейса ЭВМ-диспетчера, который поступеет по первому информационному входу устройства на схему сравнения 9, где сравнивается с физическим адресом, записанным в регистре 3, и результат сравнения с выхода схемы сравнения транслируется на информационный вход первого разряда распределителя 1. Одновременно на тактовый вход распределителя 1 поступают синхросигналы, которые переписывают сигнал от схемы 9 (в случае сравнения адресов) на первый выход распределителя 1, а затем последовательно передают его из разряда в разряд, формируя на выходах распределителя 1 управляющие сигналы. Одним из этих сигналов ЭВМ-диспетчер считывает через элемент И 28 группу элементов И 19, группу элементов ИЛИ 17, состояние триггера 1 и рзгистра 7. Затем ЭВМ-диспетчер программно анализирует признак занятости устройства, и если оно сво бодно тогда анализируется в слове состояния разряд занятости ЭВМ-сателлита по обработке предыдущей заявки. Занятость устройство (триггер занятости 13 находится в единичном состоянии)свидетельствует о занятости буферного регистра 5 от предыдущего обмена. Если устройство и ЭВМ-сателлит свободны о ЭВМ-диспетчер выдает в буферный регистр 5 информационное слово, которое является управляющим для ЭВМ-сателлита и характеризует вид и направление o6Mei:ja, а в регистр 8 - код, по которому формируется сигнал запроса к обмену, а в следующем такте распре дителя 1 - сигнал Начало обмена. Эти сигналы поступают в ЭВН-сателлит и одновременно через элемент ИЛ взводят в- 1 триггер 13 и облуляют У4етчик 2. Получив сигнал запроса в систему прерывания, ЭВМ-сателлит прерывает свою программу, прячет ее состояние затем через схему 10 с помощью регистра подключает устройство к своему интерфейсу. Причем результат сравнения в схеме 10 поступает на триггер 12, который фиксирует факт сравнения адресов. После подключения адреса ЭВМ-сателлит считывает через группу элементов И 20 группу элементов ИЛИ 1б содержимое буферно го регистра 5, в котором находятся управляющее слово для ЭВМ-сателлита По результатам анализа этого слова ЭВМ-сателлит переводится на програм му выдачи или приема информации как однословной, так и групповой, либо полняет другие действия. При направ лении обмена из ЭВМ-диспетчера к ЭВМ-сателлиту ЭВМ-диспетчер записы вает в буферный регистр 5 очередное информационное слово, вырабатывается устройством сигнал Начало обмен НЗвыдачу каждого слова, по получении которого ЭВМ-сателлит считывает слово, причем считывающий сигнал, поступающий через группу элементов И 21, группу элементов И 22 поступает в качестве сигнала готовности приему следующего слова в ЭВМ-диспетчер. По получении сигнала готовности ЭВМ-диспетчер посылает очередное слово в регистр 5; одновременно сигнал с группы элементов И 18 через элемент ИЛИ 26 обнуляет триггер 13. Этот триггер в случае сбоя на длительное время (несколько секунд) обнуляется также и счетчиком 2, запускаемым генератором 11. При организации группового обмена временная диаграмма распределителя 1 цик лится, начиная с выхода четвертого разряда, для чего последний выход заведен на информационный вход четвертого разряда, и таким образом из диаграммы исключаются первые сигналы, производящие опрос триггера 13, считывание регистра 7, а также запись в регистр 8. Для обращения к этим элементам устройства необходима выдача ЭВМ-диспетчером команды Адрес, тогда временная диаграмма распределителя 1 будет также полной. В случае получения сигнала занятости устройства при опросе триггера 13 программа ЭВМ-диспетчера по управлению устройством обрывается на команде опроса триггера 13 и циклится на начальном участке, начиная с команды Адрес. После завершения команды обмена ЭВМ- диспетчер через группу элементов И 18, группу элементов ИЛИ 15 выдает в ЭВМ-сателлит сигнал Конец обмена. При групповом обмене ЭВМ-сателлит работает до получения сигнала КО без отключения от канала связи селекторный режим), а ЭВМ-диспетчер, выставив программно в регистр управления 8 соответствующий признак, блокирующий выработку сигнала КОу может производить обмен как в селек торном, так и в мультиплексном режимах при существенном различии в быстродействии доух ЭВМ. Таким образом, окончание обмена задается программным путем через регистр управление 8, что повышает гибкость и быстродействие обмена, а также увеличивает производительность вычислительной системы. Кроме того, в случае зацикливания программ ЭВИ-сателлита и постоянном присутствии в регистре состояния 7 признака занятости ЭВМсателлита ЭВМ-диспетчер умеет возможность через регистр управления 8 программно выдать аварийный сигна приводящий все узлы и регистры ЭВМсателлита в исходное состояние. Для контроля подключают адрес и записывают в буферный регистр 6 код поступающий на триггер lA, который сигналом управления с выхода группы элементов И 21 взводится в единицу. При этом триггер Il своим инверсным выходом запрещает прохождение управ ляющих сигналов от распределителя 1 через группы элементов И 18 и 22. Затем засылается в регистр 6 очеред ное слово и сигналами управления пе редается либо через информационный тракт: группу элементов И 23 группу элементов ИЛИ 16, либо через тракт прохождения управляющих сигналов: группу элементов И 25 и группу элементов ИЛИ 15. По результатам анализа в режиме контроля выданной и полученной информации ЭВМ-сателлит определяет ошибки трактов. Изобретение позволяет повысить надежность и быстродействие устройства. Формула изобретения Устройство для сопряжения вычислительных машин, содержащее первую схему сравнения, первая группа входов которой и группы входов первого буферного регистра и регистра управления соединены с первым информационным входом устройства пер вцй регистр, выходы которого соединены с второй группой входов первой схемы сравнения,выход которой соединен с первым входом распределителя, выходы которого соединены с первыми входами элементов И первой и второй групп и входами первого буферного регистра и регистра управления, выходы которого соединены с вторыми входами элементов И первой группы, выходы к торых соединены с первыми входами элементов ИЛИ первой группы, выходы которых соединены с первой группой управляющих выходов устройства, выходы первого буферного регистра сое динены с первыми входами элементов третьей группы, выходы которых соединены с первыми входами элементов И второй Группы, выходы которых соединены с первой группой информационных выходов устройства, второй информационный вход которого соединен с группами входов второго буферного регистра и регистра состояний и с первой группой входов второй схемы сравнения, вторая группа входов которой соединена с выходами второго регистра, выход второй схемы сравнения соединен с первым входом первого триггера, выход которого соединен с первыми входами элементов И четвертой группы, вторые входы которых и первого триггера соединены с первым управляющим входом устройства, второй управляющий вход которого соединен с вторым и третьим входами распределителя, один из выходов которого соединен с одним из своих входов, выходы элементов И четвертой группы соединены с первыми входами элементов И пятой, шестой и седьмой групп, вторыми входами элементов И третьей группы, второго буферного регистра и регистра состояний и одним из уп равляющих выходов второй группы устройства, другие управляющие выходы которой соединены с выходами элементов И пятой группы, вторые входы которых и элементов И второй группы соединены с соответствующими выходами регистра состояний, выходы второго буферного регистра соединены с вторыми входами элементов И второй и шестой групп, выходы элементов И шестой группы соединены с вторыми входами элементов ИЛИ второй группы, выходы элементов И второй и седьмой групп через элементы ИЛИ третьей группы соединены с второй группой информационных выходов устройства, генератор, отличающееся тем, что, с целью повышения быстродействия и надежности, в него введены счетчик, два триггера, группа элементов И, элемент И, два элемента ИЛИ, причем выход генератора соединен с первым входом счетчика, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом второго триггера, выход которого соединен с первым входом элемента И, выход которого соединен с информационным выходом второй группы устройства, второй вход элемента И соединен с одним из выходов распределителя, первые входы элементов И восьмой группы и третьего триггера соединены с выходами второго СЗуферного регистра, пер

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения с общей маги-СТРАлью ВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU809143A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

Авторы

Даты

1982-06-15—Публикация

1981-03-03—Подача