I

Изобретение относится к выиислительной технике и может быть использовано при проектиробёнии ЭВМ и мультипроцессорных вымислительных систем.

Известны устройства связи, для вычислительной системы, содержащие блок синхронизации и группу каналов, каждый из которых включает буферный регистр, регистр адреса, приемный и пе редающий регистры, управляющий регистр, распределитель импульсов, узел синхронизации5 блок сравнения, узел коммутации управляющих сигналов 13.

Недостаток этих устройств состоит в низкой пропускной способности.

Наиболее близким к предлагаемому по технической сущности является устройство связи для вычислительной системы , содержащее группу приемных регистров, группу элементов ИЛИ, группу передающих регистров, группу распределителей импульсов, группу блоков сравнения, группу регистров адреса, группу управляющих регистров.

группу узлов синхронизации, группы первых- и вторых буферных регистров, группу узлов элементов И и блок синхронизации, первый выход которого соединен со входами распределителей импульсов группы и управляющими входами приемных регистров, второй выхо блока синхронизации, соединен с пер управляющими входами передающих регистров группы, вход каждого пере10дающего регистра группы через соответствующий элемент ИЛИ группы подключен к выходу каждого приемного регистре группы, выход каждого передающего регистра группы соединен с информа15ционным входом каждого последующего приемного регистра группы и первыми информационными входами каждых блока сравнения и вторых буферных регистров группы, вторые информационные дходы

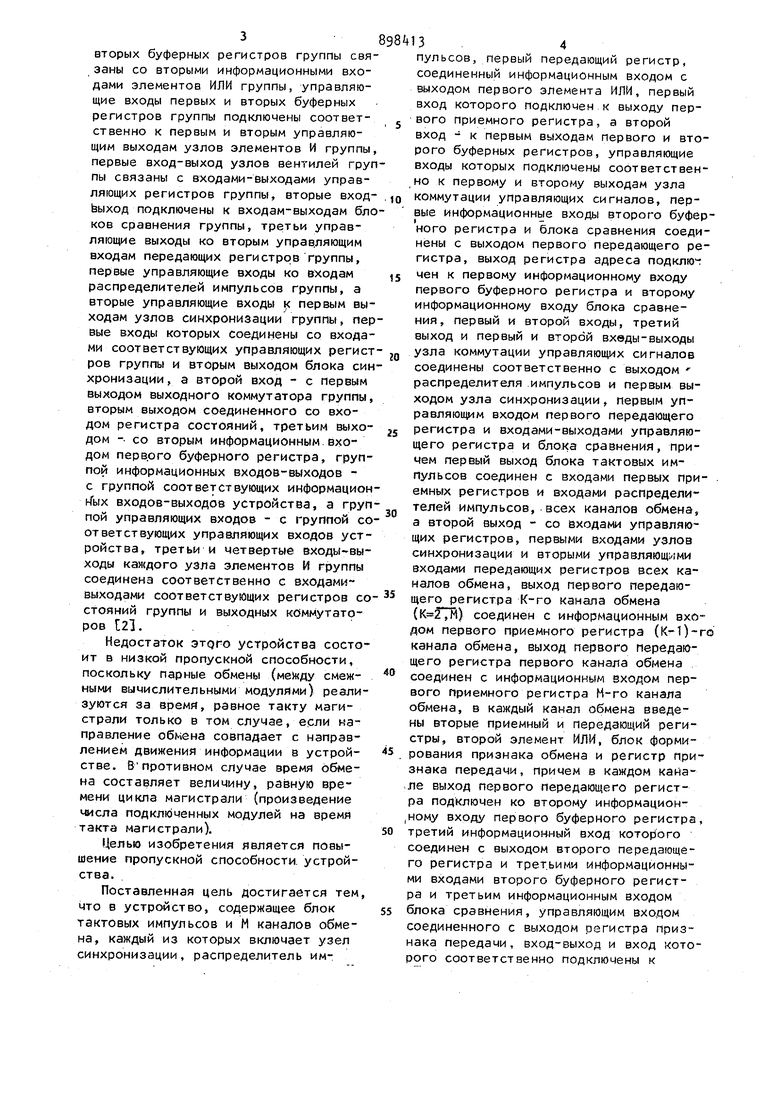

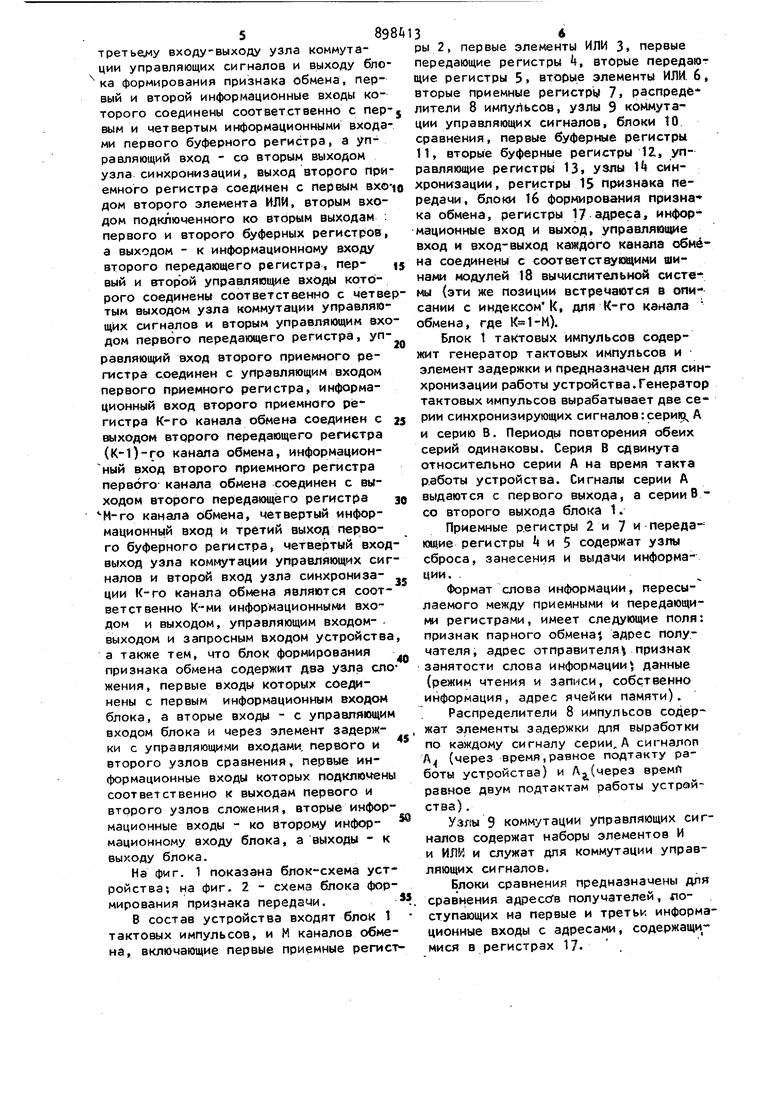

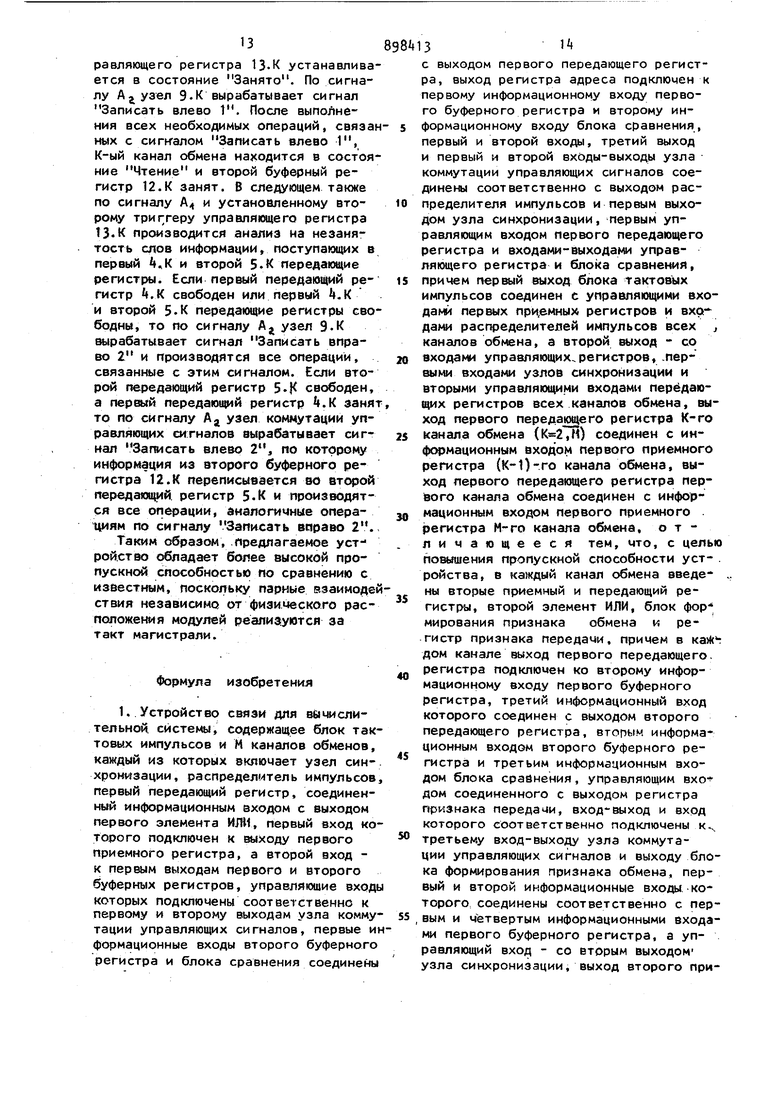

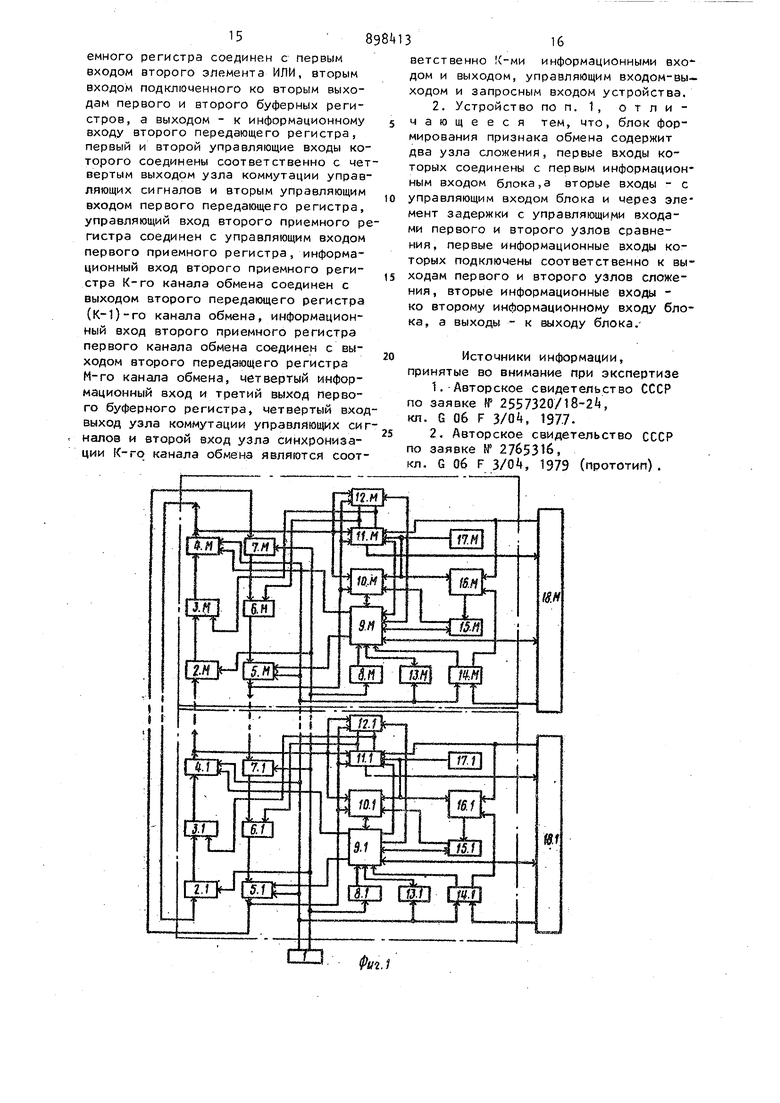

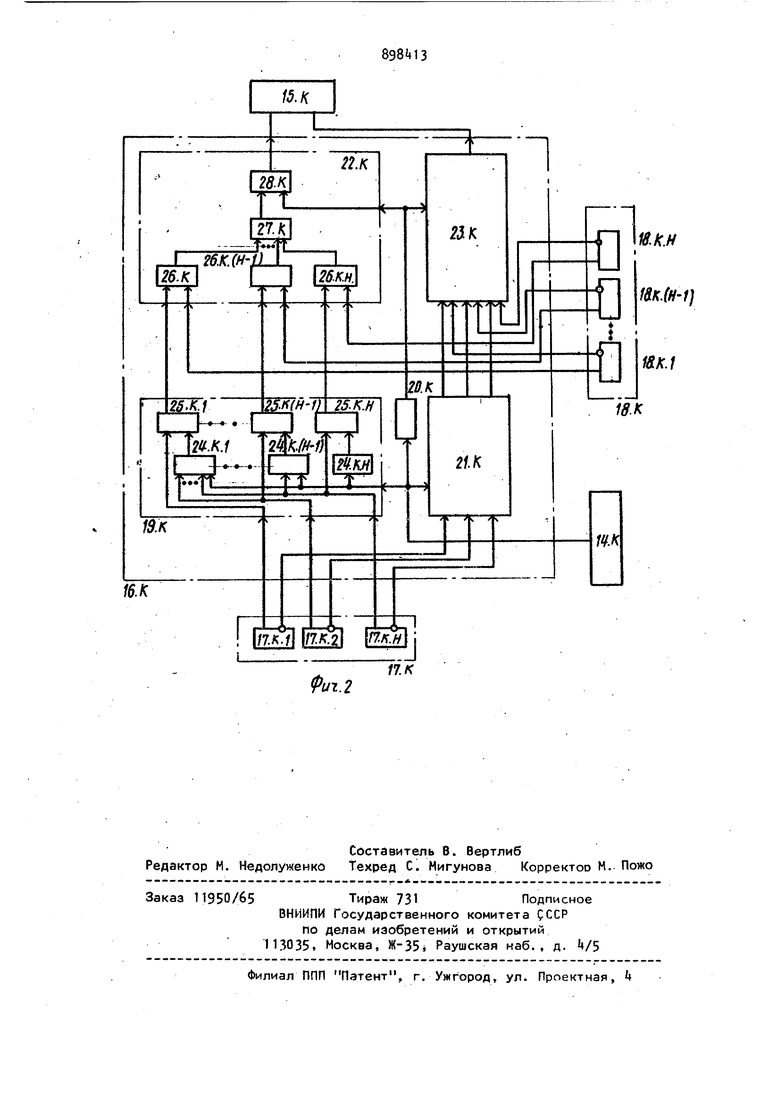

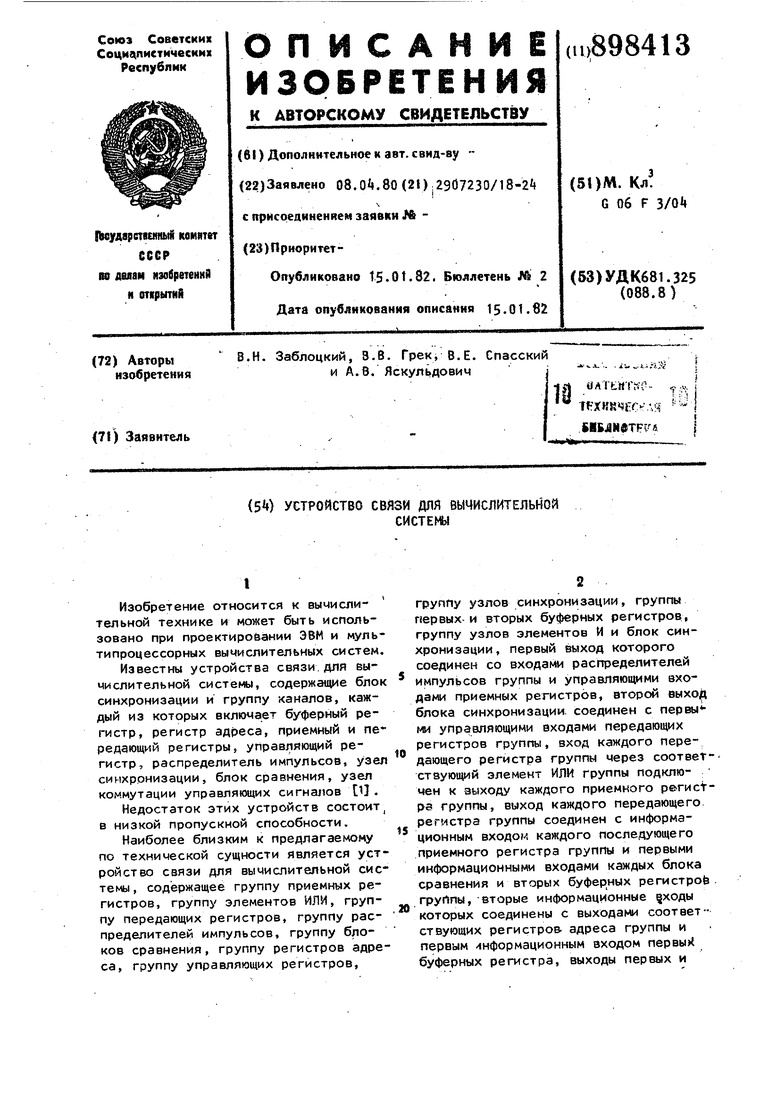

20 которых соединены с выходами соответствующих регистров адреса группы и первым информационным входом первы( буферных регистра, выходы первых и вторых буферных регистров группы свя заны со вторыми информационными входами элементов ИЛИ группы, управляющие входы первых и вторых буферных регистров группы подключены соответственно к первым и вторым управляющим выходам узлов элементов И группы первые вход-выход узлов вентилей гру пы связаны с входами-выходами управляющих регистров группы, вторые вход ёыход подключены к входам-выходам бл ков сравнения группы, третьи управляющие выходы ко вторым управляющим входам передающих регистров группы, первые управляющие входы ко входам распределителей импульсов группы, а вторые управляющие входы к первым вы ходам узлов синхронизации группы, пе вые входы которых соединены со входа ми соответствующих управляющих регист ров группы и вторым выходом блока син хронизации, а второй вход - с первым выходом выходного коммутатора группы вторым выходом соединенного со входом регистра состояний, третьим вь(ходом - со вторым информационным, входом перв.ого буферного регистра, группой информационных входов-выходов с группой соответствующих информацион h4(x входов-выходов устройства, а груп пой управляющих входов - с группой со ответствующих управляющих входов устройства, третьи и четвертые входы-выходы каждого узла элементов И группы соединена соответственно с входами выходами соответствующих регистров со стояний группы и выходных коммутаторов 23. Недостаток этдго устройства состоит в низкой пропускной способности, поскольку парные обмены (меЛду смежными вычислительными модулями) реализуются за время, равное такту магистрали только в том случае, если направление обмена совпадает с направлением движения информации в устройстве. Впротивном случае время обмена составляет величину, равную времени цикла магистрали (произведение числа подключенных модулей на время такта магистрали). Целью изобретения является повышение пропускной способности, устройства. Поставленная цель достигается тем, что в устройство, содержащее блок тактовых импульсов и М каналов обмена, каждый из которых включает узел синхронизации, распределитель импульсов, первый передающий регистр, соединенный информационным входом с выходом первого элемента ИЛИ, первый вход которого подключен к выходу первого приемного регистра, а второй вход - к первым выходам первого и второго буферных регистров, управляющие входы которых подключены соответственно к первому и второму выходам узла коммутации управляющих сигналов, первые информацисннь1е входы второго буферного регистра и блока сравнения соединены с выходом первого передающего регистра, выход регистра адреса подклю-г чей к первому информационному входу первого буферного регистра и второму информационному входу блока сравнения, первый и второй входы, третий выход и первый и второй вхвды-выходы узла коммутации управляющих сигналов соединены соответственно с выходом распределителя .импульсов и первым выходом узла синхронизации, первым управляющим входом первого передающего регистра и входами-выходами управляющего регистра и блока сравнения, причем первый выход блока тактовых импульсов соединен с входами первых при- . емных регистров и входами распределителей импульсов, всех каналов обмена, а второй выход - со входами управляющих регистров, первыми входами узлов синхронизации и вторыми управляющими входами передающих регистров всех каналов обмена, выход первого передающего регистра К-го канала обмена ) соединен с информационным входом первого приемного регистра (К-1)-го канала обмена, выход первого передающего регистра первого канала обмена соединен с информационным входом первого Приемного регистра М-го канала обмена, в каждый канал обмена введены вторые приемный и передающий регистры, второй элемент ИЛИ, блок формирования признака обмена и регистр признака передачи, причем в каждом кайале выход первого передающего регистра подключен ко второму информационному входу первого буферного регистра, третий информационный вход которого соединен с выходом второго передающего регистра и третьими информационными входами второго буферного регистра и третьим информационным входом блока сравнения, управляющим входом соединенного с выходом регистра признака передачи, вход-выход и вход которого соответственно подключены к 589 третьему входу-выходу узла коммутации управляющих сигналов и выходу формирования признака обмена, первый и второй информационные входы которого соединены соответственно с nep вым и четвертым информационными входа ми первого буферного регистра, а управляющий вход - со вторым выходом узла синхронизации, выход второго при емного регистра соединен с первым вхо дом второго элемента ИЛИ, вторым входом подключенного ко вторым выходам ; первого и второго буферных регистров, а выходом - к информационному входу второго передающего регистра, первый и второй управляющие входы которого соединены соответственно с четве тым выходом узла коммутации управляющих сигналов и вторым управляющим вхо дом первого передающего регистра, управляюи й вход второго приемного регистра соединен с управляющим входом первого приемного регистра, информационный вход второго приемного регистра Кто канала обмена соединен с выходом второго передающего регистра (K-l)-ro канала обмена, информацион ный вход второго приемного регистра первого канала обмена соединен с выходом второго передающего регистра М-го канала обмена, четвертый информационный вход и третий выхоА первого буферного регистра, четвертый вход выход узла коммутации управляющих сиг налов и второй вход узла синхронизации К-го канала обмена являются соответственно К-ми инфopмaциoнны и входом и выходом, управляющим входом- выходом и запросным Входом устройства а также тем, что блок формирования признака обмена содержит два узла сло жения, первые входы которых соединены с первым информационным входом блока, а вторые входы - с управляющим входом блока и через элемент задержки с управляющими входами, первого и второго узлов сравнения, первые информационные входы которых подклю 1вны соответственно к выходам первого и второго узлов сложения, вторые информационные входы - ко второму информационному входу блока, а выходы - к выходу блока. На фиг. 1 показана блок-схема устройства; на фиг. Z - схема блока формирования признака передгии. В состав устройства входят блок 1 тактовых импульсов, и М каналов обмена, включающие первые приемные регист 3« ры 2, первые элементы ИЛИ 3, первые передающие регистры 4, вторые передают щие регистры 5, вторые элементы ИЛИ. 6, вторые приемные регистру 7, распреде лители 8 импульсов, узлы 9 коммутации управляющих сигналов, блоки 10 сравнения, первые буферные регистры П, вторые буферные регистры 12, управляющие регистры 13. узлы И синхронизации, регистры 15 признака передачи, блоки 16 формирования призна ка обмена, регистры 17 адреса, информационные вход и выход, управляющие вход и вход-выход каждого канала обмена соединены с соответствующими шинами модулей 18 вычислительной системы (эти же позиции встречаются в описании с индексомК, для К-го канала обмена, где ). Блок 1 тактовых импульсов содержит генератор тактовых импульсов и элемент задержки и предназначен для синхронизации работы устройства.Генератор тактовых импульсов вырабатывает две серии синхронизирующих сигналов: серию А и серию В. Периоды повторения обеих серий одинаковы. Серия В сдвинута относительно серии А на время такта работы устройства. Сигналы серии А выдаются с первого выхода, а серии В со второго выхода блока 1. Приемные р.егистры 2 и 7 и передающие регистры t и 5 содержат узлы сброса, занесения и выдачи информации. . Формат слова информации, пересылаемого между приемными и передающими регистрами, имеет следукицие поля: признак парного обмена , адрес получателя, адрес отправителя признак занятости слова информации данные (режим чтения и записи, собственно информация, адрес ячейки памяти). Распределители 8 импульсов содержат элементы задержки для выработки по каждому сигналу серии А сигналоп А {через время,равное подтакту работы устройства) и Aj(4epe3 времП равное двум подтактам работы устройства). Узлы 9 коммутации управляющих сигналов содержат наборы элементов И и ИЛИ и служат для коммутации управляющих сигналов. Блоки сравнения предназначены для сравнения адрессгв получателей, лоступающих на первые и третьи информационные входы с адресами, содержащимися в регистрах 17- , 7 Вторые буферные регистры предназначены для хранения информации, принятой из первого передающего регистра в случае парного обмена с последующим модулем вычислительной системы.или из второго передающего регист ра, в случае парного обмена с предыдущим модулем вычислительной системы Управляющие регистры 13 содержат элементы занесения, сброса и первую группу триггеров, указывающих состоя ние (занято-свободно) первых буферных регистров, вторую группу триггеров , указывающих состояние (зёнято-сво бодно) вторых буферных регистров 12, третью группу триггеров,указывающих ре жим работа (запись-чтение) модулей вычислительной системы 18. Узлы 1 синхронизации содержат триггеры, элементы занесения и сброса, предназначены для синхронизации запросов, поступающих из модулей. Регистры 15 признаков передачи содержат триггеры, элементьс занесения и сброса и предназначены для хра нения информации о направлении парного обмена, поступающей из блоков 16. формирования признака обмена, которые предназначены для определения направления парного обмена в зависимости от адресов получателя, поступа щих из модулей вычислительной систем В состав К-го блока (фиг. 2) формирования признака обмена входят пер вый узел сложения 19- К элемент задержки 20. К, второй узел сложения 2t. К, первый узел сравнения 22.К и второй узел сравнения 23-К. Первый узел сложения 19.К содерй ит группу элементов И 2.К-24.К.Н, группу элементов сложения по модулю 2 25.К.1-25.К.Н и предназначен для увеличения на единицу адреса отправителя, поступающего из регистра 17. Элементы И 2.КЛ-2.1(.Н предназ.начены для формирования сигналов поразрядного переноса. Элементы сложения по модулю 2 25.К.1-25.К.Н предназначены ДОЯ пора рядного суммирования сигналов перено са с разрядами адреса, поступающего на вход узла сложения 19.К. Элемент задержки 20.К прейназначе для задержки сигнала опроса, поступа щего на управляющий вход блока форми рования признака передачи 16. Второй узел сложения 21.К по составу аналогичен первому узлу сложения 19.К и предназначен для уменьше38ния на единицу адреса отправителя, поступающего в обратном коде из регистра адреса 17.. Первый узел сравнения 22.К предназначен для сравнения адреса, поступающего на первые информационные входы, с адресом, поступающим на вторые информационные входы блока и содержит группу элементов сложения по модулю 2 26.К.1-26.К.Н, элемент ИЛИ 27.К и элемент И-НЕ 28.К. Второй узел сравнения 23.К по составу аналогичен первому узлу сравнения 22. К. Регистры 17 адреса предназначены для хранения адресов отправителей и содержат узлы сброса и занесения информации с пульта управления (не показан) . 8 качестве модулей 18 вычислительной системы могут использоваться процессоры, блоки оперативной памяти, каналы прямого доступа и т.п. Устройство работает следующим образом. По пуску устройства блок 1 наминает вырабатывать серии сигналов А и В, под управлением которых в устройстве начинают циркулировать свободные слова. По каждому сигналу В информация в парафазном коде передается из первых и вторых передающих регистров соответственно в первые и вторые приемные регистры. По сигналу А информации из первых и вторых приемных регистров в парафазном коде передается в первые и вторые передающие регистры. Каждая К-я часть может работать в двух режимах: Чтение и Запись. Режим Чтение предназначен для приема информации, адресованной К-ой частиустройства м передачи ее модулю 18 вычислительной системы. По сигналу В и состоянию Чтение третьего триггера в управляющем регистре 13.К информация первых ii.K-1 и вторых 5.К+1 передающих регистров соответственно пересылается в первые 2.К и вторые 7-К приемные регистры и опрашивается узел 1t..на наличие запроса от модуля 18. К. Если запрос из модуля 18.К отсутствует, то по сигналу А информация из первых 2.К и вторых 7-К приемных регистров пересылается соответственно в первые 4.К и вторые 5.К передающие регистры. Поле из слова информации, соответствующее адресу получателя из первого .К и второго 5-К пе 9 редающих регистров, поступает в блок 10.К, где сравнивается с содержимым регистра 17.К. По сигналу А из распределителя импульсов 8.К узел 9.К посылает в блок сравнения 10,К сигнал Опрос , в результате чего на выходе блока 10.К появится один из следующих сигналов: Принять справа или Принять слева. Сигнал Принять справа означает, что во второй передающий ре гистр 5.К поступила информация, адресованная данному модулю, или, что такая информация одновременно находится в первом .К и втором 5.К передающих регистрах. Сигнал Принять сле ва означает, что в первый передакмций регистр .К поступила информация, адресованная данному модулю, или, что такая информация одновременно находится во втором 5.К и первом 4.К передающих регистрах. По сигналу Принять справа и свободному первому буферному регистру It.К информация из второго передающего регистра 5-К переписывается в первый буферный регистр 11.К и в модуль iS.K поступает сигнал Принять При этом триггер управляющего регистра 13.К, указывающий состояние пер вого буферного регистра 11,К, переходит в состояние Занято. Задерман ным сигналом из узла 9.К второй пере дающий регистр 5.К сбрасывается, чем обеспечивается очистка слова информа ции. Сигналом серии В нулевое слово продвинуто влево по магистрали. По сигналу Принять модуль 18.К принимает информацию из первого буферного регистра 11.К на свои внутренние регистры, после чего на выход узла 9-К поступает сигнал Приня то, по которому триггер первого бу ферного регистра 11. К в управляющем регистре 13. К переводится в состояние Свободно, первый буферный регистр 11. К сбрасывается. По сигналу Принять слева и свободному первому регистру 11.К информ ция из первого передающего регистра ,К переписывается в первый буферный регистр 11,К. Со входа-выхода уз ла 9. К в модуг ь 18.К поступает сигна Принять, триггер управляющего регистра 13.К, указывающий состояние первого буферного регистра 11.К, пер водится в состояние Занято. Задерж анным сигналом из узла 9.К первый передающий регистр i.K сбрасывается. 310 чем обеспечивается очистка слова информации. Сигналом i серии В нулевое слово продвинуто вправо по магистрали. По сигналу Принять - выполняются операции, аналогичные описанным. Режим Запись предназначен для выдачи информации модуля 18.К вычислительной системы в первый или второй передающие регистры, В зтом случае, когда модуль 18.К должен передать информацию, он выставляет данные на четвертый информационный вход первого буферного регистра 11.К, адрес получателя подает на второй информационный вход блока 16.К и одновременно посылает сигнал в узел Н.К. По сигналу В при налимий запроса от модуля 18.К триггер синхрозапроса в узле синхронизации устанавливается в состояние Синхрозапрос и третий триггер управляющего регистра 13.К переводится в режим Запись. По сигналу А и установленному триггеру синхрозапроса в узле синхронизации данные из модули вычисли тельной системы и регистра 17.К переписываются 8 первый буферный регистр 11,К, первый триггер управляющего регистра 13.К устанавливается в состояние Занято, на втором выходе узла .K появляется сигнал опроса первого 19.К (фиг. 2) и второго.21.К узлов сложения. По сигналу опроса элемента И 2,К. 1г2й.К.Н формируют сигналы переноса в каждом разряде, которые суммируются с разрядами адреса, поступаюцими на входы узла сложения 19.К, в результате чего, на выхо де элементов сложения по модулю 2 25.К.1-25.К.Н формируется адрес на единицу больший адреса отправителя. Этот адрес поступает на первые информационные входы узла сравнения 22.К, где поразрядно суммируется Иа элементах сложения по модулю 26.К.1-26.К.Н с адресом получателя, поступающим на вторые информационнее входы узла сравнения 22,К. При , совпадении адресов на выходе элемента И-НЕ 2В.К формируется сигнал, означающий, что адрес получателя на единицу больше адреса отправителя, по которому регистр 15.К устанавливается .в состояние Передать вправо. Аналогичные операции выполня1&тся во вторых узлах сложения и сравнения при формировании сигнала Передать влево. При отсутствии сигналов на выходе первого 22,К и второго 23.К узлов сложения, регистр 15.К устанавливает ся в состояние Передать. Признак Передать означает, что абсолютная величина разности адреса получателя из модуля 18.К вычислительной системы и адреса отправителя из регистра 17-К больше единицы, т.е. должен быть выполнен перекрес ный обмен. По .сигналу А и установленному признаку Передать производится ана лиз слов информации, поступивших в первый 4.К и во второй 5.К передающи регистры на незанятость слова информации (свободное слово). Если первый передающий регистр . свободен или первый .tC и второй передающие регистры свободнь, то по ;сигналу AJ узел 9.К вырабатывает сиг jнал Записать вправо 1, По этому сигналу информация из первого буферного регистра И.К переписывается в первый передающий регистр 4.К, задержанным сигналом из узла 9.К, сбра сываются- первый буферный регистр И. триггер синхрозапроса в узле И.К и. первый триггер в управляющем регистр t3.K, третий триггер в управляющем регистре 13.К переводится в режим Чтение. . Если второй передающий регистр 5.К свободен, а первый передающий ре гистр .К занят, то по сигналу Ад из узла 9.К вырабатывается сигнал Записать влево 1, по которому информа ция из первого буферного регистра 11.К переписывается во второй переда щий регистр 5.К. Далее производятся действия, аналогичные действиям по сигналу Записать вправо , По сигналу А и установленному признаку Передать вправо производи ся анализ слова информации на незанятость в первом передающем регистре .К. Если первый передающий регистр k.K свободен, то по сигналу А вырабатывается сигнал Записать вправо 1 Если первый передающий регистр i.K занят, то по сигналу А информация из первого передающего регистра 4,К переписывается во второй буферный регистр 12.К и второй триггер управляющего регистра 13.К устанавливается в состояние Занято. По сигналу А,, узел 9.К вырабатывает сигнал Записат вправо 1. После выпблнения всех необ ходимых операций, связанных с сигналом Записать вправо 1, канал обмена устройства находится в состоянии Чтение и второй буферный регистр 12.К занят. При этом могут аыполняться операции режима Чтение, а режим Запись не может быть выполнен, так как триггер синхроаапроса от модуля 18.К блокирован. Очистка второго буферного регистра 12.К производится следующим образом. По сигналу А и установленному второму триггеру в управляющем регистре 13-К производится анализ на незаня о слов информации, поступающих в первые ij.K и вторые 5.К передающие регистры. Если первый передающий регистр .К свободен, или первый Л.К и второй 5.К передающие регистры свободны, то по сигналу 9.К вырабатывает сигнал Записать вправо 2. По этому сигналу информация из второго буферного регистра 12.К переписывается в передающий регистр .К, задержанным сигналом из узла 9.1 сбрасываются второй буферный регистр 12.К и второй триггер в управляющем регистре 13. К. Если второй передающий регистр 5.К свободен, а первый передающий регистр .К занят, то по сигналу A«i узел 9.К вырабатывает сигнал Записать влево 2 по которому информации из второго буферного регистра 12.К переписывается во второй передающий регистр 5.К. Далее производятся действия, аналогичные действиям по сигналу Записать вправо 2. По сигналу А;, и установленному j признаку Передать влево пйоизводится анализ слова информации на незанятость во втором передающем регистре 5.К. Если он свободен, то по сигналу А вырабатывается сигнал Записать влево Т. По этому сигналу информация из первого буферного регистра 11.К переписывается во второй передающий регистр 5.К, задержанным сигналом из узла 9.К сбрасываются первый буферный регистр 11.К, триггер синхрозапроса в узле 14.К, первый триггер в управляющем регистре 13.К, третий триггер в управляющем регистре 13.К переводится в режим Чтение. Если второй передающий регистр 5.1 занят, то по сигналу Aj информация из второго передающего регистра 5.К переписывается во второй буферный регистр 12,К и второй триггер уп13равляющего регистра 13.К устанавлива ется в состояние Занято. По сигналу АJ узел 9.К вырабатывает сигнал Записать влево t. После выполнения всех необходимых операций, связа ных с сигкалом Записать влево 1, К-ый канал обмена находится в состоя ние Чтение и второй буферный регистр 12.К занят. В следующем также по сигналу А и установленному второму триггеру управляющего регистра 13«К производится анализ на незанятость слов информации, поступающих в первый (К и второй передающие регистры. Если первый передающий регистр k,K свободен или первый 4.К и второй 5.К передающие регистры сво бодны, то по сигналу А узел 9.К вырабатывает сигнал Записать вправо 2 и производятся все операции, связанные с этим сигналом. Если второй передающий регистр свободен, а первый передаюифиЙ регистр U.K заня то по сигналу Aj узел коммутации управляющих сигналов вырабатывает сигнал Записать влево 2, по которому информация из второго буферного регистра 12.К переписывается во втсчэой передаюи й. регистр 5.К и производятся все операции, аналогичные операциям по сигналу Записать вправо 2. Таким образом,.Предлагаемое уст ройство обладает более высокой пропускной способностью по сравнению с известным, поскольку парные взаимоде ствия независимо от физического расположения модулей реализуются за такт магистрали. Формула изобретения 1. Устройство связи для вычислительной системы, содержащее блок так товых импульсов и М каналов обменов, каждый из которых включает узел синхронизации, распределитель импульсов первый передающий регистр, соединенный информационным входом с выходом первого элемента ИЛИ, первый вход ко торого подключен к выходу первого приемного регистра, а второй вход к первым выходам первого м второго буферных регистров, управляющие вход которых подключены соответственно к первому и второму выходам узла комму тации управляющих сигналов, первые и формационные входы второго буферного регистра и блока сравнения соединены 31А с выходом первого передающего регистра, выход регистра адреса подключен к первому информационному входу первого буферного регистра и второму информационному входу блока сравнения, первый и второй входы, третий выход и первый и второй вхйды-выходы узла коммутации управляющих сигналов соедине1Ш соответственно с выходом распределителя импульсов и первым выходом узла синхронизации, первым управляющим входом первого передающего регистра и входами-выходами управляющего регистра и блока сравнения, причем первый выход блока тактовых импульсов соединен с управляющими входами первых приемных регистров и вхрдами распределителей импульсов всех j каналов обкюна, а второй выход - со входами управляющих.регистров, .первыми входами узлов синхронизации и вторыми управляющими входами передающих регистров всех каналов обмена, выход первого передающего регистра К-го канала обмена (,М) соединен с информационным входом первого приемного регистра {К-1)-го канала обмена, выход первого передающего регистра первого канала обмена соединен с информационным входом первого приемного регистра М-го канала обмена, отличающееся тем, что, с целью повышения пропускной способности устройства, в каждый канал обмена введены вторые приемный и передающий регистры, второй элемент ИЛИ, блок фор мирования признака обмена и регистр признака передачи, причем в дом канале выход первого передающего, регистра подключен ко второму информационному входу первого буферного регистра, третий информационный вход которого соединен с выходом второго передающего регистра, вторы.ч информационным входом второго буферного регистра и третьим информационным входом блока сравнения, управляющим входом соединенного с выходом регистра признака передачи, вход выход и вхрд которого соответственно подключены к,,, третьему вход-выходу узла коммутации управляющих сигналов и выходу блока формирования признака обмена, первый и второй информационные входы, которого, соединены соответственно с первым и четвертым информационными входами первого буферного регистра, а управляющий вход - со вторым ВЫХОДОМ узла синхронизации, выход второго приемного регистра соединен с первым входом второго элемента ИЛИ, вторым входом подключенного ко вторым выходам первого и второго буферных регистров, а выходом - к информационному входу второго передающего регистра, первый и второй управляющие входы которого соединены соответственно с чет вертым выходом узла коммутации управ ляющих сигналов и вторым управляющим входом первого передающего регистра, управляющий вход второго приемного р гистра соединен с управляющим входом первого приемного регистра, информационный вход второго приемного регистра К-го канала обмена соединен с выходом второго передающего регистра (К-1)-го канала обмена, информационный вход второго приемного регистра первого канала обмена соединен с выходом второго передающего регистра М-го канала обмена, четвертый информационный вход и третий выход первого буферного регистра, четвертый вход выход узла коммутации управляющих сиг налов и второй вход узла синхронизации канала обмена являются соот816 ветственно (-ми информационными вхо дом и выходом, управляющим входом-выходом и запросным входом устройства. 2. Устройство по п. 1, о т л и чающееся тем, что, блок формирования признака обмена содержит два узла сложения, первые входы которых соединены с первым информацион ным входом блока,а вторые входы - с управляющим входом блока и через эле мент задержки с управляющими входами первого и второго узлов сравнения, первые информационные входы которых подключены соответственно к выходам первого и второго узлов сложения, вторые информационные входы ко второму информационному входу блока, а выходы - к выходу блока.Источники информации, принятые во внимание при экспертизе 1.-Авторское свидетельство СССР по заявке № 2557320/18-2, кп. G 06 F 3/0, 197.7. 2, Авторское свидетельство СССР по заявке № 2765316, кл, G Об F 3/0, 1979 (прототип).

СГЦ. . ф1

иг.2

п. к

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

| Устройство связи для вычислительной системы | 1977 |

|

SU734654A1 |

Авторы

Даты

1982-01-15—Публикация

1980-04-08—Подача