154). ЭЛЕМЕНТ К- НАЧНОЙ ПОРОГОВОЙ ЛСГИКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный элемент к-значной логики | 1980 |

|

SU871337A1 |

| Формирователь переноса /Заема/ к-значной логики | 1980 |

|

SU907802A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ k-ЗНАЧНОЙ ПЕРЕМЕННОЙ С ПОРОГОВЫМ ЗНАЧЕНИЕМ | 2014 |

|

RU2546085C1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Многофункциональная схема многозначной логики | 1980 |

|

SU930681A1 |

| Устройство для моделирования функций нейрона | 1983 |

|

SU1138813A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ТОКОВЫЙ ЭЛЕМЕНТ ОГРАНИЧЕНИЯ МНОГОЗНАЧНОЙ ВЫХОДНОЙ ЛОГИЧЕСКОЙ ПЕРЕМЕННОЙ | 2017 |

|

RU2640740C1 |

| Устройство для приема и передачи информации | 1988 |

|

SU1510095A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

I

Изобретение относится к эпектрсийке и автоматике н может быть использовано в цифровых устройствах, а также прк построении К -значных логических уст ройств дискретной автетлатики.

Известен элемент 1с -значной логики, Построенный на основе интегральной ижекцисйяной логики I и Л) и выполняющий функцию циклического отрицания

f(x;(.x + ijmod4ri} .

Однако данный элемент не обеспечивает реализацию -аначных пороговых функций.

Известен также универсальньй многозначный логический элемент инжекцион- ного типа, построенный на основе логики и содержащий ИЛ вентили, та- ристоры И Л и источники тока t23 .

Недостатком известного устройства являются узкие функциональные возможности, так как оно реализует только -з гачные функции двух переменных и не реализует 1с-значные пороговые фушь ции.

Цель изобретения - расширение функдконалы{ых возможностей, а именно обеспечение реализации К-значных пороговых функций.

Поставленная цель достигается тем, что в устройство, содержаще ИЛ вентиль, выход которого соединен с источником тока, транзистор ИЛ и входные шины, введены первый формирователь взвешенной суммы, выход которого через и Л вентиль подключен к выходу второго формирователя взвешенной суммы, входу выходного блока, база транзистора подключена к шине порога, а коллектор к выходу одного из формирователей взвешенной единицы, причем входные шины подключены к входам . мирователей взвешенных сумм и остальнь1М входам выходного блока.

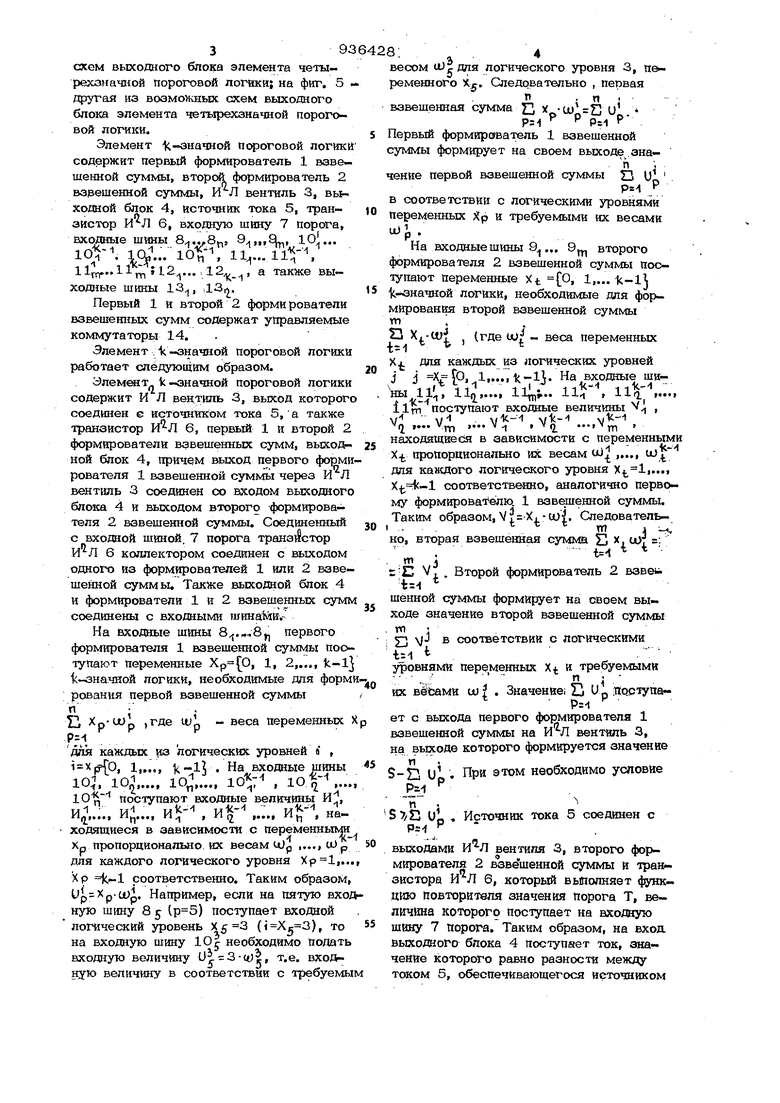

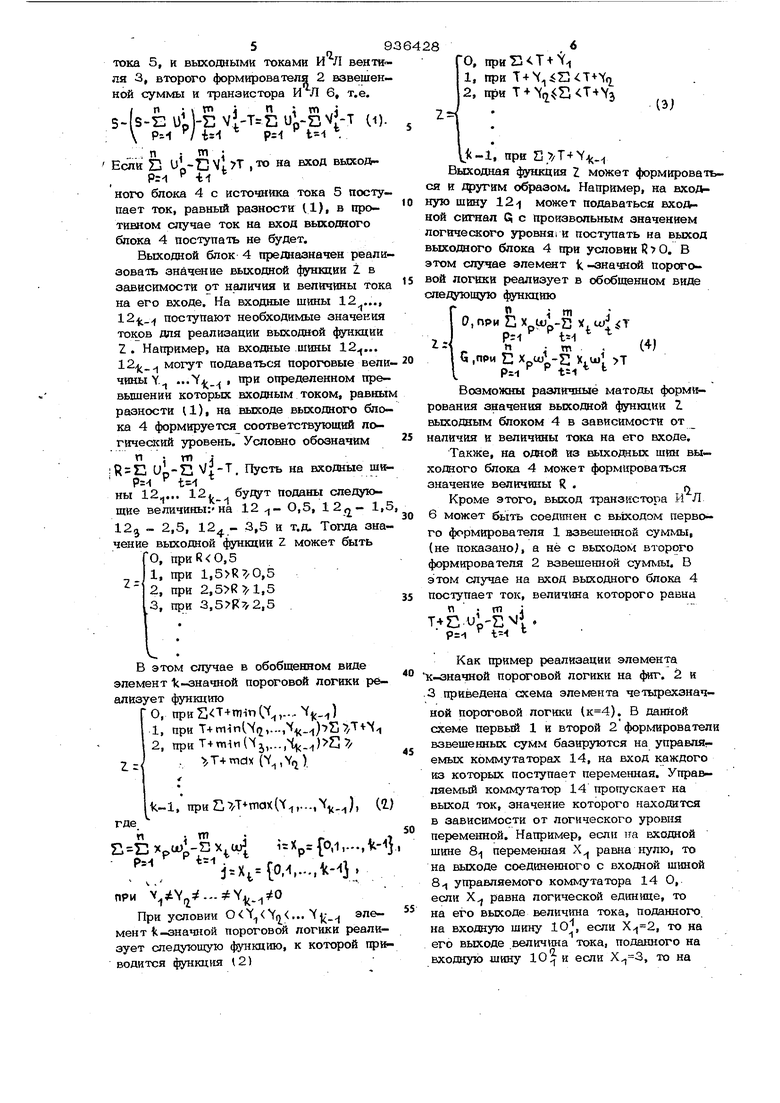

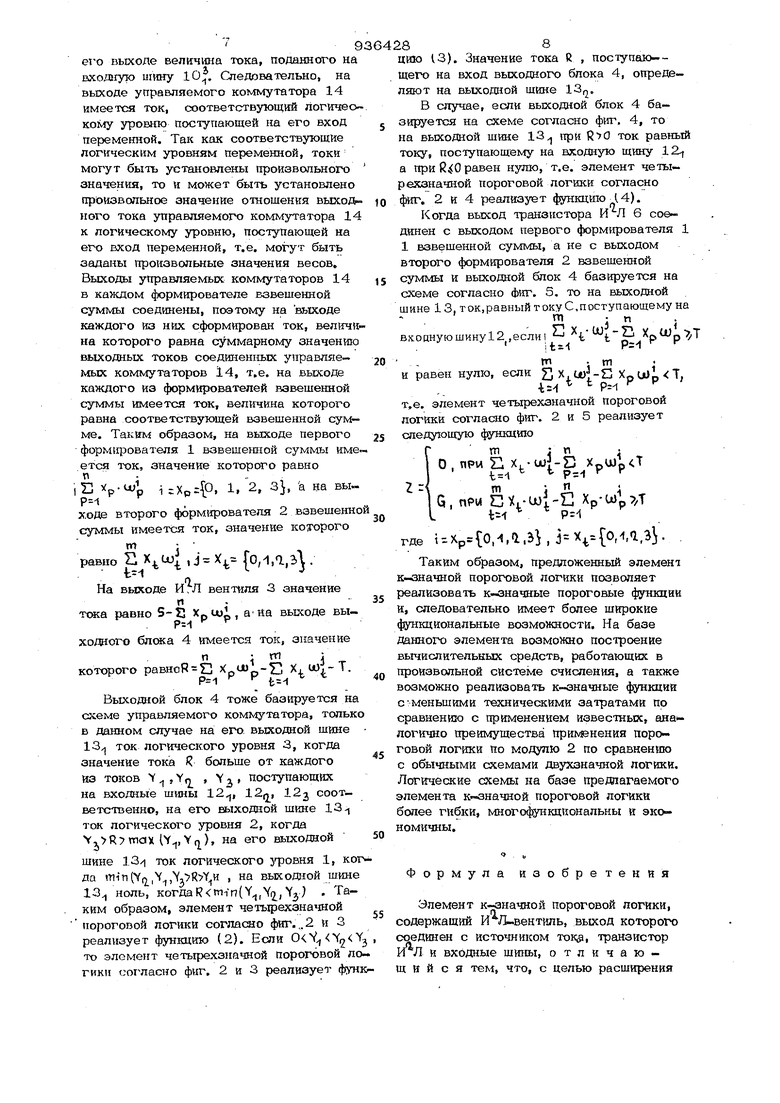

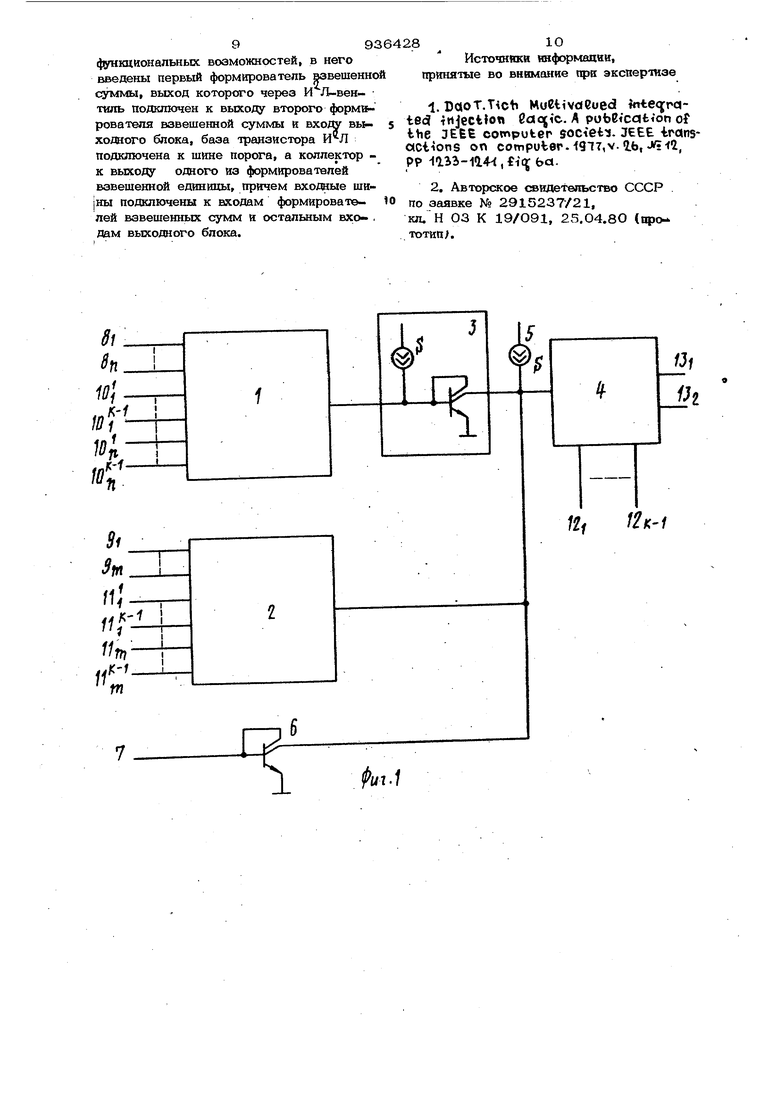

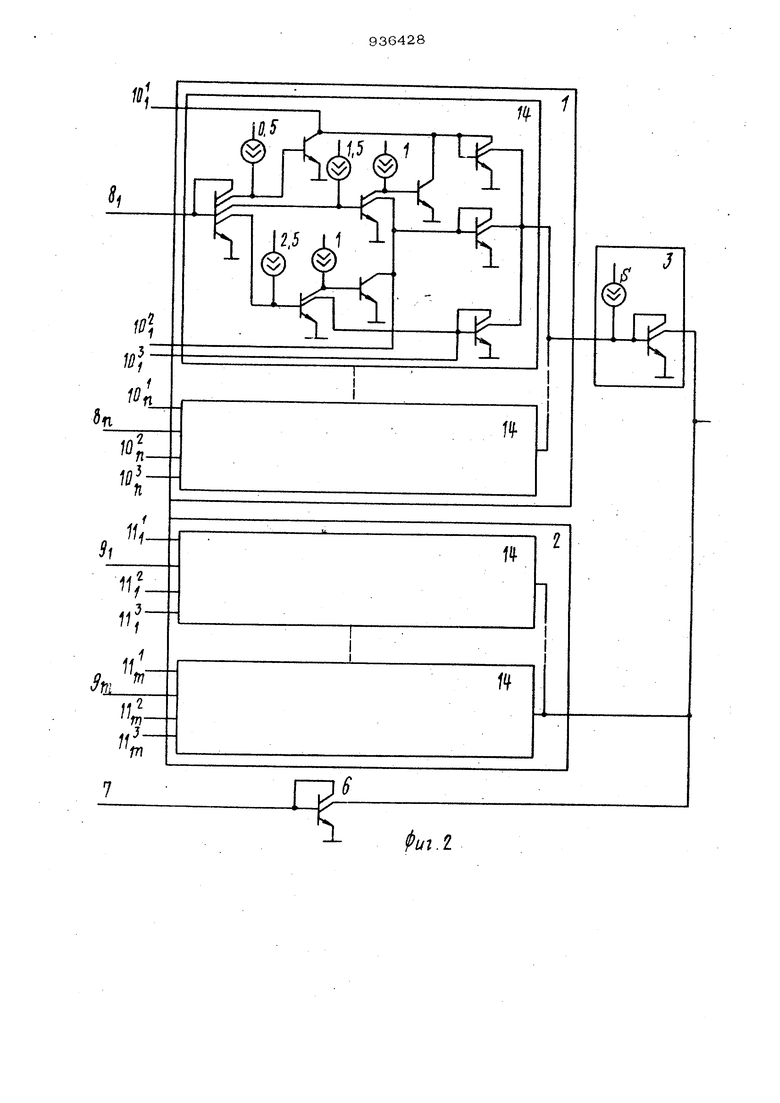

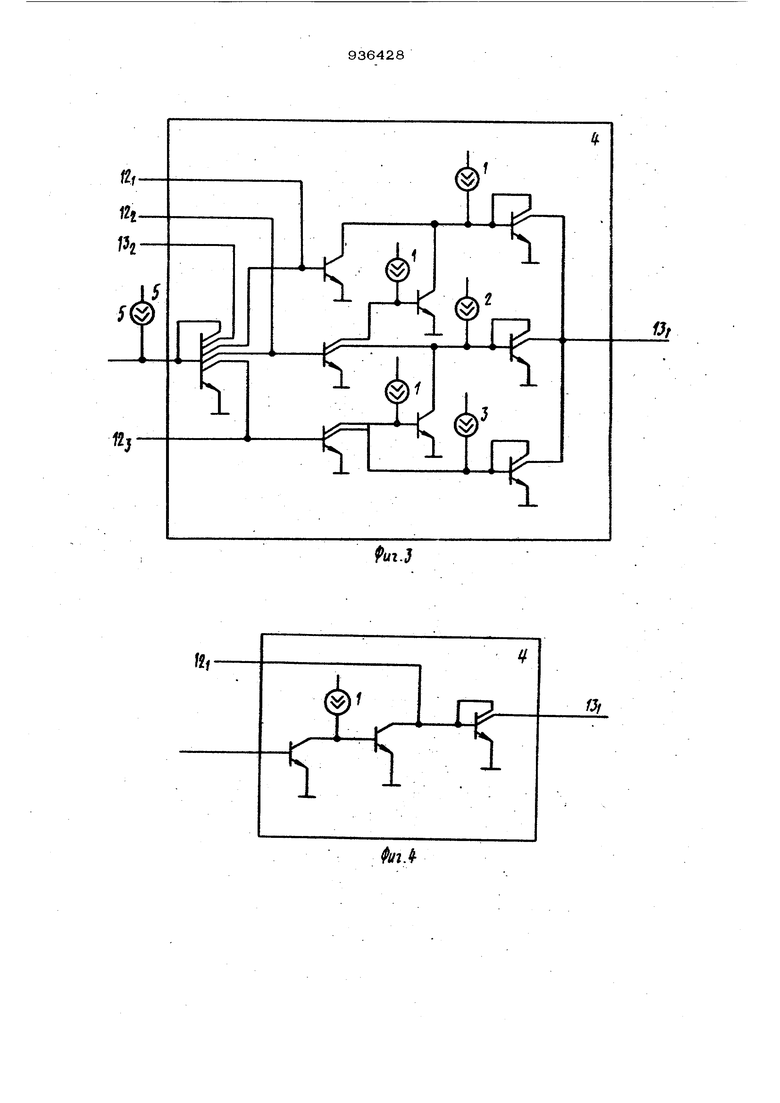

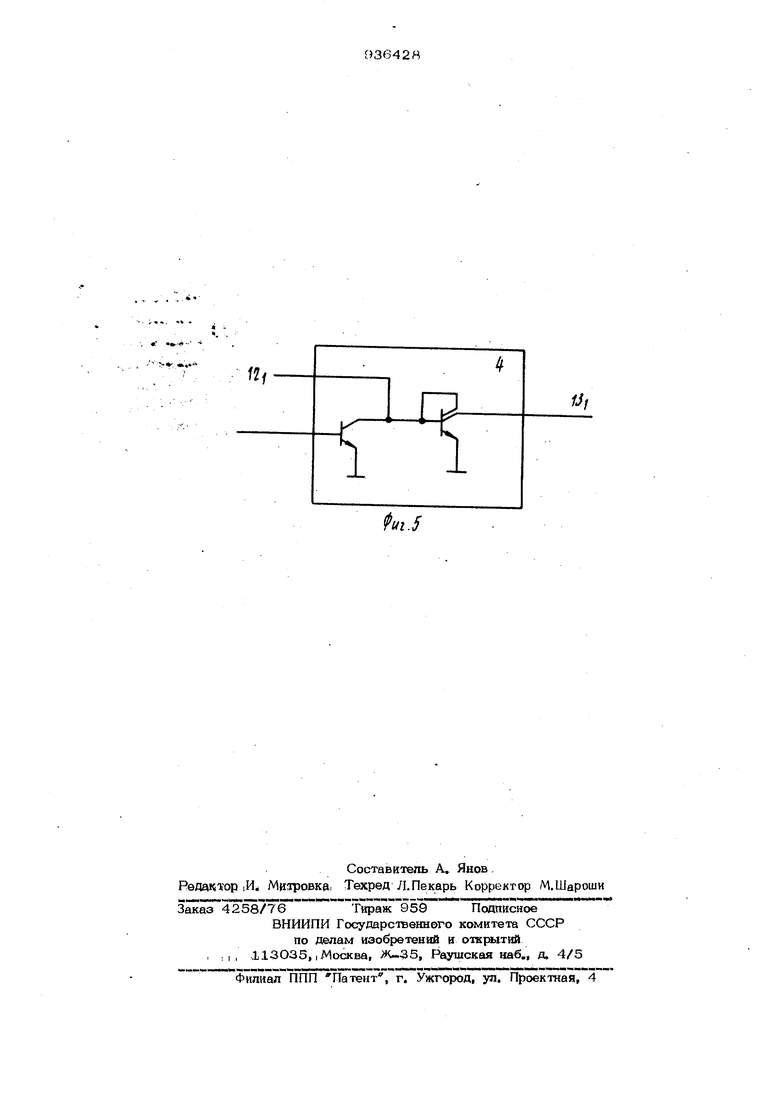

На фиг. 1 представлена блок-схема элемента k-значной пороговой логики; на фиг. 2 - элемент четырехзначной . пороговой логики, схема; на фиг. 3 то Же; на фиг. 4 - одна из возможных схем выходного блока элемента четыреханачной пороговой логики; на фиг. 5 другая нз возможных схем выходного блока элемента четьфехзначной пороговой логики. Элемент К-аначной пороговой логикИ содержит первый формирователь 1 взвешенной суммы, вторсй формирователь 2 взвешенной суммы, ИЛ вентиль 3, вьь. хояной блок 4, источник тока 5, тран зистор ИЛ 6, входную шину 7 порога. ходные шины 13, ,13. Первый 1 и второй 2 форми рователи взвешенных сумм содержат управляемые коммутаторы 14. Элемент 1 -значной пороговой логики работает следующим образом. Элемент, k значной пороговой логики содержит И Л вентиль 3, вь;КОД которого соединен с источником токи 5,а также транзистор 6, первый 1 и второй 2 формирователи взвешенных сумм, выходной блок 4, причем выход первого форми рователя 1 взвешенной суммы через И Л вентиль 3 соединен со входом выходного блока 4 и выходом второго формирователя 2 взвешенной суммы. Соединенный с входаой шиной. 7 порога транзистор 6 коллектором соединен с выходом одного из формирователей 1 или 2 взвешенной суммы. Также выходной блок 4 и формирователи 1 и 2 взвешенных сумм соединены с входными шинами.На входные шины 8.-.8j, первого формирователя 1 взвешенной суммы поотупают переменные , 1, 2,..., k-l -зна.чной логики, необходимые для форм рования первой взвешенной суммы п Ё, ,где lui, - веса переменных Х р- г для каждых рз логических уровней « , i Xp{0, 1,..,, . На входные шины 1 п 1 п1 in 1 о lu, -LU-,,.., iu,..., J.u, , J.U (2 ... 10 поступают входные величины И , и;,..., и;;..., H , ,.:., находящиеся в зависимости с переменны Хр пропорционально их весам ч)р ,..,| uJp для каждого логического уровня ,... Хр Я-1 соответственно. Таким образом, Up Xp-cji p. Например, если на пятую вход ную 85 ) поступает входной логический уровень t 5 ( на входную шину Ю необходимо подать входную величину U 3-«;, т.е. входную величину в соответствии с требуемы весом для логического уровня 3, п&. ременного f.. Следовательно , первая п. п взвешенная сумма J3 Х -шгЙ и РИ Р Р Pci Р Первый формирователь 1 взвешенной уммы формирует на своем выходе.знаение первой взвешенной суммы Д U в соответствии с логическими уровнями переменных Хр и требуемыми их весами На входные шины 9... 9 второго формирователя 2 взвешенной суммы поступают переменные Xt 0, 1,... -значной логики, необходимые для формирования второй взвешенной суммы W1 Q I (где to - веса переменных Х для каждых из логических уровней j j Xc i-- --i 111,, HQ,..., 111 ИО llm поступают входные величины V , V VV - V () i... Vf , v находящиеся в зависимости с переменными Х пропорционально их весам UJ,..., ю для каждого логического уровня ..., соответственно, аналогично первому формироват е лю. 1 взвешенной суммы. Таким образом,,-0)1. Следователь. тп ,, -ч. но, вторая взвешенная сумма С х, ц)- : «, 3 гС V, Второй формирователь 2 взве«. шенной суммы формид ет на своем выходе значение второй взвешенной суммы w |J в соответствии с логическими - I.-. уровнями переменных Х и требуемыми их вёЬами и) I . Значение: С U1 inociyna - Р ет с выхода первого формирователя 1 взвешенной суммы на вентиль 3, на выходе которого формируется значение S-G и . При этом необходимо условие JPM ui, , Источник тока 5 соединен с P Р выходами ИЛ вентиля 3, второго формирователя 2 взвешенной суммы и транзистора 6, который выполняет функцию повторителя значения порога Т, величина которого Поступает на входную Шину 7 порога. Таким образом, на вход выходного блока 4 поступает ток, значение которого равно разности между током 5, обеспечивающегося источником тока 5, и выходаыми токами И Л венти ля 3, второго формирователя 2 взвешен ной суммы и транзистора И Л 6, т.е. I 4 i 1 ,i 5- S-E и; -2 vJ-TrC ul-CVj-Т (1) РИ 1 in . Если E U.-C Vl T , TO на вход выходгP -l -tf Hot4 блока 4 с источника тока 5 посту пает ток, равный разности {i), в противном случае ток на вход выходного блока 4 поступать не будет. Выходной блок 4 предназначен реали зовать значение выходной функции Z в зависимости от наличия и величины ток на его входе. На входные шины 12 ..., 12.) поступают необходимые значения токов для реализации выходной функции Z . Например, на входные шины 12... 12 могут подаваться пороговые вел чины Y .... , при определенном превьшении которых входным током, равны разности Ц), на выходе выходного бло ка 4 формируется соответствующий логичесг ий уровень. Условно обозначим п R E UO-G Vi-T. Пусть на входные шй р Р tM ны 12,.. 12 будут поданы следующие величины:на 0,5, 1, 12 - 2,5, 12 - 3,5 и т,д. Тогда зна чение выходной функции Z может быть 0,приК О,5 1,при 1,,5 2,при 2,,5 3,при 3,,2,5 В этом случае в обобщенном виде элемент 1с..начной пороговой логики реализует функцию 0,при S T-nnin Cf,.... V,(. J 1,при T+mini4(j,...,V) Ij7/T X-, 2,при T4miM(Xj,...,4x.) , (V,Y) k-1, (Ч,...,Чу-, (V n} ;r. C EXpOU -Sx u)j ,i,...,M 1 ., frt j, 1 5 ,1,...Д-1} , .° При условии элемент It-значной пороговой логики реализует следующую функцию, к которой приводится функция 12) 28 0,при13 Т Ч 1,при Т + , 2,при T + jt-l, при . Выходная функция Z может формироваться и прутам образом. Например, на входную шину может подаваться вхоДгной сигнал Q с произвольным значением логического уровня; и поступать на выход выходного блока 4 при условии R О. В этом случае элемент k,-значной порсговой логики реализует в обобщенном виде следующую функцию 0,nPHi;XpWp-2X w.T .. п i G ,при С X 0)-2 X, ш; т Р tM Ь Возможны различные матоды формирования значения выходной функции 1 выходным блоком 4 в зависимости от наличия и величины тока на его входе. Также, на одной из выходных шин вы ходаого блока 4 может формироваться значение величины R . Кроме этого, выход транзистора И Л 6 может быть соединен с вь1ходом первого формирователя 1 взвешенной суммы, (не пoкaзaнo, а не с выходом второго формирователя 2 взвешенной . В этом случае на вход выходного блока 4 поступает ток, величина которого равна п . m : Р tH t Как пример реализации элемента -оначной пороговой логики на фиг. 2 и 3 приведена схема элемента четъфехзначной пороговой логики (). В данной схеме первый 1 и второй 2 формирователи взвешенных сумм базируются на управляемых коммутаторах 14, на вход каждого из которых поступает переменная. Управляемый коммутатор 14 пропускает на выход ток, значение которого находится в зависимости от логического уровня переменной. Например, если на входной шине 8 переменная Х равна нулю, то на выходе соединенного с входной шиной 8-, управляемого коммутатора 14 О, если Х равна логической единице, то на его выходе величина тока, поданного на входную шину Ю, если , то на его выходе величша тока, поданного на входную шину 10 и если , то на eto выходе величина тока, поданного на входную шину Ю, Спедоватепьно, на выходе управляемого коммутатора 14 имеется ток, соответствующий логичес кому уровню поступающей на его вход переменной. Так как соответствующие логическим уровням переменной, токи могут быть установлены произвольногчэ значения, то и может быть установлено произвольное значение отношения выход ного тока управляемого коммутатора 1 к логическому уровню, поступающей на его вход переменной, т.е. могут быть заданы произвольные значения весов. Выходы у1фавляемых коммутаторов 14 в каждом формирователе взвешенной суммы соединены, поэтому на выходе каждого из них сформирован ток, величи на которого равна суммарному значению выходных токов соединенных управляемых коммутаторов 14, т.е. на выходе каждого из формирователей взвешенной суммы имеется ток, величина которого равна соответствующей взвешенной сум ме. Таким образом, на выходе первого форм фователя 1 взвешенной суммы име ГОК, значение которого равно . 1. 2, 3}, а на выходе второго ф6рм1фователя 2 взвешенн суммы имеется ток, значение которого m равно И , j Х о,1,а,з . На выходе ИгЛ вентиля 3 значение п. тсжа равно S-S Xptulj, аНа выходе выр:ходного блежа 4 имеется ток, значение которого paBHoR D Xo JuX-S Х, U)-Т. Выходной блок 4 тоже базируется на схеме управляемого коммутатора, тольк в данном случае на его. ВЬЕКОДНОЙ шине 13 ток логического уровня 3, когда значение тока К. больше от каждого из токов ,(1 УЗ поступающих на входные шины 12, . 3 ветственно, на его выходной шине 13ток логического уровня 2, когда V,R7mc(X (Y, YIJ). на его вьгходной шине 13/1 ток логического зфовня 1, ко да (Тип(о,,,и , на выходной шине 13 ноль, когдаR min{Y,Y2.) КИМ образом, элемент четьфехзначной пороговой логики согласно фиг... 2 и 3 реализует фун1щию (2). Если то элемент четырехзначной пороговой л гики согласно фиг. 2 и 3 реализует фун 28 цию (3), Значение тока R , поступаю-щего на вход выходного блока 4, определяют на Быхош ой шине 13. В случае, если выходной блок 4 базируется на схеме согласно фиг. 4, то на выходной шине 13 при ток равный току, поступающему на входную щину 12 а при (0 равен нулю, т.е. элемент четырехзначной пороговой логики согласно фиг. 2 и 4 реализует функцию Ч 4). Когда выход транзистора И Л 6 соединен с выходом первого форм1фователя 1 1 взвешенной суммы, а не с выходом второго формирователя 2 взвешенной суммы и выходной блок 4 базируется на схеме согласно фиг. S. то на выходной шине 13, ток.равный г оку С,поступающему на i-g s В соцнуюшину12|,если {. -Г г m и равен нулю, если S X, U) , М 9--Л т,е. элемент четырехзначной пороговой логики согласно фиг. 2 и 5 реализует следующую функцто m; п О, ПРИ С г m1 п G, прм GX.-u)i-I Хр-и)1,д IЫ t-.,-i,a.3iJ vt .iТаким образом, предложенный элемент к-значной пороговой логики позволяет реализовать к-значные пороговые функции и, следовательно имеет более широкие 4отнкциональные возможности. На базе Данного элемента возможно построение вычислительных средств, работающих в произвольной системе счисления, а также возможно реализовать к-значные функций сменьшими техническими затратами по сравнению с применением известных, аналогично преимущества применения пороговой логики tio модулю 2 по сравнению с обычными схемами двухзначной логики. Логические схемы на базе предаагаемого элемента к- начной пороговой логики более гибки, мнoгo4Q кц(Ioнaльны и эк1 номичны. Формула изобретения Элемент к начной пороговой логики, содержащий И Л-вентиль, выход которого соединен с источником то1ф| транзистор ИЛ и входные шшсы, о т л и ч а ю щ и и с я тем, что, с целью расширения 99364 функциональных воаможностей, в него введены первый формирователь взвешенной суммы, выход которого через И Л-вентиль подключен к выходу второго форм. рователя взвешенной суммы и вхо/у вы- s ---e-. r r , ХОДНОГО блока, база транзистора подключена к шине порога, а коллектор к выходу одного из формирователей взвешенной единицы, причем входные ,,о,к«ны к . ..а™- ,. Г„ - 2810 Источники информации, принятые во внимание при экспертеае 1. DcloT.Ticli Moetivdeoed tMjectJon Cdcjic. A pobetcdtion of ЛЕБЕ compoter society. ЛЕЕЕ iransactions on computer. 19l7,v.5.b. Пгч А1ЛлАл м.. РР ni3-ia44,fi(5ba. v 2. Авторское жидетельство СССР ., - н о« К- ia/ow ;|.o4.80 ,.р тотип/.

О

Hi

fJ)

Авторы

Даты

1982-06-15—Публикация

1980-10-31—Подача