(З) ФОРМИРОВАТЕЛЬ ПЕРЕНОСА (ЗАЕМА) К-ЗНАЧНиЙ ЛОГИКИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный элемент к-значной логики | 1980 |

|

SU871337A1 |

| Элемент К-значной пороговой логики | 1980 |

|

SU936428A1 |

| Многофункциональная схема многозначной логики | 1980 |

|

SU930681A1 |

| Четырехуровневый сумматор-вычитатель | 1987 |

|

SU1422396A1 |

| Инжекционный сумматор-вычитатель | 1987 |

|

SU1471305A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ СРАВНЕНИЯ k-ЗНАЧНОЙ ПЕРЕМЕННОЙ С ПОРОГОВЫМ ЗНАЧЕНИЕМ | 2014 |

|

RU2546085C1 |

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| Устройство для вычисления полинома | 1983 |

|

SU1179323A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛОВ | 2000 |

|

RU2195014C2 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

I

Изобретение относится к вычисли-v тельной технике и может быть использовано в цифровых вычислительных устройствах, работающих с применением К-значной логики.

Известны схемы К-значной логики, реализация которых осуществляется на основе двухзначных логических элементов на переключателях тока| 13.

Недостатком известных схем является невозможность использования схем других типов.

Известен полный сумматор К-значной логики на базе схем на переключателях тока,, содержащий соединенный с источником логических уровней формирователь переноса, обеспечивающий формирование переноса при суммировании и заема при вычитании ЗНедостатком сумматора К-значной логики также является невозможность использования при синтезе схем других типов, что ограничивает его функциональные возможности.

Цель изобретения - расширение функциональных возможностей, т.е. создание формирователя, обеспечивающего формирование как переноса при сложении двух чисел, так и формирование заема при их вычитании в К-значной логике, использующей не только схемы на переключателях тока но и другую элементную базу.

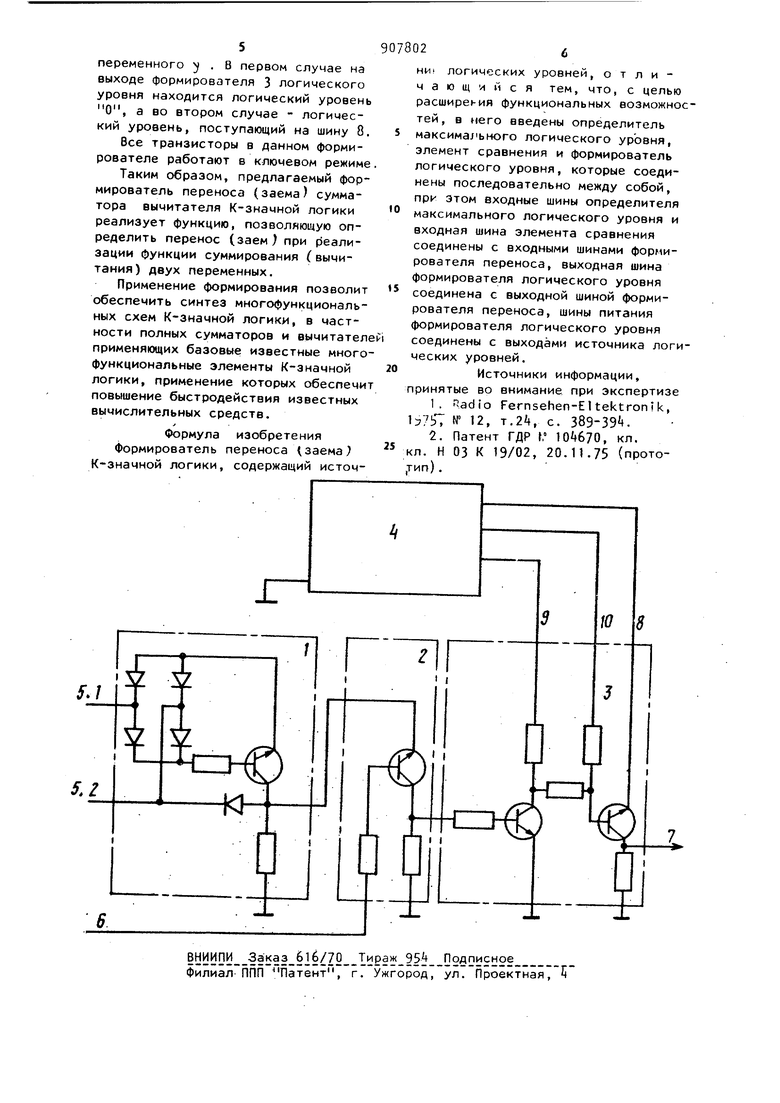

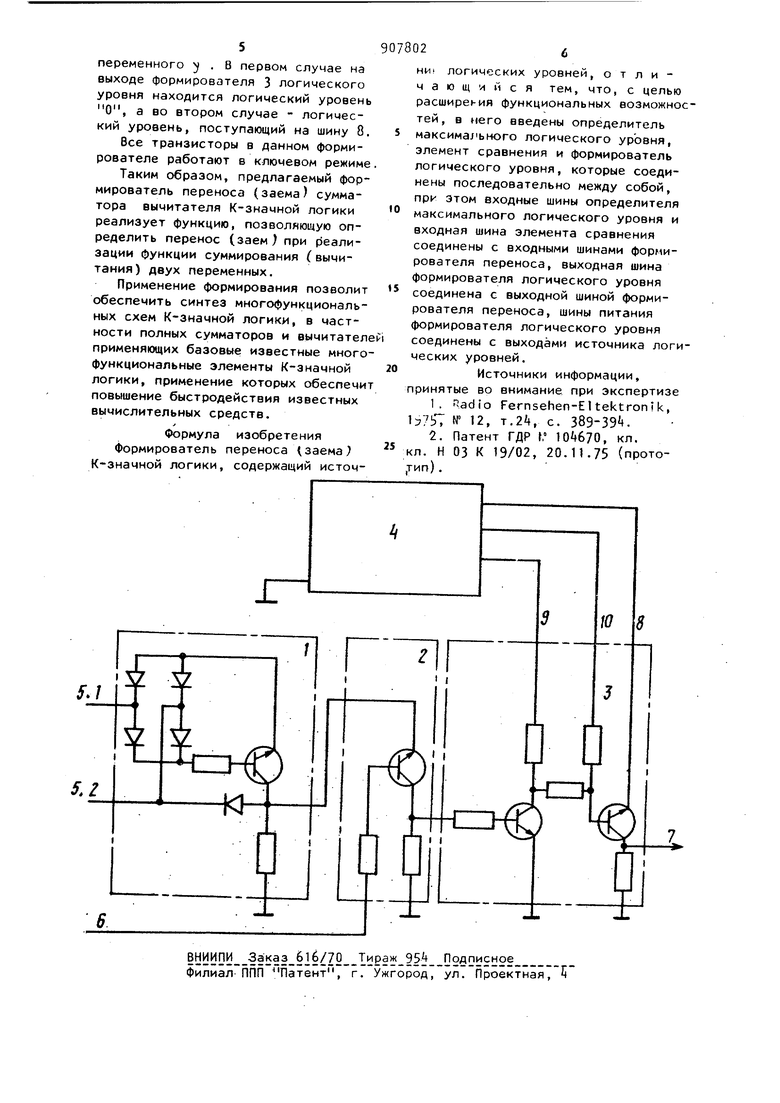

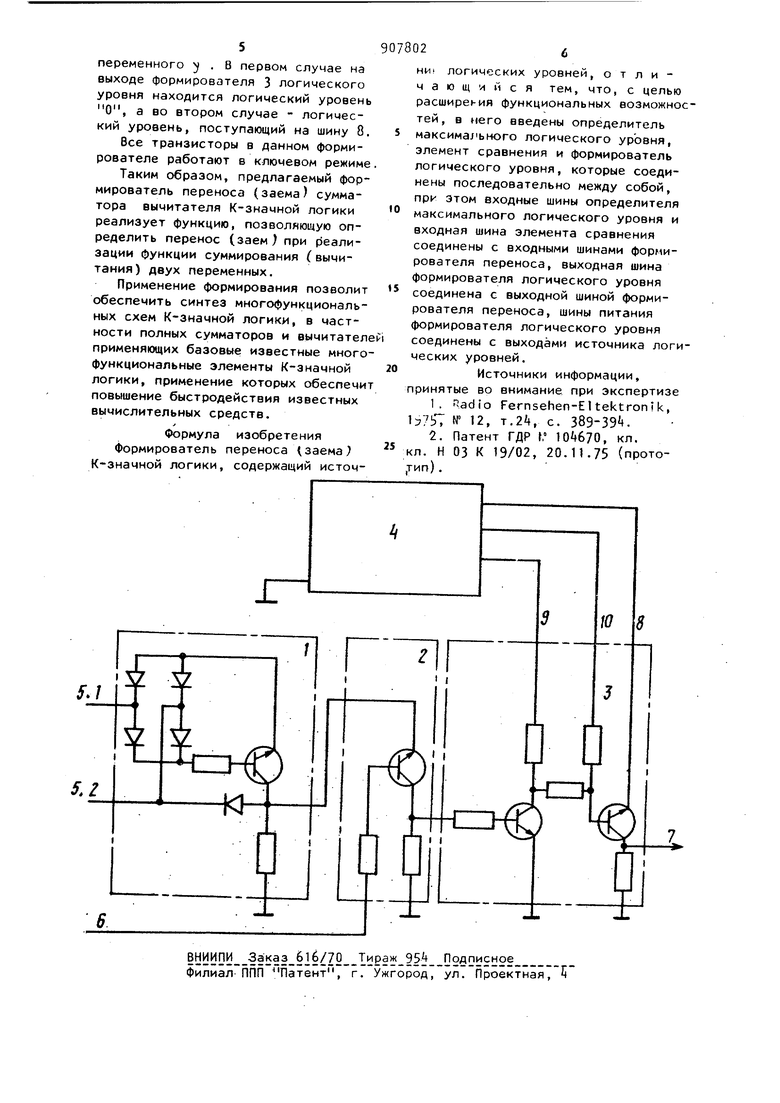

Указанная цель достигается тем, что в формирователь переноса ( заема) К-значной логики, содержащий источник логических уровней, введены определитель максимального логического уровня, элемент сравнения и формирователь логического уровня, которые соединены последовательно между собой, при этом (Входные шины определителя максимального логического уровня и входная шина элемента сравнения соединены с входными шинами формирователя переноса, выходная шина формирователя логического уровня соединена с выходной шиной формиравателя переноса, шины питания фор мирователя логического уровня соединены с выходами источника логичес ких уровней. На чертеже предстаолена схема фо мирователя переноса ( даема) суммато ра ifвычитателя) К-значной логики, Формирователь содержит определитель 1 максимального логического уровня, элемент 2 сравнения, формирователь 3 логического уровня, исто ник логических уровней, входные шины 51| , входную шину 6, выходную шину 7 шины 8, 9 и 10. Формирователь переноса ( заема ) сумматора (вычислителя ) К-значной логики работает следущим образом. Рассмотрим работу формирователя при отрицательном кодировании, когда логические уровни определяются величиной отрицательного напряжения. С источника k логических.уровней на шины, соединяющие его с формирователем 3 логического уровня, подают следующие логические уровни: на ,шииу 8 - логический уровень, который необходимо получить на выходной шине 7, на шину 9 - максимальный логический уровень, на шину 10 логический уровень необходимого напряжения смещения, который на один логический уровень выше от поданного на шину 8. Когда на шину 8 подан максимальный логический уровень, то он подается также и на ojHHy 10. Пусть на входные шины 5.1, 5.2 определителя 1 максимального логического уровня поданы логические уровни переменных X, У соответствен но , а на входную шину 6 элемента 2 сравнений - логический уровмк функции сложения f(X,V) modi; без учета переноса. В этом случае определител 1 максимального логического уровня работает таким образом, что на его выходе появляется больший из логиче ких уровней пере 1еиных X ,V т.е. тах(Х,У ). Этот максимальный логический уровень сравнивается элементом 2 сравнения с /югическим уровне функции сложения f {%, y)modk без учета переноса, т.е. при max(X,V) if(), 5) modk транзистор элемента 2 сравнения закрыт и на, его выходе по является логический уровень О,, а при max(y,).f {H,)modk, транзистор элемента 2 сравнения открыт и йа его выход поступает входной логический уровень, т.е. максимальный логический уровень из переменных х N. Если на вход формирова.теля 3 лоrkf4ecKoro уровня поступает логический уровень О, то его транзисторы закрыты и на выходной шине 7 имеетс ч логический уровень О. Если же на вход формирователя 3 логического уровня поступает логический уровень, отличный от О, то его транзисторы открыты и на- выходной шине 7 имеется логический уровень, поступающий на Шину 8, Таким образом, формирователь реализует функцию FU,V)niodK ,{Q,l riKSx(X,V)f(X,V)rviodK -{t, «wiMXiVnfCx.VJmodK Де ,1,..,.4ол-.Лн5, 24o...,VHi, «.- «--}5; :-jr V4.l т.е. функциюj позволяющую определить перенос при суммировании двух логических уровней К-значной логики. 8 случае подачи на одну из входных шин 5.1, 5.2 логического уровня переменного , а на другую логического уровня О также на входную шину 6 элемента 2 сравнения логического уровня переменного У , формирователь реализует функцию . г/ л 0| ПР F(x,y).,,; р где X o,1,.,.,k-l} .1,. ..-1 Z |0,1 k-l, позволяющую определить заем при реализации функции вычитания двух переменных . . f (X, ) fnodk4k , п ри ХкУ В этом случае определитель 1 максимального логического уровня работает как повтс ритель переменного У , так как на его вторую входную шину подан логический уровень О. Таким образом, элемент 2 сравнения сравнивает логические уровни переменных / и ( . Если , то его транзистор закрыт и на выход элемента 2 срав нения поступает логический уровень О, а если Х , то его транзистор открыт и на вь1ходе эл(вмента 2 срав.нения присутствует логический уровень

Авторы

Даты

1982-02-23—Публикация

1980-06-13—Подача