СП

СД 4 СЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения в резервированной многопроцессорной системе | 1987 |

|

SU1501079A1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

| Резервированная вычислительная система | 1989 |

|

SU1624470A1 |

| СПОСОБ КОРРЕЛЯЦИОННОГО ПРИЁМА СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2237978C2 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU940148A1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| Резервированная система | 1982 |

|

SU1101827A1 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

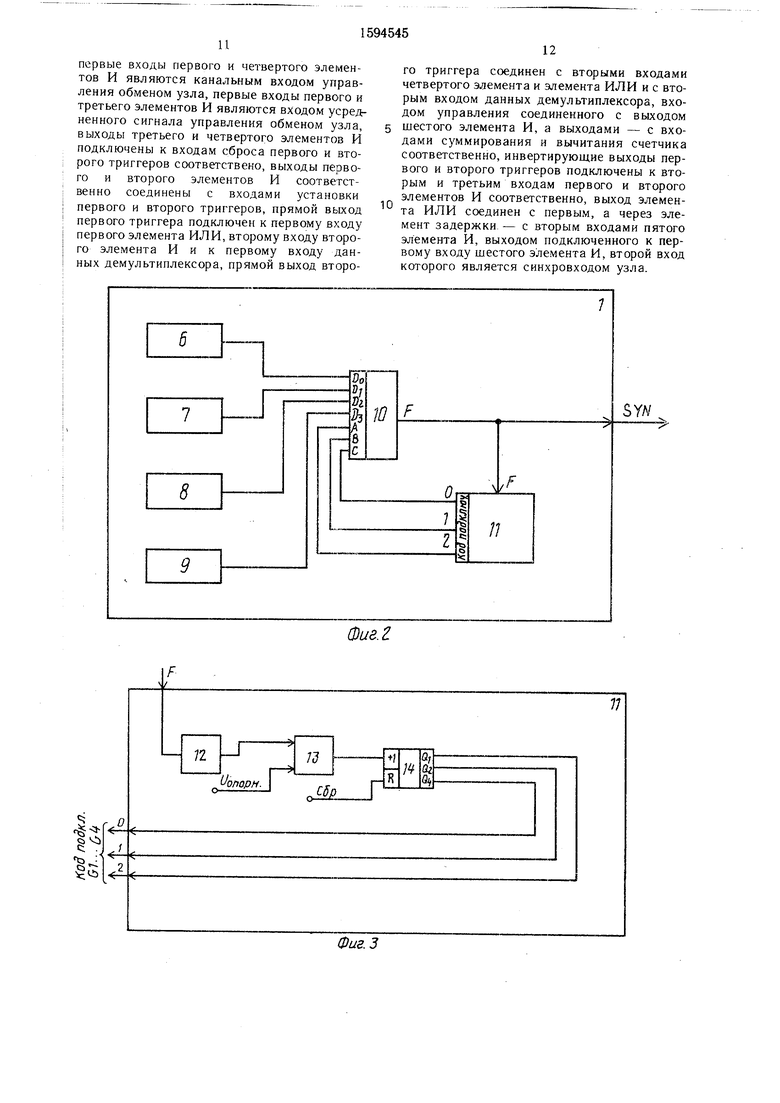

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления технологическими процессами. Цель изобретения - повышение надежности устройства. Устройство содержит блок 1 генераторов, предназначенный для синхронизации процессоров и вырабатывающий синхроимпульсы SYN, блок 2 процессоров, содержащий три процессора, работающих независимо, параллельно и синхронно, выполняющих одинаковые инструкции /команды/, блок 3 сопряжения процессоров, предназначенный для мажоритирования управляющих сигналов и данных, а также для сопряжения трех процессоров с тремя независимыми наборами внешних устройств. Блок 4 управления задержками предназначен для индивидуальных задержек синхроимпульсов каждому процессору в пределах допустимых взаимных рассогласований между процессорами и вырабатывает соответственно степени рассогласования три серии синхроимпульсов SYN 1, SYN 2, SYN 3. Блок 5 слежения за рассинхронизацией процессоров предназначен для оценки степени взаимной рассинхронизации процессоров и выработки соответствующего кода рассинхронизации для блока 4. 3 з.п. ф-лы, 22 ил.

аз,/

Изобретение относштя к вычислительной технике и может быть использовано в автоматизированных системах управления технологическими процессорами (АСУ ТП), где ошибочность функционирования АСУ может иметь катастрофические последствия, например в АСУ aTOMHoi r энергетики несвоевременный ввод унравляющего воздействия может иметь катастрофические последствия.

Цель изобретения - повышение надежности устройства.

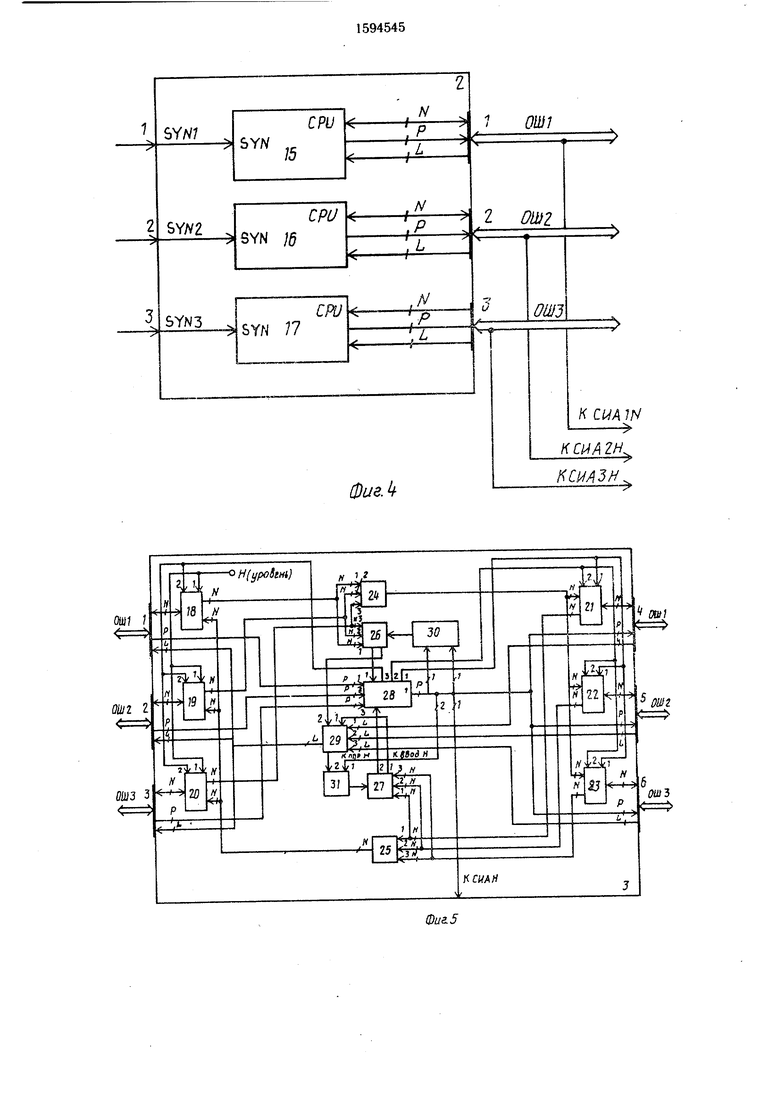

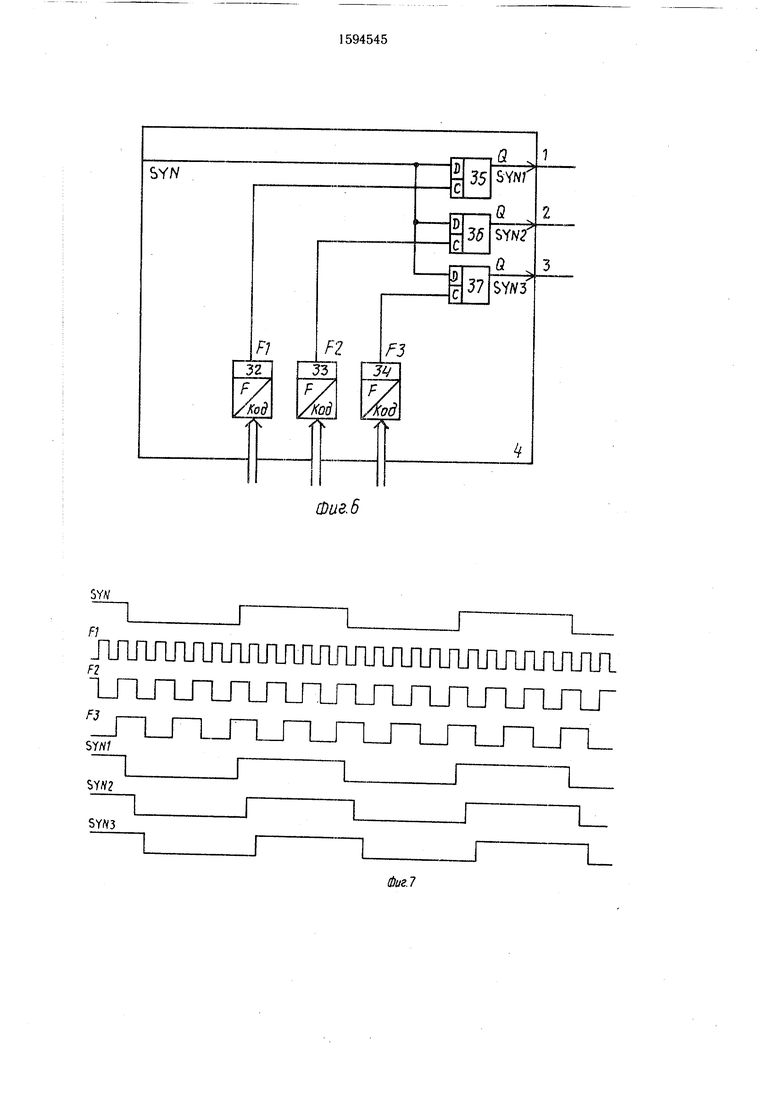

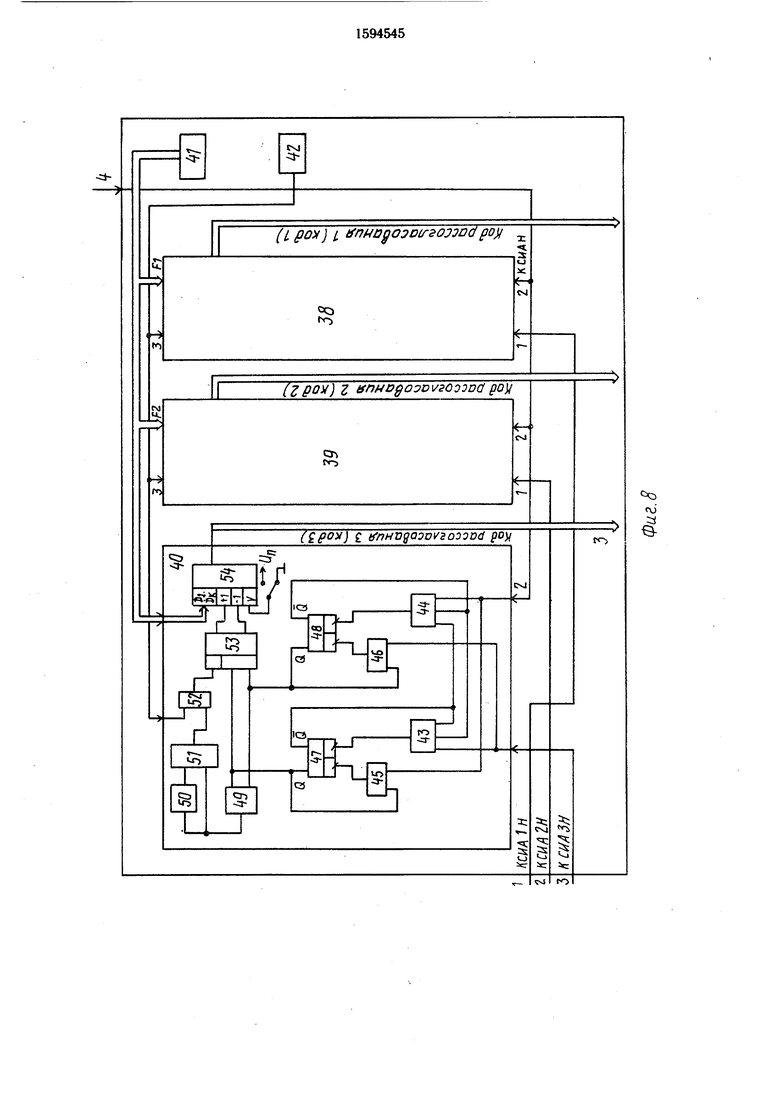

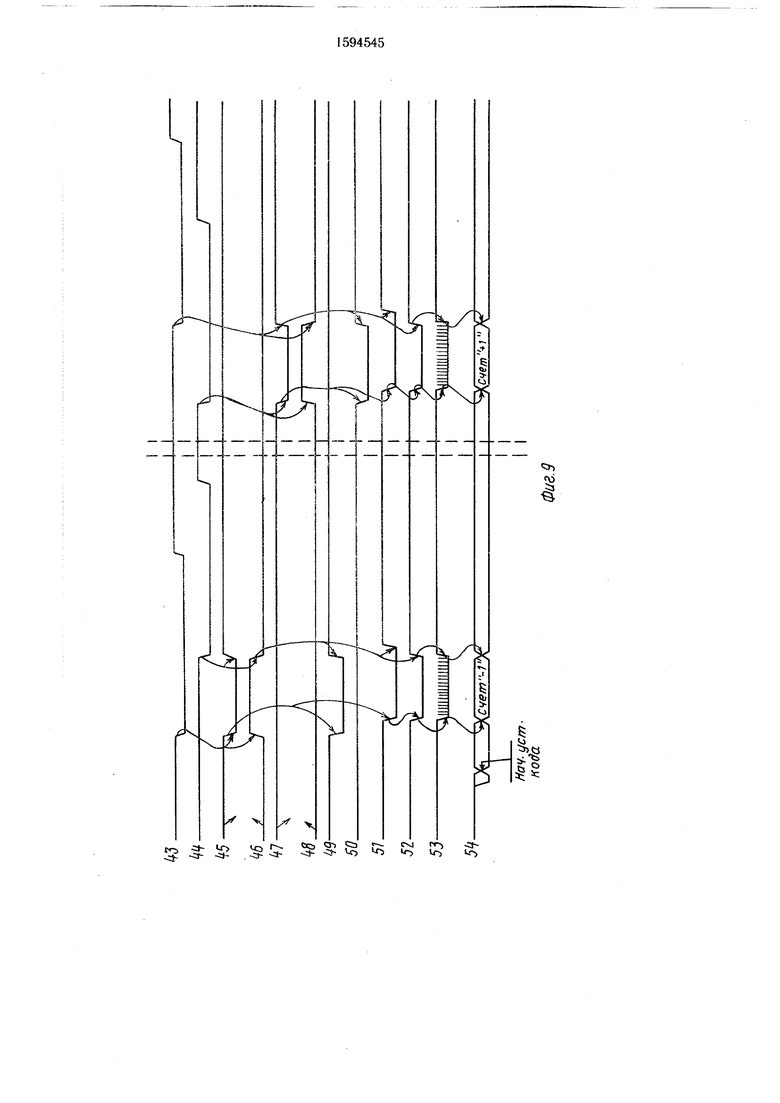

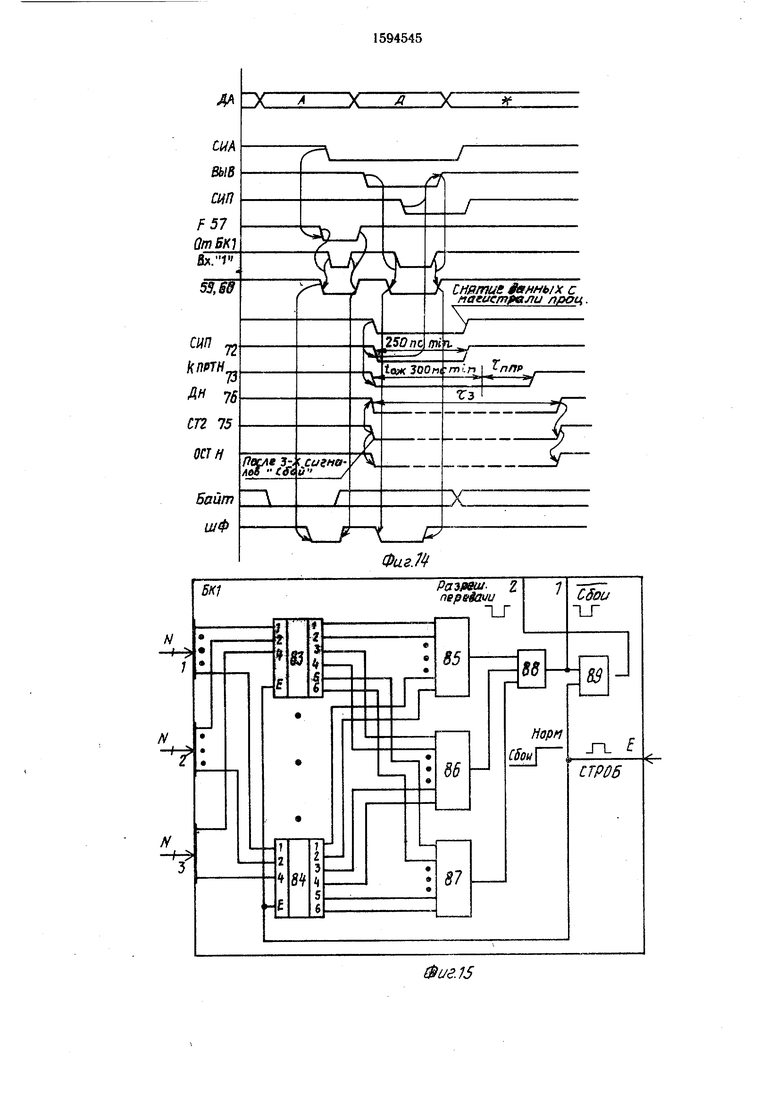

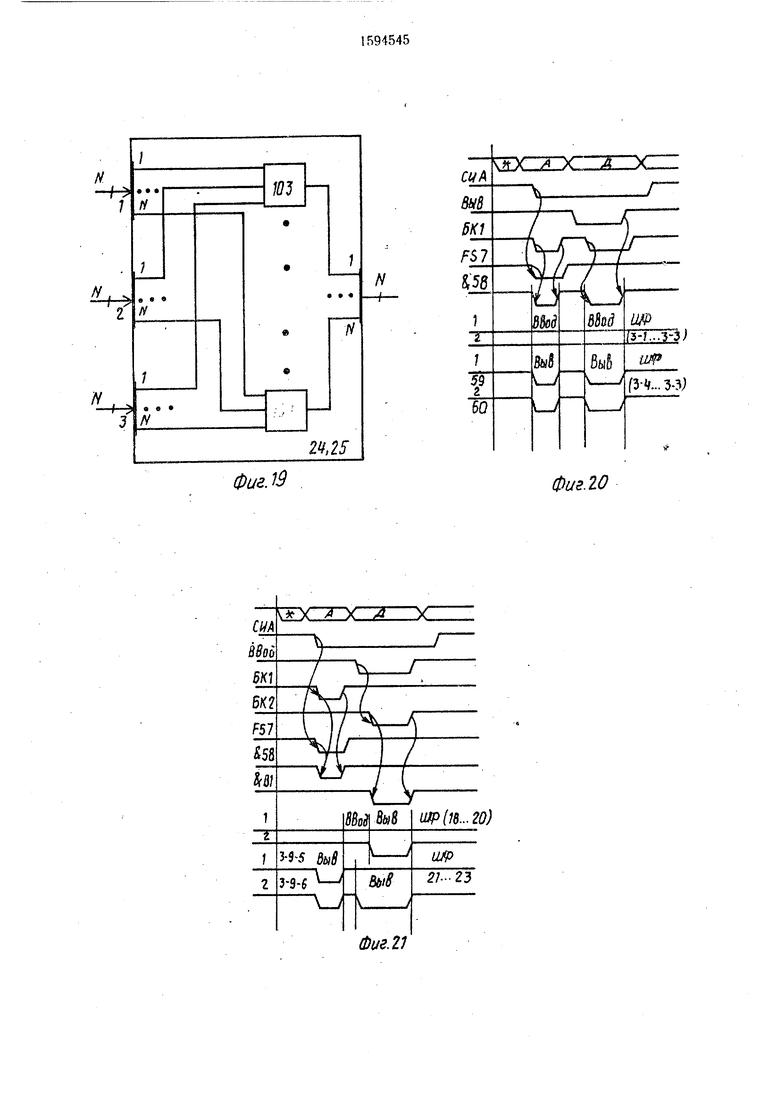

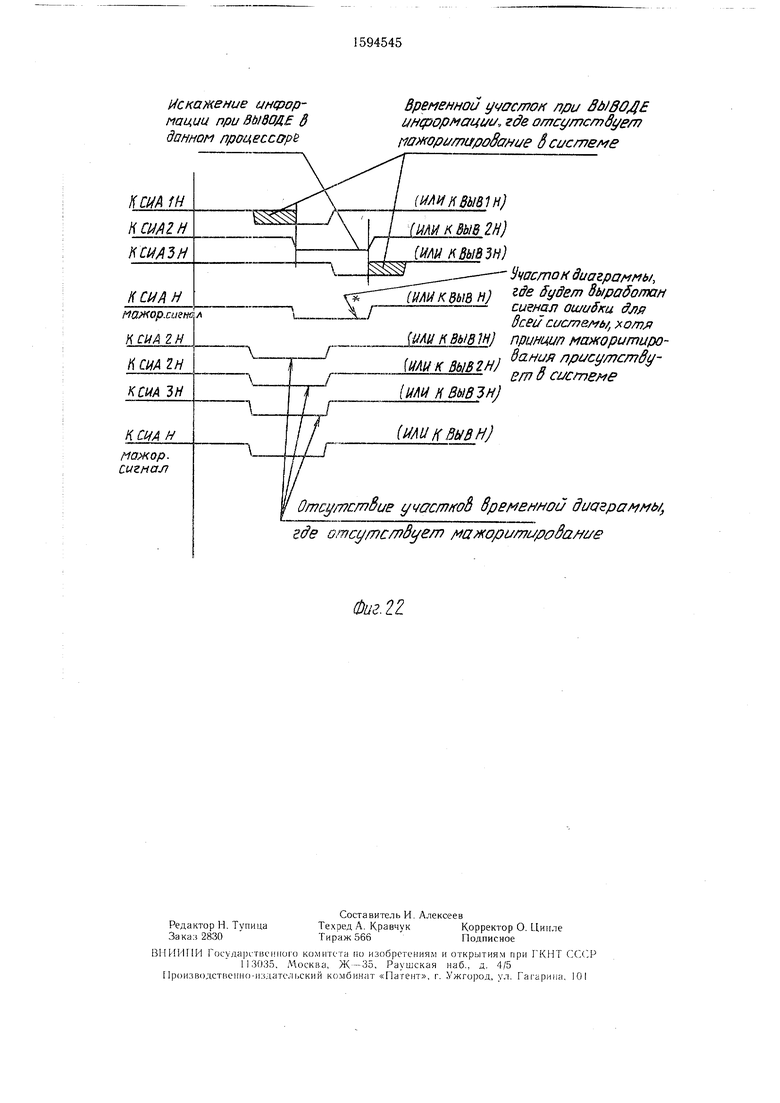

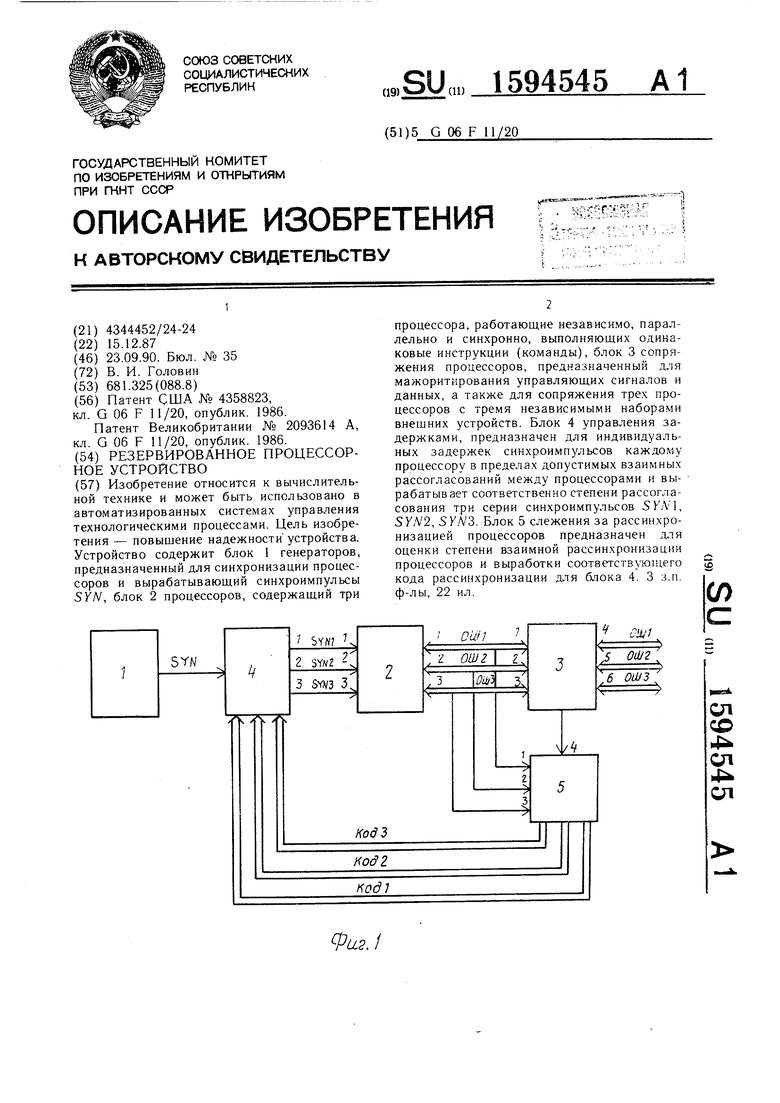

На фиг. приведена функциональная , схема предлагаемого устройства; на фиг. 2 - функциональная схема .блока генераторов; на фиг. 3 - функциональная схема блока контроля синхросигналов; на фмг. 4 - функциональная схема блока процессоров; на фиг. 5 - схема блока сопрял ения процес- соров; на фиг. G - функциональная схема блока управления задержками; на фиг. 7 - временная диаграмма работы блока управления задержками; на фиг. 8 - функциональная схема блока слежения за рассинхро- низацией; на фиг. 9 -- временная диаграмма работы блока слежения за рассинхронизацией процессоров; на фиг. 10 -- функциональная сх1}ма первого блока синхронизЕщии; на фиг. 1 - функциональная схема первого блока стробирования; на фиг. 12 - сре- менная диаграмма работь блока; на фиг. 13 .- функциональная схема второго блока синхрО 1изации; на фиг. 4 - временная диаграмма работы блока; на фиг. 15 и 16 - функциональные схемы первого и второго блоков контроля; на фиг. 7 - функциональная схема второго блока стробирования; на фиг. 18 - временная диаграмма работы блока; на фиг. 19 - функциональная схема разводки канальных сигналов в блоке мажоритарных элементов к мажоритарным элементам; на фиг. 20 и 21 -- временная диаграмма упра(5ления процессами «Вывод и «Ввод п блок сопряжения процессоров; на фиг. 22 - временная диаграмма, иллюстрирующая преимущественно предлагаемого устройства.

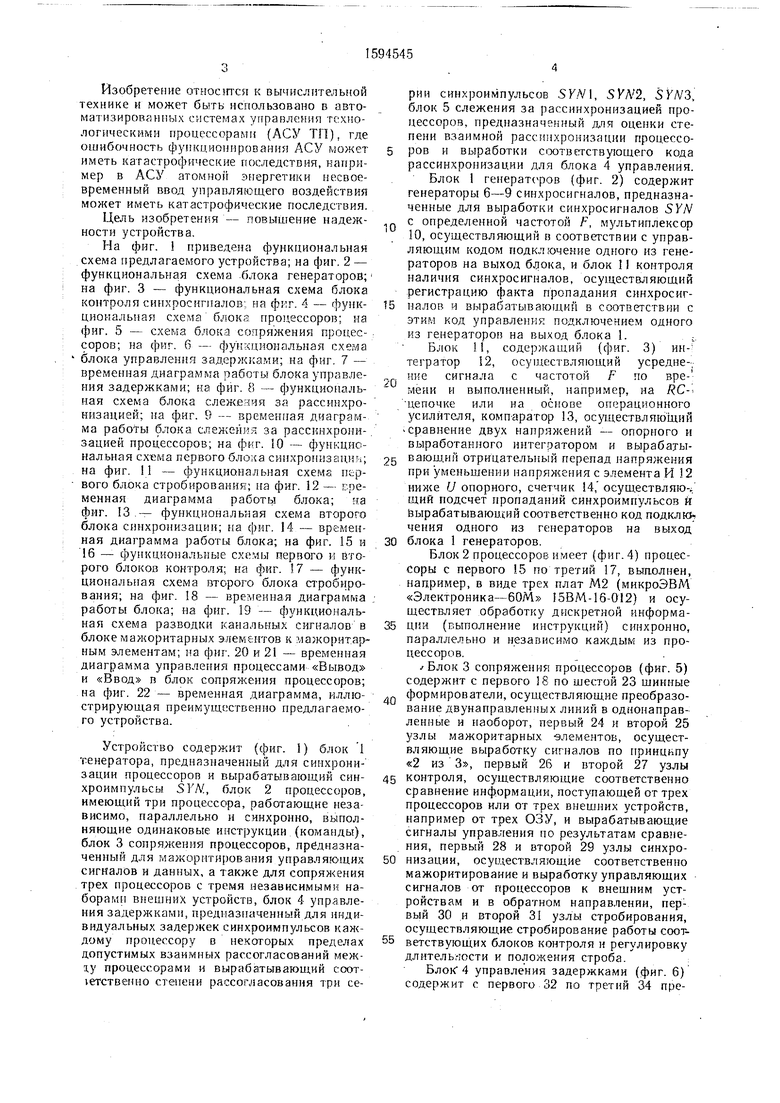

Устройство содержит (фиг. 1) блок 1 генератора, предназначенный для синхрони- зации процессоров и вырабатывающий синхроимпульсы SYN., блок 2 процессоров, имеющий три процессора, работающие независимо, параллельно и синхронно, выполняющие одинаковые инструкции. (команды), блок 3 сопряжения процессоров, предназначенный для мажорнтирования управляющих сигналов и данных, а также для сопряжения .трех процессоров с тремя независимыми наборами внешних устройств, блок 4 управления задержками, предиазпаченный для индивидуальных задержек синхроимпульсов дому процессору в некоторых пределах допустимых взаимных рассогласований меж- ly процессорами н вырабатывающий соот- lercTBeHHO степени рассогласования три серии синхроимпульсов SYN, 5КЛ 2, 5} yV3, блок 5 слежения за рассинхронизацией процессоров, предназначенный для оценки степени взаимной рассинхронизации процессоров и выработки С1эответствующего кода рассинхронизации для блока 4 управления. Блок 1 генерат(ров (фиг. 2) содержит генераторы 6-9 синхросигналов, предназначенные для выработки синхросигналов SYN

Q с определенной частотой f, мультиплексор 10, осуществляющий в соответствии с управляющим кодом подключение одргого из генераторов на выход блока, и блок 1 контроля наличия синхросигналов, осуществляющий регистрацию факта пропадания синхросиг5 налов и вырабатывающий в соответствии с этим код управления подключением одного из генераторов на выход блока 1..;.

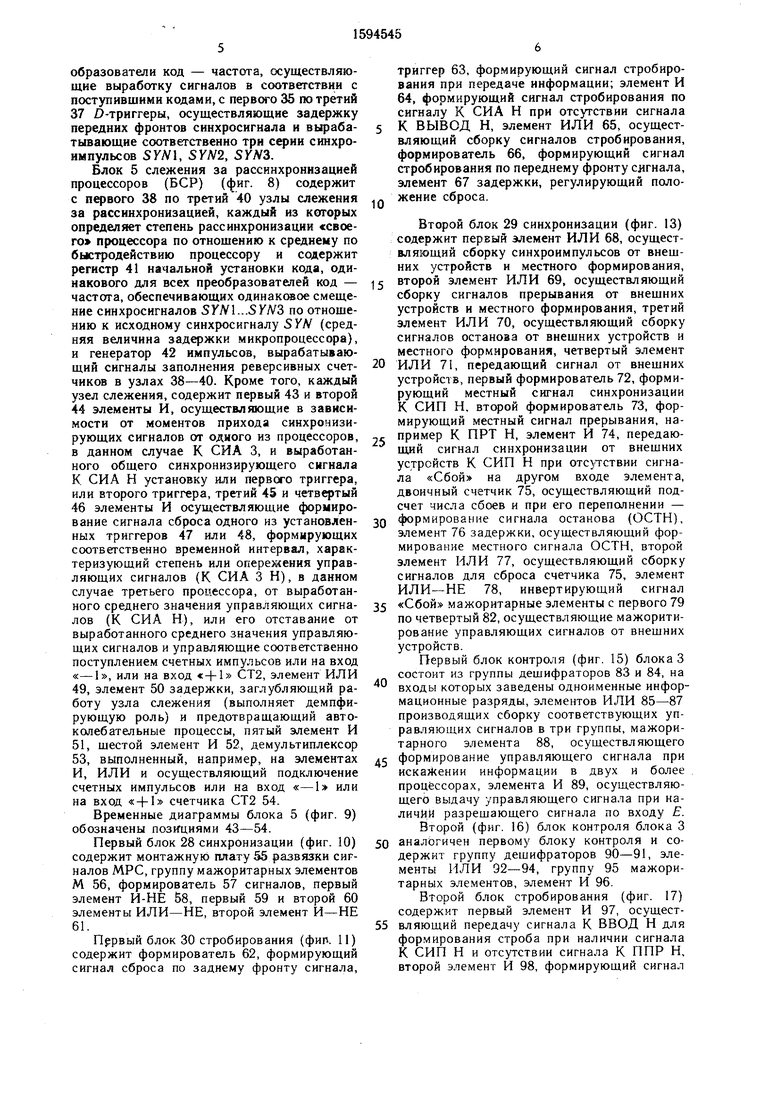

Блок , содержащий (фиг. 3) ин- тегратор 12, осуществляющий усредне-., ние сигнала с частотой F по времени и выполненный, например, на RC цепочке или на основе операционного

усилителя, комп-аратор 13, осуществляющий

-сравнение двух нанряжений - опорного и

выработанного интегратором и вырабаты5 вающ,ий отрицательный перепад напряжения при уменьшении напряжения с элемента И 12 ниже и опорного, счетчик 14, осущ,ествляю-/ щий подсчет пропаданий синхроимпульсов и вырабатывающий соответственно код подклкь чения одного из генераторов на выход

0 блока 1 генераторов.

Блок 2 процессоров имеет (фиг. 4) процессоры с первого 15 по третий 17, выполнен, например, в виде трех плат М2 (микроЭВМ «Электроника--60М {5ВМ-16-012) и осуществляет обработку дискретной информа5 ции (выполнение инструкций) синхронно, параллельно и независимо из процессоров.

Блок 3 сопряжения процессоров (фиг. 5) содержит с первого 18 по шестой 23 щинные

Q формирователи, осуществляющие преобразование двунаправленных линий в однонаправленные и наоборот, первый 24 и второй 25 узлы мажоритарных елементоБ, осуществляющие выработку сигналов по принципу «2 из 3, первый 26 и второй 27 узлы

5 контроля, осуществляющие соответственно сравнение инф ормации, поступающей от трех процессоров или от трех внещних устройств, например от трех ОЗУ, и вырабатывающие сигналы управления по результатам сравнения, первый 28 и второй 29 узлы синхро0 низации, осуществляющие соответственно мажоритирование и выработку управляющих сигналов от гфоцессоров к внещним устройствам и в обратном направлении, первый 30 и второй 31 узлы стробирования, осуществляющие стробирование работы соот5 ветствующих блоков контроля и регулировку длительности и положения строба.

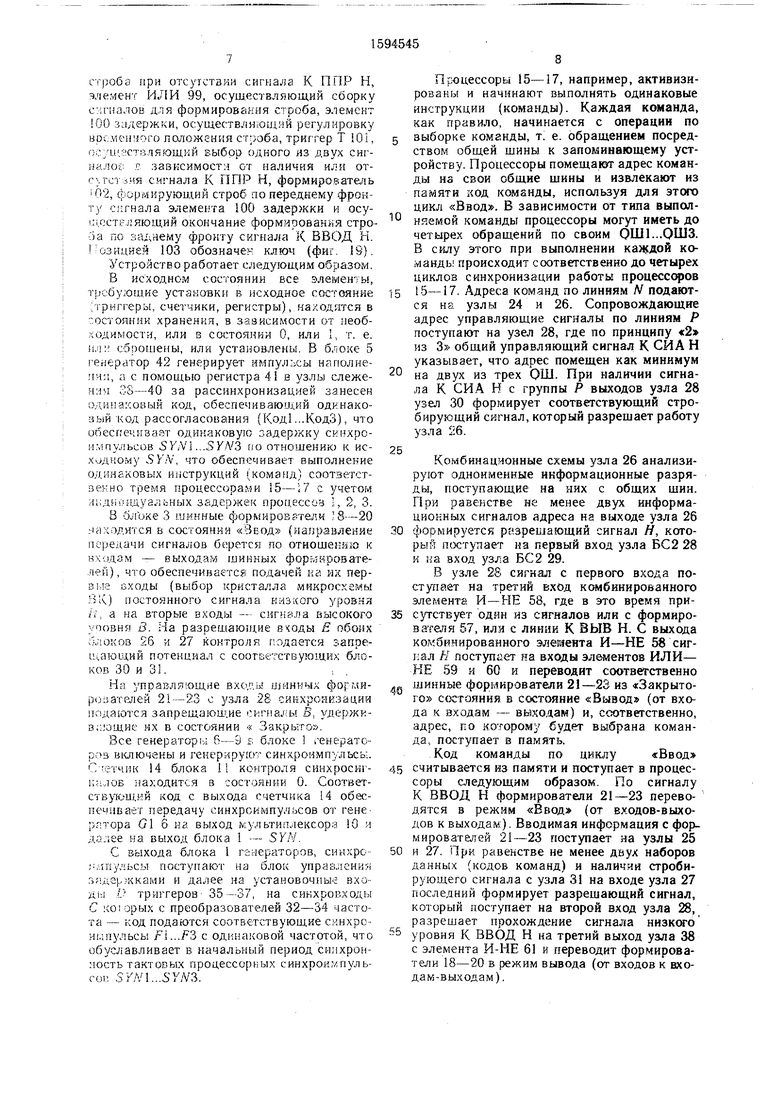

Блок 4 управления задержками (фиг. 6) содержит с первого 32 по третий 34 преобразователи код - частота, осуществляющие выработку сигналов в соответствии с поступившими кодами, с первого 35 по третий 37 D-триггеры, осуществляющие задержку передних фронтов синхросигнала и вырабатывающие соответственно три серии синхроимпульсов SYN, SYN2, SYN3.

Блок 5 слежения за рассинхронизациеб процессоров (БСР) (фиг. 8) содержит с первого 38 по третий 40 узлы слежения за рассинхронизацией, каждый из которых определит степень рассинхронизации ссвое- го процессора по отнощению к среднему по быстродействию процессору и содержит регистр 41 начальной установки кода, одинакового для всех преобразователей код - частота, обеспечивающих одинаксжое смещение синхросигналов SYNI...SYN3 по отнощению к исходному сиихросигналу SYN (средняя величина задержки микропроцессора), и генератор 42 импульсов, вырабатывающий сигналы заполнения реверсивных счетчиков в узлах 38-40. Кроме того, каждый узел слежения, содержит первый 43 и второй 44 элементы И, осуществляющие в зависимости от моментов прихода синхронизирующих сигналов от одного из процессоров, в данном случае К СНА 3, и выработанного общего синхронизирующего сигнала К. СИЛ Н установку или первого триггера, или второго триггера, третий 45 и четвертый 46 элементы И осуществляющие формирование сигнала сброса одного из установленных триггеров 47 или 48, формирующих соотвегственно временной интервал, характеризующий степень или опережения управляющих сигиалов (К СИЛ 3 Н), в данном случае третьего процессора, от выработанного среднего значения управляющих сигналов (К СИЛ Н), или его отставание от выработанного среднего значения управляющих сигналов и управляющие соответственно поступлением счетных импульсов или на вход «-1, или на вход «+Ь СТ2, элемент ИЛИ 49, элемент 50 задержки, заглубляющий работу узла слежения (выполняет демпфирующую роль) и предотвращающий автоколебательные процессы, пятый элемент И 51, щестой элемент И 52, демультнплексор 53, выполненный, например, на элементах И, ИЛИ и осуществляющий подключение счетных импульсов или на вход «-1 или на вход « + 1 счетчика СТ2 54.

Временные диаграммы блока 5 (фиг. 9) обозначены позициями 43-54.

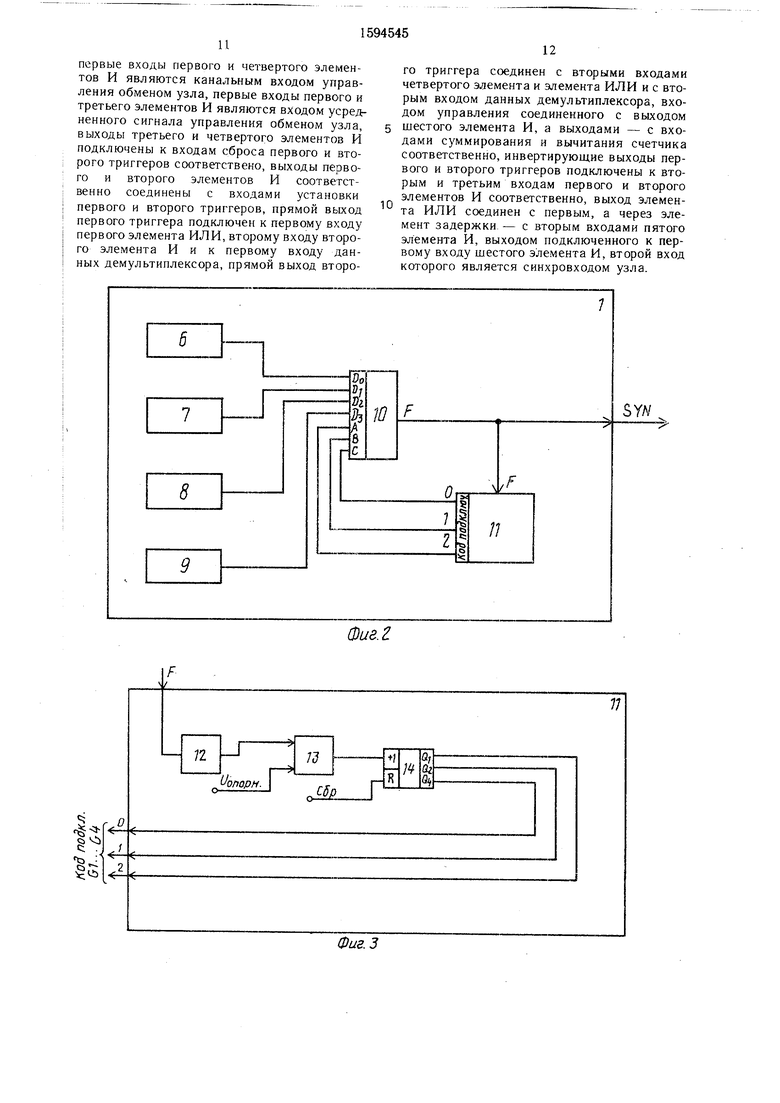

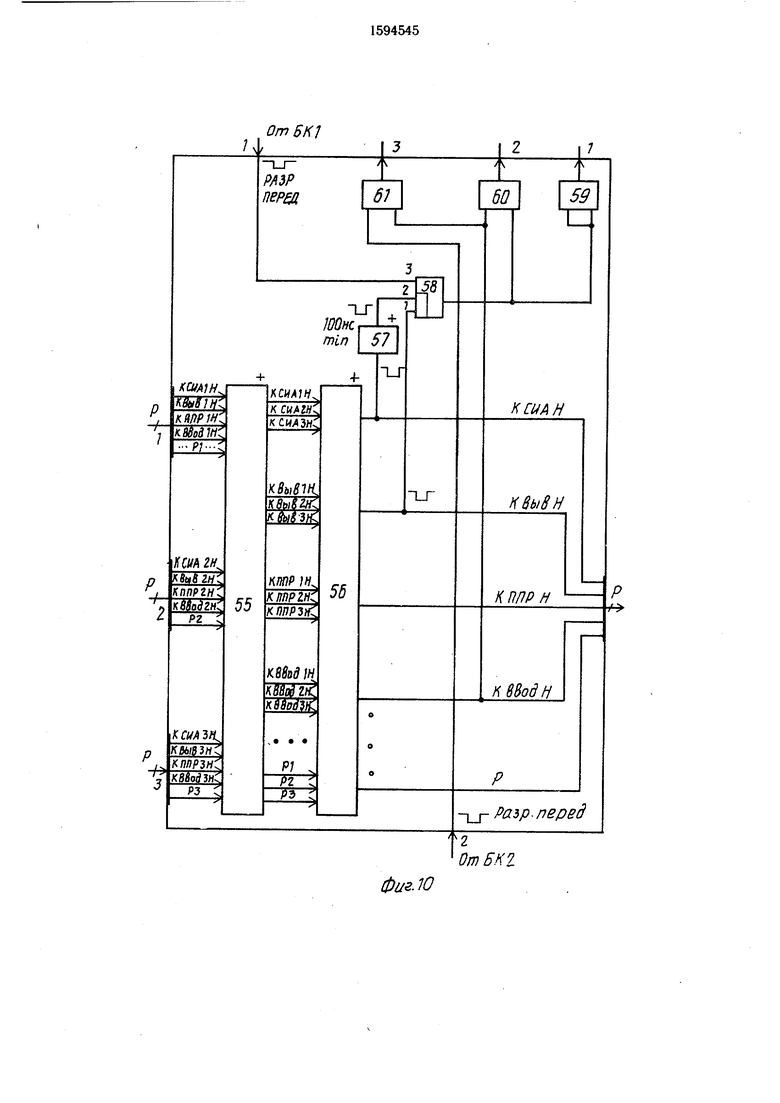

Первый блок 28 синхронизации (фиг. 10) содержит монтажнук) плату 55 развязки сигналов МРС, группу мажоритарных элементов М 56, формирователь 57 сигналов, первый элемент Й-НЕ 58, первый 59 и второй 60 элементы ИЛИ-НЕ, второй элемент И-НЕ 61.

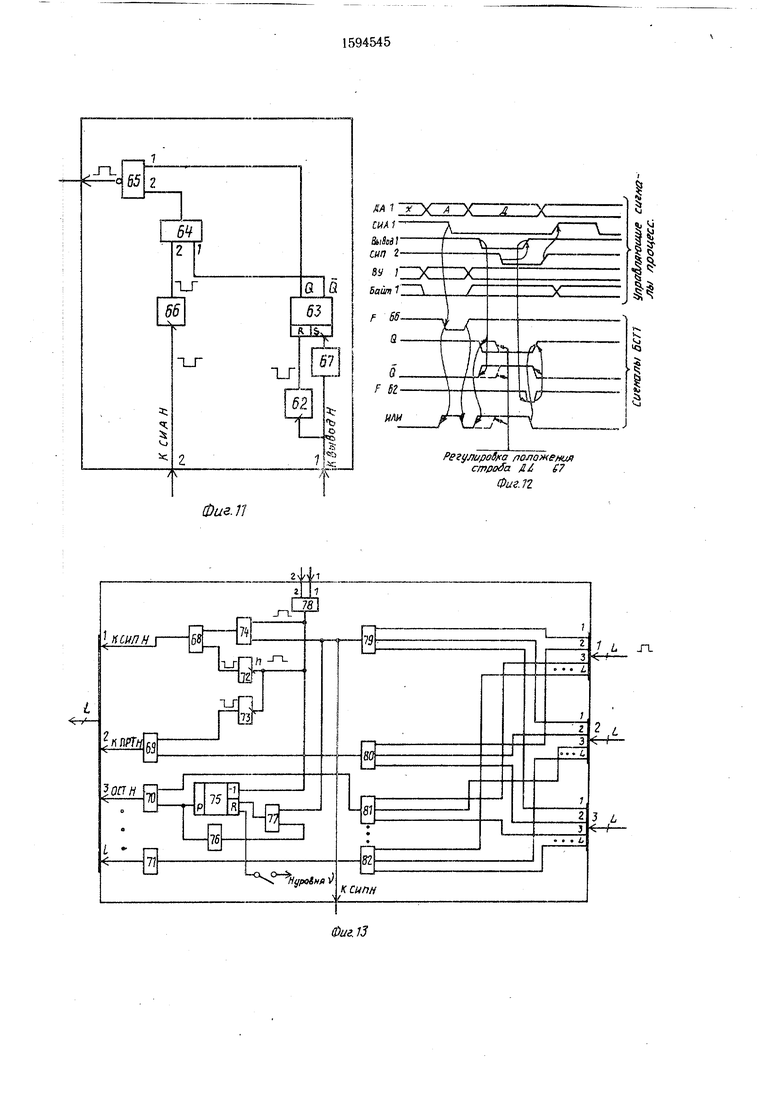

Первый блок 30 стробирования (фип. 11) содержит формирователь 62, формирующий сигнал сброса по заднему фронту сигнала.

трнггер 63, формирующий сигнал стробирования при передаче информации; элемент И 64, формирующий сигнал стробирования по сигналу К СИА Н при отсутствии сигнала

К ВЫВОД Н, элемент ИЛИ 65, осуществляющий сборку сигналов стробирования, формирователь 66, формирующий сигнал стробирования по переднему фронту сигнала, элемент 67 задержки, регулирующий поло- жение сброса.

Второй блок 29 синхронизации (фиг. 13) содержит первый элемент ИЛИ 68, осуществляющий сборку синхроимпульсов от внешних устройств и местного формирования,

г второй элемент ИЛИ 69, осуществляющий сборку сигналов прерывания от внешних устройств и местного формирования, третий элемент ИЛИ 70, осуществляющий сборку сигналов останова от внешних устройств и местного формироваиия, четвертый элемент

0 ИЛИ 71, передающий сигнал от внешних устройств, первый формирователь 72, формирующий местный сигнал синхронизации К СИП Н, второй формирователь 73, формирующий местный сигнал прерывания, на пример К ПРТ Н, элемент И 74, передаю- щий сигнал синхронизации от внешних устройств К СИП Н при отсутствии сигнала «Сбой на другом входе элемента, двоичный счетчик 75, осуществляющий подсчет числа сбоев и при его переполнении -

0 формирование сигнала останова (ОСТИ), элемент 76 задержки, осуществляющий формирование местного сигнала ОСТИ, второй элемент ИЛИ 77, осуществляющий сборку сигналов для сброса счетчика 75, элемент ИЛИ-НЕ 78, инвертирующий сигнал

5 «Сбой мажоритарные элементы с первого 79 по четвертый 82, осуществляющие мажорити- рование управляющих сигналов от внешних устройств.

Первый блок контроля (фиг. 15) блока 3 состоит из группы дешифраторов 813 и 84, на

входы которых заведены одноименные информационные разряды, элементов ИЛИ 85-87 производящих сборку соответствующих управляющих сигналов в три группы, мажоритарного элемента 88, осуществляющего

с формирование управляющего сигнала при искажении информации в двух и более процессорах, элемента И 89, осуществляющего выдачу управляющего сигнала при наличии разрешающего сигнала по входу Е. Второй (фиг. 16) блок контроля блока 3

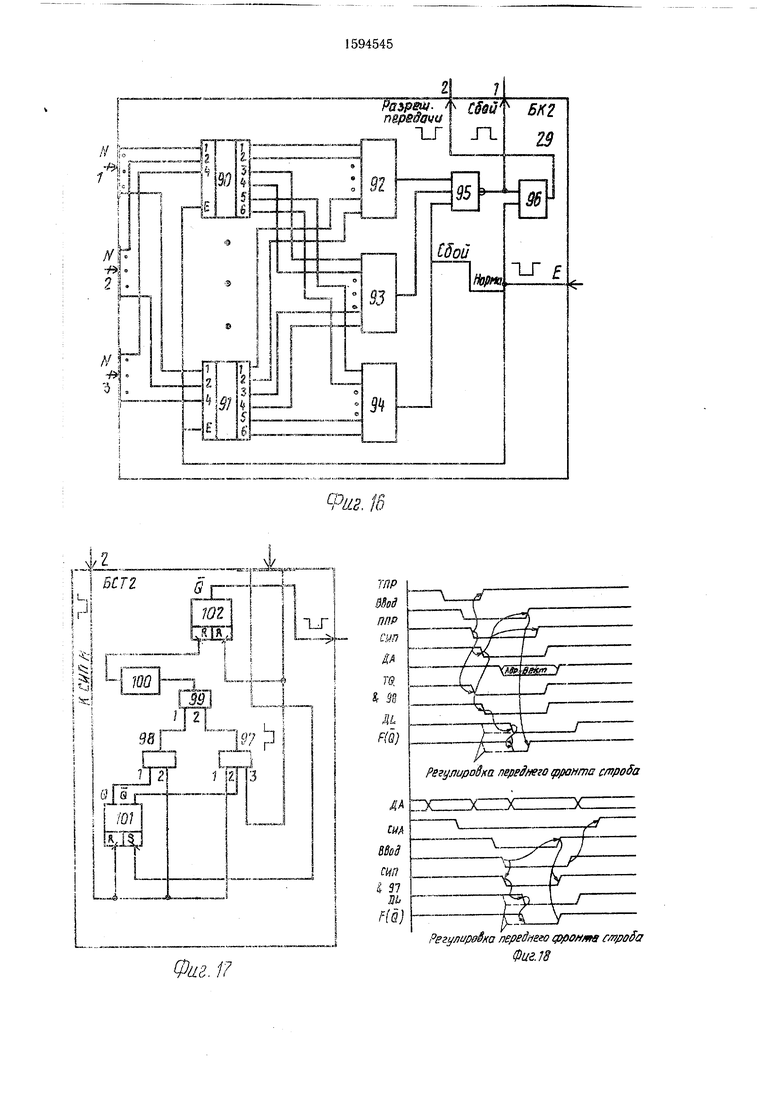

0 аналогичен первому блоку контроля и содержит группу дешифраторов 90-91, элементы ИЛИ 92-94, группу 95 мажоритарных элементов, элемент И 96.

Второй блок стробирования (фиг. 17) содержит первый элемент И 97, осущест5 вляющий передачу сигнала К ВВОД Н для формирования строба при наличии сигнала К СИП Н и отсутствии сигнала К ППР Н, второй элемент И 98, формирующий сигнал

строба при отсутствии сигнала К ППР Н, здемен г ИЛИ 99, осуществляющий сборку слгналов для формирования строба, элемент 00 задержки, осуществляющий регулировку вролтенного положения строба, триггер Т 101, ос/и-.йствляющкй выбор одного из двух сиг- налоЕ: р зависимости от наличия или от- с;,ГС1 ия сигнала PC ППР Н, формирователь 02, ф оррлируюидий строб по переднему фронту сигнала элемента 100 задержки и осу- П,сст1:-ляющий окончание формирования строба по заднему фронту сигнала К ВВОД Н. ):0зицией 103 обозначен ключ (фиг. 9).

Устройство работает следующим образом.

В исходном состоянии все элементы, требующие установки в исходное состояние (триггеры, счетчики, регистры), находятся в остоянии хранения, в зависимости от необходимости, или в со :тоянии О, или I, т. е. и,г11 сб1:), или установлены. В б.поке 5 енератор 42 генерирует импульсы наполне- ии;;, а с помощью регистра 4 в узлы слеже- нип 38-40 за рассинхронизацией занесен одинаковый код, обеспечивающий одинако- зый код рассогласования (Код1 ...КодЗ), что обеспечивает одинаковую задержку синхроимпульсов .,.SYN3 по отношению к исходному SV . V, что обеспечивает выполнение одинаковых инструкций (команд) соотзетст- зекно тремя процессорами i5-17 с учетом и;;диои.дуальных задержек процессов 1, 2, 3.

В блоке 3 шинные формироввте ш ;8-20 находится в состояния «Вьод (напраилекие передачи сигналов берется по отноше -гно к вх(щзм - вьЕходам шинных формйрозате- лей), что обеспечивается подачей ка их пер- В1ле входы (выбор кристалла микросхе5л.ы .Н1ч) постоянного сигнала низкого уровня /,, а на вторые входы - сигнала высокого уоовня j3. Ma разрещаю цие входы обоих сллоков 26 и 27 контроля подается запре- 1ь,ающий потенциал с соответствующих блоков 30 и 3.

На управляющие входы шинных форми- ро; ателей 21-23 с узла .28 синхрояк.зации подаются запрещающие с -;гна/;ы В., удержк- в;;.ощие их в состоянии « Закрыто.

Все генераторы 6-Э Е блоке 1 генераторов включены и генерируют синхроимпульсы. С ьэтчик 4 блока II контроля синхросиг- к.илоБ находится в состоянии 0. Соответствующий код с выхода счетчика 14 обее- нечивает передачу синхроимпульсов от гене- рптора G1 6 на выход мультиплексора 0 и да;;ее на выход блока 1 - SYM.

С блока 1 генераторов, сикхро-- ;:;.1иу.льс.ы поступают на блок управления .5Г:дер)кками и далее на установочные входы / триггеров 35-37, на сикхровходы С ;со10рых с преобразователей 32-34 частота - код подаются соответствующие синхрс- иглпульсы .ri...f3 с одинаковой частотой, что обуславливает в начальный период синхронность тактовых процессорных синхроимпуль- сои SYNI...SYN3.

Процессоры 15-17, например, активизированы и начинают выполнять одинаковые инструкции (команды). Каждая команда, как правило, начинается с операции по

выборке команды, т. е. обращением посредством общей щины к запоминающему устройству. Процессоры помещают адрес команды на свои общие шины и извлекают из памяти код команды, используя для этого цикл «Ввод. В зависимости от типа выполняемой команды процессоры могут иметь до четырех обращений по своим ОШ1...0ШЗ. В силу этого при выполнении каждой команды происходит соответственно до четырех циклов синхронизации работы процесссфов

15-17. Адреса команд по линиям N подаются на узлы 24 и 26. Сопровождающие адрес управляющие сигналы по линиям Р поступают на узел 28, где по принципу «2 из 3 общий управляющий сигнал К СИА Н указывает, что адрес помещен как минимум

на двух из трех ОШ. При наличии сигнала К СИА Н с группы Р выходов узла 28 узел 30 формирует соответствующий стро- бирующий сигнал, который разрещает работу узла 26.

Комбинационные схемы узла 26 анализируют одноименные информационные разряды, поступающие на них с общих щин. При равенстве не менее двух информационных сигналов адреса на выходе узла 26

формируется рйзрео ающий сигнал Н, который П()сту11ает из первый вход узла БС2 28 к на вход узла БС2 29.

В узле 28 сигнал с первого входа поступает на третий вход комбинированного элемента И-НЕ 58, где в это врегля присутствует один из Сигналов или с формирователя 57, иля с линнк К ВЫВ Н. С выхода комбинированного элемента И-НЕ 58 сиг- кал Я поступает па входы элементов ИЛИ- НЕ 59 и 60 и переводит соответственно

шинные формирователи 21-23 из «Закрытого СОСТОЯНИЙ в состояние «Вывод (от входа к зходам - выходам) и, соответственно, адрес, по которому будет выбрана команда, поступает в память.

Код команды по циклу «Ввод

считывается из памяти и поступает в процессоры следующим образом. По сигиалу К ВВОД Н формирователи 21-23 переводятся в режим «Ввод (от входов-выходов к выходам). Вводимая информация с формирователей 21-23 поступает на узлы 25

и 27. При равенстве не меиее двух наборов данных (кодов команд) и наличии строби- рующего сигнала с узла 3 на входе узла 27 последний формирует разрещающий сигнал, который поступает на второй вход узла 28, разрешает прохождение сигнала низкого

уровня К ВВОД Н на третий выход узла 38 с элемента И-НЕ 61 и переводит формирователи 18-20 в режим вывода (от входов к входам-выходам).

Вывод и ввод информации в процессоры всегда сопровождаются синхроимпульсом активного усройства К СИЛ Н. Каждый из этих сигналов с соответствующих процессоров (К СИЛ 1Н, К СИЛ 2Н, К СИЛ ЗН) ОШ1, ОШ2, ОШЗ, кроме блока 3, поступают соответственно на блок 5, куда поступает общий сигнал (занимающий среднее временное положение в начальный момент) К СИЛ Н. В случае, когда, например, в начальный период сигнал К СИЛ ЗН опережает общий сигнал К СИЛ Н, то по переднему фронту сигнала К СИЛ ЗН устанавливается триггер Т47, что приводит к установлению на входах VI, V2 демультиплексора 53 кода, обеспечивающего подачу счетных импульсов с генератора 42 на вход-«1 счетчика 54. При поступлении общего импульса К СИЛ Н триггер Т47 сбрасывается. На входах VI, V2 демультиплексора 53 формируется код, закрывающий демультиплексор 53 для счетных импульсов генератора 42.

Таким образом, на выходах счетчика присутствует код рассогласования, характеризующий в цифровой форме величину опережения сигналом К СЙА ЗН сигнал К СИЛ Н. Коды рассогласования поступают на блок 4 управления задержки, где с помощью преоб- разователсй код - частота вырабатываются синхросигналы, обеспечивающие или задержку исходного сигнала SYN., или оставляющие его временное положение без изменений (фиг. 7.) обеспечивается индивидуальная задержка процессорных синхросигналов, что обеспечивает одновременность появления информационных и управляющих сигналов на выходах процессоров.

В известном устройстве в случае взаимного рассогласования выходных сигналов трех процессоров, превыщающих некоторую величину, когда один из процессоров отстает или опережает остальные два, и при случайном искажении информации в одном из оставшихся двух процессоров принцип голосования «2 из «3 нарушается,, при этом по сформированным сигналагй ошибки затрачивается время на восстановление синхро низации. На весь период восстановления синхронизации принцип голосования «2 из «3 нарушается. В случае более значительной рассинхронизации, когда один из процессоров опережает или отстает от остальных на несколько тактов, принцип голосования «2 из «3 тем-более не выполняется.

Предлагаемое устройство поддерживает точную синхронизацию сигналов на выходных контактах, например, микропроцессора, и в случае искажения инфорации в одном из них принцип голосования «2 из «3 сохраняется. Кроме того, не затрачивается время на восстановление синхронизации.

Формула изобретения

процессоров, информационные входы и выходы которого через блок сопряжения процессоров подсоединены к информационным входам-выходам устройства, отличающееся тем, что с целью повыщения надежности устройства, в него введены блок управления задержками и блок слежения за рассинхро- низацией процессоров, вход усредненного сигнала управления обменом которого соединен с соответствующим выходом блока сопряжения процессоров, входы канальных сигналов управления обменом подключены к соответствующим линиям входов-выходов блока процессоров, а выходы кодов управления задержкой частоты подключены к соот- 5 ветствующим входам управления с задержкой частоты блока управления задержками. синхровходом подключенного к выходу блока генераторов, а синхровыходами - к соответствующим синхровходам блока процессоров.

0 2. Устройство по п. 1, огли:1ак мгеся тсь-., что блок управления задержками содержит с первого по третий преобразователи код - чае- тота и с первого по третий триггеры, выходы которых являются синхровыходми блока 5 управления задержками, входы преобразователей код - частота являются cooTserj ст,вующими входами управления задержкой частоты блока управления задержками, а выходы соединены с синхровходами триггеров с первого по третий, входы данных 30 которых являются синхровходом блока управления задержками.

35 узлы слежения за рассинхронизациеи, регистр и генератор импульсов, выходом подключенный к синхровходам узлов слежения за рассинхронизациеи с первого по третий, выходы регистра подключены к соответствующим входам данных узлов слежения ,-;;5

рассинхронизациеи, кодовые выходы которых являются выходами кодов управлени; задержкой частоты блока слежения за рас- скнхронизацией процессоров, входы усред ненных сигналов управления обменом являлс; ются одноименным входом блока слежения за рассинхронизациеи процессоров, входы канальных сигналов управления обменом которого соединены с одноименными входами узлов слежения за рассинхронизациеи соответственно.

50

4 Устройство по п. 3, отличающееся тем. что узел слежения за рассинхронизациеи содер жит с первого по шестой элементы И, первый и второй триггеры, элемент ИЛИ, элемент задержки, демультиплексор и счет- 55 чик, входы данных которого являются входами данных узла,вход установки через ключ соединен с шиной нулевого потенциала, вы- ходы являются кодовыми выходами узла.

первые входы первого и четвертого элементов И являются канальным входом управления обменом узла, первые входы первого и третьего элементов И являются входом усредненного сигнала управления обменом узла, выходы третьего и четвертого элементов И подключены к входам сброса первого и второго триггеров соответствено, выходы первого и второго элементов И соответственно соединены с входами установки первого и второго триггеров, прямой выход первого триггера подключен к первому входу первого элемента ИЛИ, второму входу второго элемента И и к первому входу данных демультиплексора, прямой выход второФиг. г

го триггера соединен с вторыми входами четвертого элемента и элемента ИЛИ и с вторым входом данных демультиплексора, входом управления соединенного с выходом шестого элемента И, а выходами - с входами суммирования и вычитания счетчика соответственно, инвертирующие выходы первого и второго триггеров подключены к вторым и третьим входам первого и второго элементов И соответственно, выход элемента ИЛИ соединен с первым, а через элемент задержки - с вторым входами пятого элемента И, выходом подключенного к первому входу шестого элемента И, второй вход которого является синхровходом узла.

SY/V

FJ 32

F2

33

Фиг. 6

лллшшж яшшллжллллшщ

F3

nSinnrLTLnn

35

SYN; Q

SYf/г Q

SY/V3

F3 3

.

fU

:

К

От SKI

P/I3P

/fep

LT /ШйС min

4КСЯАТН.

)(8ы81И,

iKBaSZff:

8ug3H

55

КППР )Н.

К.ППР1Н:

кпппК

56

Шпд W

BSodZ:

KSSodl

PI

рг

ръ

i

t:-i

Т-Г

KCUAH

TJ

Н8ы8Н

КППР н

SBodH

Р

Pazp. перед

От БКг

фцгЛО

Фив. л

Peiyj}ijpoSf(a /7оло е иа строка Д 7

Фиг. 72

1 L Л.

5К1

А/

It

yV 8

CSou

В5

86

Hapfi

J-L f CTP06

§7

ФиеЛ5

16

г.1

2

CSeu

BK2 29

Регулироёка переднего cfpoSa

ад

Ш8

W;7

I 37 Sl

He

Регулирв§на переднего (pftOM/rts с/про5а

ФигЛЗ

Н

Н

Н

Фиг. 19

Фиг.го

Lifp(lB...20)

Фиг. 27

Искажение (jHcpop- ации при ВЫдОД д данном лроцессогрё

Временной yt/ac/nofi при Зд/ВО Е инсрормоции, где omcg/ncmdt/efTj

(Opi /7Jtf/}o8aHi/e §сисгле/ е

Фиг. г.

| Патент США № 4358823, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| ЭЛЕКТРОЛИТ ЛУЖЕНИЯ ЖЕСТИ | 1995 |

|

RU2093614C1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1990-09-23—Публикация

1987-12-15—Подача