(54) УСТРС СТВО СОТРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентами | 1985 |

|

SU1283779A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для обмена информацией | 1986 |

|

SU1336017A1 |

| Устройство для обмена информацией между ЭВМ | 1990 |

|

SU1784990A1 |

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1312591A1 |

| Устройство управления вводом-выводом | 1990 |

|

SU1839254A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1981 |

|

SU1003066A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления технологическими прсщессами, измерительво-информац oifflbDC системах и комплексах автоматиз1фованной обработки экспериментальных данных.

Известно устройство для согфяжения, содержащее дешифратор адреса, дешифратор группового обращения, блок эле ментов И, два блока элементов ИЛИ, дешифратор комавды, блок элемеигов И, блок групповой синхронизации, блок индикации неисправности, блок анализа состояния, блок элементов ИЛИ два бло-ка элементов И 1}

Недостатком указанного устройства является fro сложность.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для сопряжения с цифровой Вычислительной машиной, которое содержит блок щ)иемоп едаюших усилителей, регистр данных.

коммутатсф, регистр состояния, блок тферывания, первый и второй дешифратqpы адреса, регистр внутренней адресации Г2.

Недостаток известного устройства состоит в том, что с его помощью ЦВМ может вести обмен только с одним внешним устройством, этим обуславливается низкий коэффициент использования обфудования, которое Щ)остаивает, тогда как ЦВМ имеет возможность вести обмен с большим количеством внешних устройств

Цель изобретения - повышение коэффициента использования оборудования.

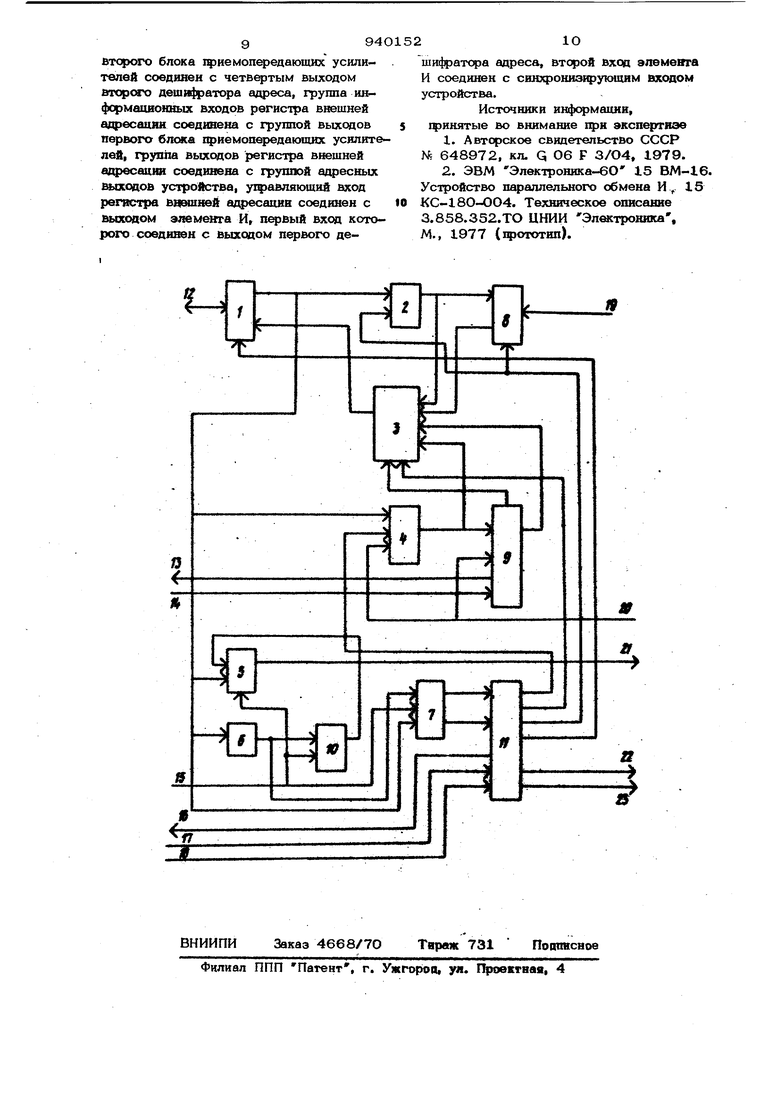

Поставленная цель достигается тем, что в устройство сопряжения, содержащее первый блок щжемопередающих усилителей, группе входов - выходов которого соединена с первой группой информационных входов - выходов устройства, груцпа выходов первого блока приемопере- дающих усилителей соединена с группаI ми входов регистра данных, первого дешифратора адреса, регистра внутренней адресации и первой группой входов регистра состояния, группа входов первого блока приемопередающих усилителей соединена с группой выходов коммутатора, группа выходов регистра данных соединена с первой группой информациOHHbLx входов коммутатора, группа выхо дов регистра состояния соединена со второй группой информационных входов «о мутатораи группой маскирующих входов блока прерывания, вторая группа входов регистра состояния соединена с группой информационных входов блока прерыванш и группой .чапросных входов устройства, группа выходов блока гферывания соединена с третьей группой информационных входов коммутатора, первый выход блок щэерывания соединен с выходом сигнала прерывания устройства, второй выход блока прерывания соединен с первым управляющим входом коммутатора, вход блока гферывания соединен с разрешающим входом устройства, выход первого деши4ратора адреса соедшшн с управляющим Входом регистра внутре;шей адресации, тактовый вход которого соединен с сшсфонизирующим входом устройства, щэизнаковь.й выход регистра внутренней адресации соединен с управляющим входом втсрого дешифратора адреса, группа информационныг выходов регистра внутренней адресации соединена с группой информационных входов второго дешифратора адреса, с первого по седьмой Выходы второго дешифратора адреса соеД1шеиы соответствешю с выходом готовности устройства, с у15 авляющим входом регистра состояния, с вторым уп равляющим входом коммутатора, с упрагшяюшим входом регистра Данных, с управляющим входом первого блока приемопередающих усилителей, выходами )ежимов вывода и ввода устройства, а первый и второй информационные входы BTqporo дешифратора адреса соединены соГгветственно с входами режимов вывода и ввода устройства, введены регистр внешней адресации, второй блок щэиемопередающих усилителей и элемент И, причем группа входов второго блока приемопередающих усилителей соединена с группой выходов регистра , четвертая гоуппа информационных входов коммутатора соединена с группой выходов второго блока приемопередающих усилителей, группа входов выходов которого соединена с второй группой информационных входов - выходов ycTpoJ.CTBa, управляющий вход второго блока приемопередающих усилителей соединен с четвертым выходом второго дешифратора адреса, группа информационных входов регистра внешней адресации соединена с группой выходов первого блока приемоп едающих усилителей, группа выходов регистра внешней адресации соединена с группой .адресных выходов устройства, ухфавляющий вход регистра внешней адресации соединен с выходом элемента И, первый вход которого соединен с выходом первого деши4ратсра адреса, второй вход элемента И соединен с синхронизирующим входом устройства. На чертеже представлена структурная схема устройства. Устройство сопряжения содержит первый блок 1 приемопередающих усилителей, регистр 2 данных, коммутатор 3, регистр 4 состояния, регистр 5 внешней адресации, первый дешифратор 6 адреса, регистр 7 внутренней адресации, второй блок 8 гфиемопередающих усилителей, блок 9 1ферывания, элемекг И Ю, второй дешифратор 11 адреса, первую группу 12 входов - выходов устройства, первый выход 13 устройства, первый и второй входы 14 и 15 устройства, второй выход 16 устройства, третий и четвертый входы 17 и 18 устройства, вторую группу 19 входов - выходов устройства, группу входов 2О устройства, группу выходов 21 устройства, третий и четвертый выходы 22 и 23 устройства. Устройство работает следующим образом. Обмен информацией между ЦВМ и внешними устройствами осуществляется в программном режиме и по требованиям гферывания программы от внешних устройств и включает в себя адресный цикл и цикл передачи данных. Адресное слово, предаваемое двоичным кодом через первую группу 12iBxoдов - выходов устройства от ЦВМ, принимается первым блоком 1 приемопередающих усилителей и передается на внутреннюю шину адреса-данных устройства. Часть разрядов адресного слова подается на группу входов дещифратора 6 адреса, чем осуществляется адресация к данному устройству. Остальные разряды адресного слова распределяются между регистрами внутренней 7 и внешней 5 ащзесации и подаются на их группы , входов. , отведенные регистру 7 внутренней адресации, гредназначены для регистров устройства сопряжения. Разряды, отведенные регистру 5 внешней адресации, гфедназначены для выбора одного из внешних устройств, подключенных к устройству сопряжения. Если ЦВМ обращается к данному устройству сопряжения, то его дешифратор 6 адреса В1фабатывает сигнал выбора данного устройства, который с выхода дешифратсфа 6 подается на первые входы элемента И 1О и регистра 7 внутренней адресаций. При по$шлении на втором входе 15 устройства сигнала сиюфонизации от ЦВМ, подаваемого в- адресном цикле обмена информацией, осуществляется запис в регистр 7 внутренней адресации соответствующих разрядов адресного слова и сигнала выбора устройства, подаваемого с выхода дешш} атора 6 адреса, снятие блокировки записи в регистр 5 внеш ней адресации, которое вьшолняется подачей сигнала синхронизации на вход регистра 5, появление сигнала на выходе элемента И 10, которым осущест вляется запись соответствукяцих адресного слова в регистр 5 внешней ащ}есации, и появление кода внешнего устройства, с которым будет осуществляться обмен информацией, на группе вы ходов 21 устройства. Бели в цикле передачи данных должен выполняться вывод данных во внешнее устройство, то через первую группу 12 входов - выходов устройства блоком 1 приемопередающих усилителей щ инимается двоичный код данных и подается на группу входов регистра 2 данных. Запись информации в регистр 2 осуществляется при появлении на его входе сигнала с дешифратора 11, который вырабатываетс 1ФИ условии наличия на группе входов и первом входе дещифратора 11 кода регистра данных и сигнала выбора устройства, записанных в регистр 7, и появлении на втором входе дешифратора 11 сигнала вывода, поступающего от ЦВМ через третий вход 17 устройства. При этом сигналом, поступающим на его вход открывается второй блок 8 1Ц)иемопередающих усилителей и на второй группе 19 входов - выходов устройства появляется ко данных, сопровождаемый сигналом вывода Вьфабатываемого дешифратором 11 и по даваемого на третий выход 22 устройст ва. Данные могут быть цриняты только тем внешним устройством, код записан в адресном цикле в регистр 5. Если в цикле передачи данных должен юсушёствляться ввод данных из внетинего |Устройства в ЦВМ, то прк подаче на четвертый вход 18 устройства сигнала ввода от ЦВМ и при наличии на группе входов дешифратора 11 соответствующего хода им вырабатывается сигнал ввода, предаваемый через четвертый выход 23 ргстройства к внешнему устройству. После этого данные от внешнего устройства через вторую группу 19 входов - выходов устройства и второй блок 8 приемопередающих усилителей поступают на группу входов коммутатора 3, а затем через первый блок 1 Щ)иемоп едающих усилителей, котсрый получает улравпяющий сигнал от дешифратора 11, и первую группу 12 входов - выходов устройства предаются в ЦВМ. Данные могут быть преданы только тем внешним устройством, код которого записан в адресном цикле в регистр 5. Вырабатывая внутренние управляющие сигналы, дешифратсф 11 вьщает сигнал сншфонизации, который сигнализ1фует ЦВМ о том, что данные устройством приняты (оря выводе информаш{и) или подг готовлены для передачи (тфи вводе информации), и 1юредает через второй выход 16 устройства. Получив этот сигнал, ДВМ снимает сигнал вывода (или ввода), а затем и сигнал синхронизации, вьфабоганный в вцресаом цикле, по заднему фронту которсяо обнуляется регистр 5 внешней адресации, на чем завершается if}onecc обмена данными. Запись информации (ра цений на прерывания ф ограммы ЦВЛ1) в регистр 4 состояния осуществляется по аналогии с записью информации в регистр 2 данных. Подаваемый на группу входов регистра 4 код записывается щзи появлении на его входе сигнала с дешифратора 11, который вырабатывается прк условии запнси в регистр 7 кода регистра состоягаш. С помощью коммутатора 3 по аналогии с процессом ввода данных от внешнего устройства в ЦВМ может быть введена информация из регистра 2 данных, регистра 4 и адрес вектс а 14 ерываннд с блока 9 хф ывания. Выбор оюного нз четьфех нвформашюнных входов коммутатора 3 осуществляется подачей уар&ъпяютях. сигналов на первый и второй входы коммутатора 3. Обмен данными по требованиям прерывания 1фограммы от внешних устройств имеет место арк появлении сигнала на любом из входов группы входов 2О устройства и прк наличии сигнала разреше1ШЯ на соответствующее прерывание, который передается в блок 9 прерывания через группу выходов из регистра 4 состояния, куда это разрешение 1федварительно должно быть занесено по программе ЦВМ. При этом блок 9 прерывания фсчзм1фует сигнал требования гферывания, который поступает в ЦВМ через первый выход 13 устройства. Ответом на этот сигнал является сигнал предоставления 1Ц)ерываиия, поступающий на блок 9 прерывания через первый вход 1 устройства. В результате с группы выхо дов блока 9 прерывания передается через коммутатор 3, первый блок 1 передающих усилителей и первую группу 12 входов-выходов устройства код адреса ве тсра прерывания, используемый ЦВМ для перехода к соответствующей фограмме об служивания требования г эерывания i oграммы от внешнего устройства. Вторая группа 19 входов - выходов устройства, образующих шину данных, и выходы 22 и 23 для внешних устройств являются линиями коллективного пользования. Группа входов 2О устройства образуется линиями индивидуального пользования, распределенными между внешними устройствами. Каждая из линий, входящи в ipyimy выходов 21 устройства, может быть использована внешними устройствами как коллективно, так и индивидуально. Таким образом, изобретение позволяе повысить коэффициент использования оборудования без увеличения длительности цикла обмера данными. Число подключаемь1Х внешних устройств определяется количеством адресных линий m , выводимых к внешним устройствам через групп Выходов 21 устройства при индивидуальном расщзеделении этих линий между ними, и может быть равно 2 при коллективном использовании адресных линий Формула изобретения Устройство сопряжения, содержащее первьй блок приемопередающих усилителей, группа входов - выходов которого соединена с первой группой информашюнin ix входов - ькодов устройства, группа выходов первого блока приемопередающих усилителей соед1шена с группами входов регистра да1шых, первого дешифратора адреса, регистра внутренней адре сации и первой группой входов регистра состояния, группа входов первого блока приемопередающих усилителей соединена с группой выходов коммутатора, группа выходов регистра данных соединена с первой группой информационных входов коммутатора, группа выходов регистра состояния соединена с второй группой информационных входов коммутатора и группой маскирующих входов блока прерывания, вторая группа входов регистра состояния соединена с группой инфс мационных входов блока прерывания и группой запросных входов устройства, группа выходов блока прерывания соединена с третьей группой инф мационных входов коммутатс а, первый выход блока прерывания соединен с выходом сигнала прерывания устройства, второй выход блока прерывания соединен с первым управляющим входом коммутатора, вход блока щ ерывания соединен с разрещающим входом устройства, выход первого дешифратора адреса соединен с у15)авляющим входом регистра внутренней адресации, тактовый вход коTcqjoro соединен с синхронизирующим входом устройства, щэизнаковый выход регистра внутренней адресации соед1шен с управляющим входом второго дешифратора адреса, группа инфс мационных выходов регистра внутренней адресации соединена с группой информационных входов BTqjoro дешифратора адреса, с первого по седьмой выходы второго дешифратора а;феса соединены соответственно с выходом готовности устройства, с управляющим входом регистра состояния, с вторым уфавляющим входом коммутатора, с угфавляющим входом регистра данных, с управляющим входом первого блока приемопередающих усилителей, выходами режимов, вывода и ввода устройства, а первый и второй инфсрмационные входы второго дешифратора адреса соединены соответственно с входами режимов вывода и ввода устройства, отличающееся тем, что, с целью повьпиения коэффициента использования оборудования, оно содержит регистр внешней адресации, втсфой блок приемопередающих усилителей и элемент И, хфичем группа входов блока приемопередаюц1их усилителей соединена с группой выходов регистра данных, четвертая группа информационных входов коммутатора соединена с грутшой выходов второго блока 15)иемопере5цающих усилителей, группа входов - выходов которого соединена с второй группой информационных входов выходов устройства, управляющий вход

второго блока щжемоп едающих усилителей соединен с выходом второго дешифратора ащэеса, группа ш&формацвонных входов регистра внешней адресации соединена с группой выходов первого блока приемопередающих усилителей| группа выходов регистра внешней а1фесацин соединена с группой ащэесных выхспоь устройства, утфавляюший вход репютра внешней а/фесацин соединен с зшходом эпе мента И, вход которого соединен с выходом первого дешифратора адреса, второй вход элемента И соединен с синхронизщ)ую1Ш1М входом устройства.

Источники информации, 1рин51тые во внимание при экспертизе

2,ЭВМ Электроника-6О 15 ВМ-16. Устройство п аллельного обмена И, 15 КС-18О--ОО4. Техническое описание 3.858.352.ТО ЦНИИ Электрокика,

М., 1977 (i9)OTOTHn).

Авторы

Даты

1982-06-30—Публикация

1980-12-29—Подача