(54) ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1976 |

|

SU683026A2 |

| Делитель частоты | 1975 |

|

SU595863A1 |

| Устройство для воспроизведения видеосигнала | 1987 |

|

SU1555918A1 |

| Устройство для моделирования вероятностных сетевых графиков | 1982 |

|

SU1022177A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Устройство для контроля линейных динамических объектов | 1990 |

|

SU1795422A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для измерения частоты и ритмичности сердечных сокращений | 1984 |

|

SU1219048A1 |

1

Изобр&гвкке относится ie импульсной технике.

Известен делитель частоты, содержащий элемент ЗАПРЕТ, блок элементов И, . д&а регистра, сумматор, элементы ИЛИ, элемент задержки, триггер l

Однако данный делитель не обладает достаточным быстродействием.

Наиболее близким по технической сущности к предлагвемому является де ,д литель, который содержит элемент запрета, вентили, регистр числителя, регистр знаменателя, элемент ИЛИ, сумматор, триггер, элемент задержки, регистр разности, дополнительный триггер, допоп- 5 шпельный элемент запрета. Выходы ре- гистров числителя, шменателя и разности подключены к входам вентилей. Выходы вентилей связаны со входами элемента ИЛИ, выход которого связан сю входом сумматора. Один вход сумматора, подключен ко вкоау регистра разности, второй выход связан- со входами триггера и дополнительного триггера. Другой

вход триггера связан с выходом элемента задержки. Прямой выход триггера и инверсный выход дополнительного триггера связШ1Ы со входами элемента запрета. Инверсный выход триггера и прямой вьь-. ход яснтолнительного триггера подключены к входам дополнительнозго элемента запрета. Остальные оходы элемента запрета и дополнительного элемента запрета связаны со входом элемента задержки, а их выходы подключены ко входам дополнительного элемента ИЛИ 1.2 .

Однако известный делитель не обладает достаточной точностью.

Цель изобретения - увеличение точности.

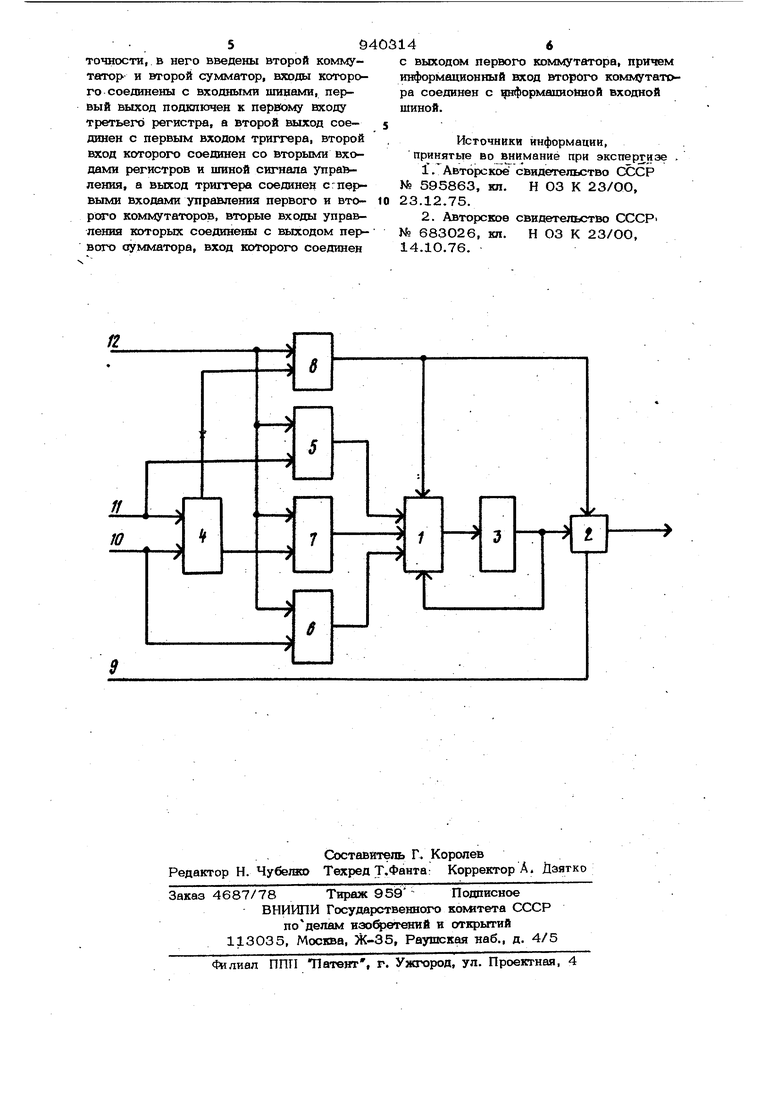

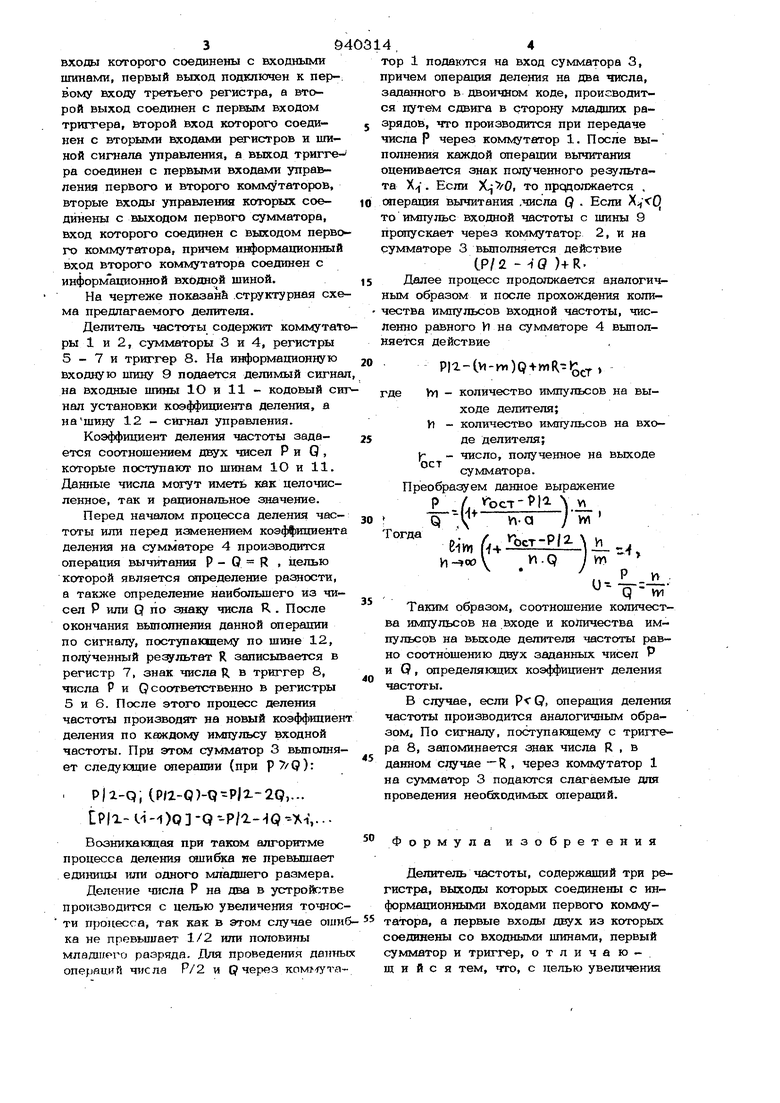

Поставленная цель достигается тем, что в делитель частоты, содержащий три регистра, выходы которых соединены с информационными входами первого коммутатора, а первые входы двух «з которых соединен со входыми шинами, первый сумматор и триггер, введены второй коммутатор и второй сумматор, входы которого соединены с входными шинами, первый выход подключен к первому входу третьего регистра, а второй выход соединен с периым входом триггера, второй вход которого соеди- нен с вторыми входами регистров и шиной сигнала управления, а выход трнгге ра соединен с первыми входами управления первого и второго коммутаторов, вторые входы управления которых соедйнены с выходом первого сумматора, вход которого соединен с выходом перво го коммутатора, причем информационный вход второго коммутатора соединен с информационной входной шиной. На чертеже показан структурная схе ма предлагаемого делителя. Делитель частоты содержит коммутат ры 1 и 2, сумматоры 3 и 4, регистры 5 - 7 и триггер 8. На информационную входную шину 9 подается делимый сигна на входные шины Ю и 11 - кодовый си нал установки коэффициента деления, а на шину 12 - сигнал управления. Коэффициент деления частоты задается соотношением двух чисел Р и Q , которые поступают по шинам 1О и 11. Данные числа могут иметь как целочисленное, так и рациональное значение. Перед началом процесса деления частоты или перед изменением коэффициент деления на сумматоре 4 производится операция вычитания Р - О R . целью которой является сшределение разности, а также определение наиболыыего из чисел Р или Q lio знаку числа R . После окончания вьшопнения данной операции по сигналу, поступающему по шине 12, полученный результат R записывается в регистр 7, знак числа R. в триггер 8, числа Р и Q соответственно в регистры 5 и 6. После этого процесс деления частоты производят на новый коэффициен деления по каждому импульсу входной частоты. При этом сумматор 3 вьтолня ет следующие сяперадии (при p7/Q): PU-Qi CP/1-Q)-Q-P|X-2Q,... tPlT- И -1)Q -q -P/a-HQ --.i,... Возникающая при таком алгоритме процесса деления саиибка не превышает единицы или одного младшего размера. Деление числа Р на два в устройстве производится с целью увеличения точности процесса, так как в этом случае ошиб ка не превьштает 1/2 или половины младшрго разряда. Для проведения дантшо операций числа Р/2 и Q через KOMifyraTop 1 подакугся на вход сумматора 3, причем операция деления на два числа, заданного в двоичном коде, происводится путем сдвига в сторону младших разрядоВ|, что производится при передаче числа Р через коммутатор 1. П осле выполнения каждой операции вычитания оценивается знак полученного результата . Если /0, то продолжается , операция вычитания .числа Q . Если то импульс входной частоты с шины 9 пргатускает через коммутатор 2, и на сумматоре 3 выполняется действие СР/2 - G )+R. Далее процесс продолжается аналогичным образом и после прохождения количества импульсов входной частоты, численно равного V) на сумматоре 4 выполняется действие P|a-Cvi-m)Q-HYiR-lg,.t где hi - количество импульсов на выходе делителя; И - количество импульсов на входе делителя; - число, полученное на выходе сумматора. Преобразуем данное выражение Л Пэст-1 1 2QИ-ч . п. JL-JL. Q VV1 Таким образом, соотношение количества импульсов на входе и количества импульсов на выходе делителя частоты равно соотношению двух заданных чисел Р и Q , определяющих коэффициент деления частоты. В случае, если , операция деления частоты производится аналогичным образом. По сигналу, поступающему с триггера 8, запоминается знак числа R , в данном случае - R , через коммутатор 1 на сумматор 3 подаются слагаемые для проведения необходш сых огхераций. Формула изобретения Делитель частоты, содержащий три регистра, выходы которых соединены с информационными входами первого KOMJviyтатора, а первые входы двух из которых соединены со входными шинами, первый сумматор и триггер, отличающийся тем, что, с целью увеличения

точности, в него введены второй коммутатор и второй сумматор, входы которого соединены с входными шинами, первый выход подключен к первому входу третьего регистра, а второй выход соединен с первым входом триггера, второй вход которого соединен со вторыми входами регистров и шиной сигнала управления, а выход триггера соединен с-первыми Входами управления первого и второго коммутаторов, вторые входы управления которых соединены с выходом первого оумматора, вход которого соединен

с выходом первого коммутатора, причем информационный вход второго коммутатора соединен с нформашюшюй входной шиной.

Источники информации, принятые во внимание при экспергиэе .

1 Г Авторское свидетельство СССР N° 595863, кл. Н ОЗ К 23/ОО, 23.12.75.

Авторы

Даты

1982-06-30—Публикация

1980-12-17—Подача