(54) УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения частоты следования импульсов | 1982 |

|

SU1040598A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU945964A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Цифровой умножитель частоты | 1979 |

|

SU788363A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU949789A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU898600A1 |

| Умножитель частоты | 1986 |

|

SU1332316A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель-нормализатор частотныхСигНАлОВ | 1979 |

|

SU847505A1 |

| Цифровой умножитель частоты | 1980 |

|

SU957206A1 |

1

Настоящее изобретение относится к импульсой технике.

Известен умножитель частоты следования мпульсов, содержащий формирователь импульсов, счетчики импульсов, блоки сравнения, запоминающий- регистр, блок управления и триггер 1.,

Недостатком умножителя частоты является снижение точности его работы при больших коэффициентах умножения.

Известен умножитель частоты следования импульсов, содержащий делитель опорной частоты импульсов, входной и,выходной формирователи импульсов, счетчик импульсов и счетчик импульсов опорной частоты, блок упрарлеиия, запоминающий регистр и блок, элементов И 2.

Недостатком данного умножителя также является пониженная точность при больших коэффициентах умножения..

Целью изобретения является повышеиие точности умножения..

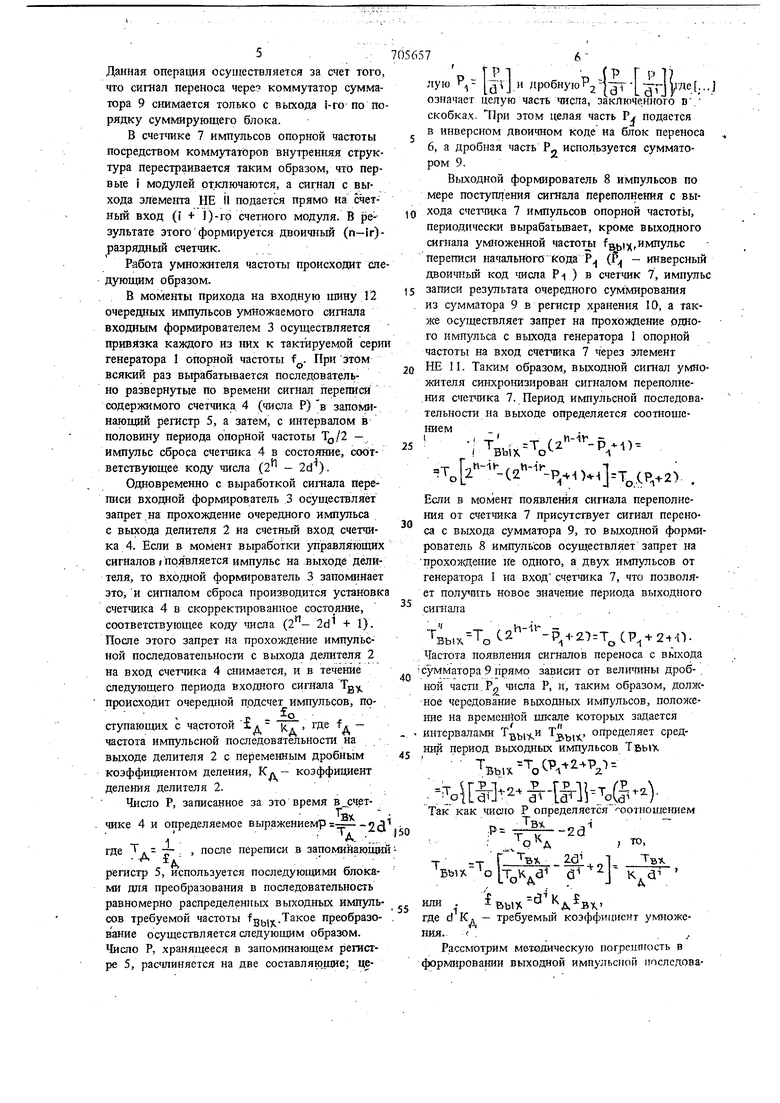

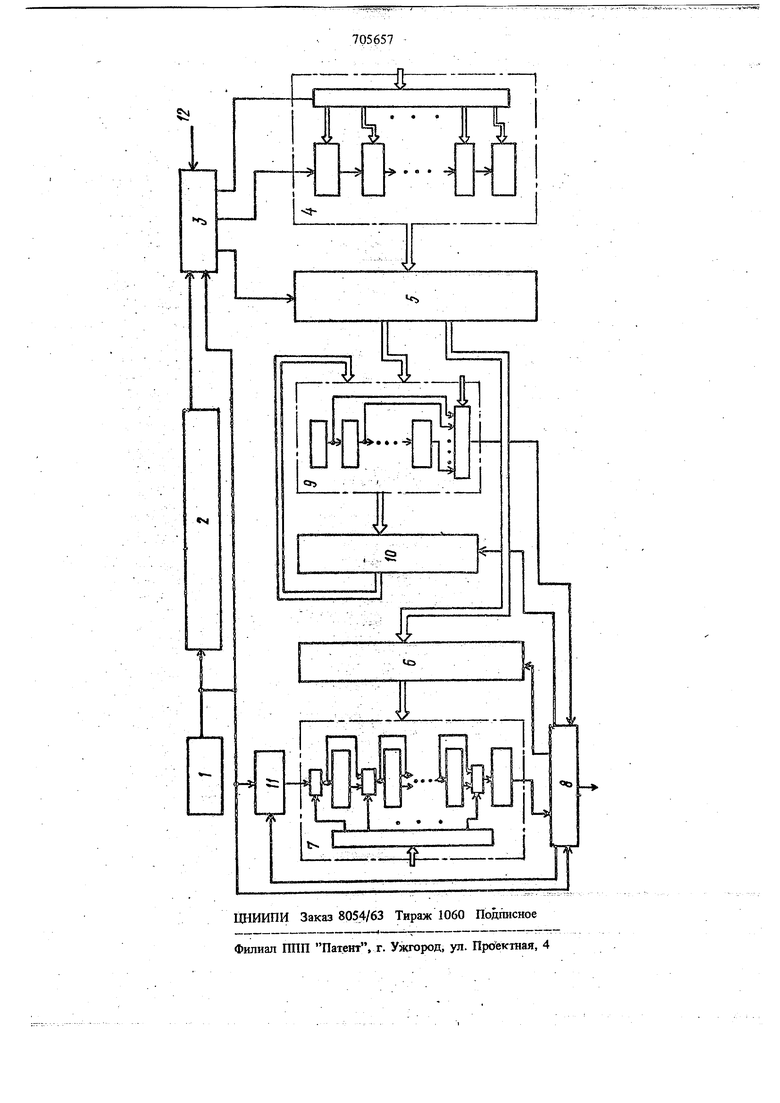

С этой целью в умножитель частоты следования импульсов, со держащийвходной форми.рователь импульсов, первый вход которого соединен с входной шиной, генератор опорной частоты, выход которого соединен с входом делителя частоты, запоминающий регистр, входы которого соединены с выходами счетчика импульсов, а первый выход через блок переноса подключен к первому входу счетчика импульсов опорной частоты, выход которого через выходной формирователь импульсов соединен с вторым входом блока переноса, введен сумматор, регистр хранения суммы и элемент запрета, выЯод которого подключен к второму входу счетчика опорной частоты, первый вход соединен с вторым выходом выходного формирователя импульсов, а второй вход - с выходом генератора опорной частоты и вторым Входом выходного формирователя импульсов, третий вход которого соединен с первым выходом сумматора, первьш.ход ко- . торого соединен с вторым ВЬЕХОДОМ запоминающего регистра, а второй - с выходом регистра хранения суммы, первый вход которою подключен к второму выходу сумматора, а второй вход - к третьему выходу выходного формирователя импульсов, при этом гзторой вход входного формирователя имщльсон соединен с выходом делителя частоты, третий вход - с вькодом генератора опорной частоты, первый выход - с первым входом запо№шающего ре гистра, второй и третий выходы - с входами счетчика импульсов. На чертеже изображена структурная электрическая схема умножителя частоты следова|Ния импульсов. Он содержит генератор 1 опорной частоты, делитель 2 частоты следоващш и тульсов, входной формирователь 3, счетчик 4 импульсов, запош1наю1дий регистр 5, блок переноса 6 параллельного кода, счетчик 7 импульсов опорной частоты, выходной формирователь 8 импульсов, сумматор 9, 10 хранения суммы, элемент НЕ 11 (элемент запрета). Ци рой 12обдзначена входная шина устройства. Счегшк 4 импульсов на п двоичных разря дов состоит, например, из (n-mr)-разрядной пересчетной схемы и последовательно соединен ных с ней мехсду собой m г-разрядных счет.ных модулей, которые управляются коммутатором. Целое число г, определяющее разрядность модулей, задается из соотношения . г logjd (например, при d 10, г 4, а npH.d 2, )-,. Счетчик опорной частоты 7, также .составлен из последовательно соединенных (п-гпг)разрядной пересчетной схемы и mr-разрядных счетных модулей, управление которыми осуще ствляется Через коммутирующие блоки. Сумматор 9, состоящий из вдентичных суммирующих по модулю d блоков, соединенных по цепи переноса последовательно, может переключаться коммутатором на суммирова1ше чисел с перемегшой, но фиксированной (при заданном коде положения запятой) разрядностью слов. Коммутаторы управляются щиной, кодовое состояние которой соответствует необходимому положению запятой в требуемом коэффициенте умножения. Входной формирователь 3-, синхронизируемый генератором 1 опорной частоты, обрабатьгоает входной сигнал, поступающий на вход-, ную шину, и сигнал с выхода делителя 2к частоты следования импульсов с переменным дроб ным коэффициентом деления. Кроме формирования импульсной последовательности, поступающей на вход счетчика 4 импульсов, он вырабатьшает также импульс переписи содержимо го этого счетчика в запоминающий регистр 5 и импульс сброса, счетчика импульсов в исходное состояние. Выходной (|юрмирователь 8 импульсов, также синхронизируемый генератором I опорной частоты и обрабатьгоающий сигнал переполнения счетчика 7 и fflyльcoв опорной частоты и сигнш переноса от сумматора 9, фор fflpyeт выходную импульсную последователь ность устройства и вырабатьшает следующие управляющие сигналы: импульс переписи параллельного кода из запоминающего регистра :5 в счетшк 7 импульсов опорной частоты через блок переноса 6, импульс записи результата суммирования из сумматора 9 в регистр хране шя 10 и сигнал запрета на прохождение импульсов от генератора 1 через элемент НЕ 11 на вход счеттка 7 импульсов опорной частоты. Принцип работы умножителя частоты заключается в следующем. Пусть требуется реализовать умножение на некоторый произвольный козффищ1ент К, который можно представить в системе счисления по основанию d i--(, . -ii. nO. K,,.,,...-.a. ; где (I -I- 1); - максимальная разрядность слов, с которыми может оперировать делитель с перемегшым дробным коэффициентом деления 2, Тогда, учитьшая ограничения, налагаемые на целую часть, коэффивдент деления 2 «-,d--v. при этом 5 -ci- j---6 g a g --j. Следовательно, на шине управления делителем частоты 2 должно устанавливаться состояние. соответствующее кодовой комбинации в И- -аТребуемый коэффициент дополнительного, умножения при этом составляет велйч1шу d . Код, соответствующий данному коэффициенту дополнительного умножения, через тины упраВ ления и коммутаторы подготавливает депи счетчика 4 импульсов, сумматора 9 и счетчика 7 импульсов опорной частоты к реализации заданного коэффициента умножения. В счетчике 4 импульсов при этом первые 1 г-разрядных счетных модулей переключаются на. счет по модулю d, а остальные (m-f) модули и пересчетная схема включаются в цель так, что образуют единый (n-ir)-разрядный двоичный счетчик. Кроме того, коммутатором этого счетчика подключаются к выходу входного формирователя установочные входы триггеров этого счетчика таким образом, что начальная его загрузка будет соответствовать коду числа (2 - 2d). Одновременно с этим сумматор 9 переключается на сзп мированис чисел по модулю d. 5.. Данная операция осуществляется за счет того что сигнал переноса чере коммутатор сумма тора 9 С1шмается только с выхода i-го по по рядку суммирующего блока. В счетчике 7 импульсов опорной частоты посредством коммутаторов внутренняя струк тура перестраивается таким образом, что первые i модулей рт.клгочаются, а сигнал с выхода элемента НЕ il подается прямо на счетный вход (i + i)-rp счетного модуля. В результате этого формируется двоичный (п-ir) разрядньш счетчик. Работа умножителя частоты происходит сл дующим образом. В моменты прихода на входную пшну 12 очередных импульсов умножаемого сигнала входным формирователем 3 осуществляется привязка каждого из imx к тактируемой сери генератора 1 опорной частоты f . При этом всякий раз вырабатывается последовательно развернутые по времени сигнал перешгст содержимого счетчика. 4 (числа Р) в запоминающий регистр 5, а затем, с интервалом в половину периода опорной частоты То/2 -. импульс сброса счетчика 4 в состояние, соответствующее коду числа (2 - 2d ). Одновременно с выработкой сигаала переписи входной формирователь 3 осуществляет запрет.на прохождение очередного импульса с выхода делителя 2 на счетный вход счетчика 4. Если в момент выработки управляющих сигналов (Появляется импульс на выходе делителя, то входной формирователь 3 запоминает это, и сигаалом сброса производится установк счеттека 4 в скорректированное состояние, соответствующее коду числа ( 2d + 1). После этого запрет на прохождение импульсной последовательноста с выхода делитеяя 2 на вход счетчика 4 снимается, и в течение следующего периода входного сигнала Tg происходит очередной подсчет импульсов, . те fд ступающих с частотой 1д частота илшульсной последовательности на выходе делителя 2 с переменным дробным коэффициентом деления, Кд коэффициент деления делителя 2. Число Р, записанное за это время в счртTrawчике 4 и определяемое выражениемр -5с . V-i: , после переписи в запоминающи регастр 5, используется последующими блоками для преобразования в последовательность равномерно распределенных выходных импуль сов требуемой частоты fjj,.Такое преобразование осуществляется следующим образом. Число Р, хранящееся в запоминающем регистре 5, расчлиняется на две составляющие; це7лую Р vJ.H дробнуюPjl- I VjfWJ;... означает целую часть числа, заключе.нного D. скобках. При этом целая часть Р подается в инверсном двоичном коде на блок переноса 6, а дробная часть Р„ используется сумматором 9. Выходной формирователь 8 импульсов по мере поступления сигнала переполнения с выхода счетчика 7 импульсов опорной частотьг, периодически вырабатьюает, кроме выходного сигнала умноженной частоты f,),импульс переписи начального Код;аР (f - инверсный двоичный код 1шсла Pi ) в счетчик 7, импульс записи результата очередного суммирования из сумматора 9 в регистр хранения 10, а также осуществляет запрет на прохождение одного импульса с выхода генератора 1 опорной частоты на вход счегшка 7 через элемент НЕ П. Таким образом, выходной сигнал умножителя синхро шзирован сигналом переполнения счетчика 7. Период импульсной последовательности на выходе определяется соотнощением ; ,Т„ 2 ---С2 ---Р,..(Р,.2 . Если в момент появления сигнала переполнения от счетчика 7 присутсгвует сигнал переноса с выхода сумматора 9, то выходной формирователь 8 импульсов осуществляет запрет на прохолэдегпге Не одного, а двух импульсов от генератора I на вход счетчика 7, что позволяет получить новое значение периода выходного сигаала h-ii- :-Т„С2 -P,-Z7-T CP 2- iV Частота появления сигналов переноса с выхода Сумматора 9 прямо зависит от вел1тошы дроб- . ной части.РЛ числа Р, и, таким образом, должное чередование выходных импульсов, положе1ше на временйой шкале которых задается интервала1 /ш Т.ц,|-, , определяет средшш период выходных импульсов Vt - Q V -Pz-..cg-). Так как число Р определяется оотноше1О1ем п, TBIJ. „ , 1 ,р--2d .. о -Tr-J-M 2:d .„1 где d К. - требуемый коэффициент умножеия. . . Рассмотрим методическую по грепп гость в ормирова1ши выходной импульсной послсдовательности. Так как измерение периода умножа мой частоты производится в результате запоминания дискретной последовательностью эталонных импульсов временного интервала, равного входному периоду, то максимальная погрешность в определении числа Р не превышает единицы младшего разряда

/P-TI51,

где Р - реальное полученное в предварительном 4 стеленное значение выражения

/11М.,

гаЛ

При этом максймальньш набег по фазе в выходной умноженной последовательности за время очередного периода входного сигаала доставит Т,

Л тахТ

Bi;

BbDS, Bb

aic

И21Г

выи

в умножителях частоты, реализуемых по принципу полушния коэффи1|иента умножения, равного коэффициенту делегшя, м аксимальная велншна набега фазы в выходной поспедовательности определяется выражегшем

То (Т.

Г То (

mavc-2JC L BtoW

ъь

2 т.

BbiA Hj таким образом, из -отношения

.с.л аУ j

1

видно, что чем больше лачение козффищента умножения, тем более точно по отношению к сравниваемым устройствам реализуется в предложе1шом умгюжителе частоты требуемый коэффициент умножения.

Если величину ограничить значением 2iT, то при заданном диапазоне изменений целой части коэффициентов умножения от 1 до 1000, верхний п рёдел.:вь1хрдных частот определяется из выражения ;..,,.

. 1

YВЫХ К Ю(для заявленного .устройства), .V

У

,,1о

-е

(для прототипа),

ше d 10;

При частоте генератора fg равной 4-10 Гц,

числе1Шые значения предельных частот соответственно равны:

о/г.

mqy. VK --10 ) 360кГц

(для заявляемогйобъекта)..;

МЧ

2К

. тся IK 10 j прототипа)

VSТаким образом, приведенные соотношения показьгоагат, что настояцдай умножи1ель частоты следования импульсов имеет более точные пр (cpaiBHeifflro с известными характеристики;/, преобразования, особенно при больших значениях коэффициентов умножения, что позволяет применить его в качестве генератора опорных частот для систем обработки сложных сиг налов в более широком диапазоне выходных частот. чФормула изобретения

Умножитель частоты следования импульсов,

содержашдй входной формирователь импульсов, первый вход которого соединен с входной шиной, генератор опорной частоты, выход которого соединен с входом делителя частоты, запоминающий регастр, входы которого соеди5 нены с выходами счгтчика импульсов, а первый выход через блок переноса подключен к первому входу счетчика импульсов опорной частоты, выход которого через выходкой формирователь импульсов соединен с вторым входом блока переноса, о тли чающийс я тем, что, с целью повышения точности умножения, э него введены сумматор, регистр . хранения суммы и элемент запрета, выход которого подключен к второму входу счетчика

j опорной частоты, первый вход соединен с вторым выходомвыход1того формирователя импульсов, а второй вход - с выходом генератора опорной частоты и вторым входом вьрсодного формирователя импульсов, третий вход которого соединен с nepBbiM выходом сумма(тора, первьш вход которого соединен с вторым выходом запоминающего регистра, а второй - с выходом регистра хранения суммы, первьш.вход которого подключен к второму выходу сумматора, а второй вход - к третьему выходу выходного формирователя импульсов, при этом второй вход входного формирователя импульсов соединен с выходом делителя. частоты, третий вход - с выходом генератора опорной частоты, первый выход - с первым входом запоминающего регистра, второй и третий йыходы - с входами счетчика импульсов.

Источники информащш, принятые во вшмание при экспертизе

n

S

IV- Ik

L

Ti

.

ti

Ц

-...

M

S

Авторы

Даты

1979-12-25—Публикация

1977-09-29—Подача