1

Изобретение относится к вычислительной технике и може быть использовано в стохастических вычислитель- ных машинах и устройствах.

Известен стохастический интегратор, содержащий постоянное запоминающее устройство, генератор управляющих случайных последовательностей и логическую матрицу 1.

Обладая простотой схемной реализации и возможностью легкой перестройки на воспроизведение различных функций, такой интегратор требует вместе с тем значительного объема пЬстояннрго запоминающего устройства и большого количества управляющих случайных последовательностей.

Известен также стохастический интегратор, содержащий сдвйгаквдий регистр с комбинационным сумматором на входе, одноразрядный генератор

случайных символов и схему сравнения 2 .

Обладая простотой аппаратурной реализации, такой интегратор имеет, однако, низкое быстродействие ввиду последовательного принципа организации вычислений.

Наиболее близким по технической сущности к предлагаемому является стохастический интегратор, содержа-. ,

щий п-разрядный накопитель подынтегральной функции, вход которого является входом интегратора, генератор случайных чисел,, генератсф тактовых импульсов, блок сравнения, пербый вход которого соединен с выходом генератора случайных чисел, тактируямдий вход соединен с тактирующим входом накопителя подынтегральной функции и с выходом генератора.тактовьи,, импульсов, а выход является выходом; устройства ЗГ.

Недостатком указанного интегратора является его аппаратурная сложность, основную долю которой составляют п-разрядные генератор случайных чисел и блок сравнения, предназначенные для верйоятностного преобразования п-разрядньк значений подынтегральной функции.

Цель изобретения упрощение стохастического интегратора.

Поставленная цель достигается

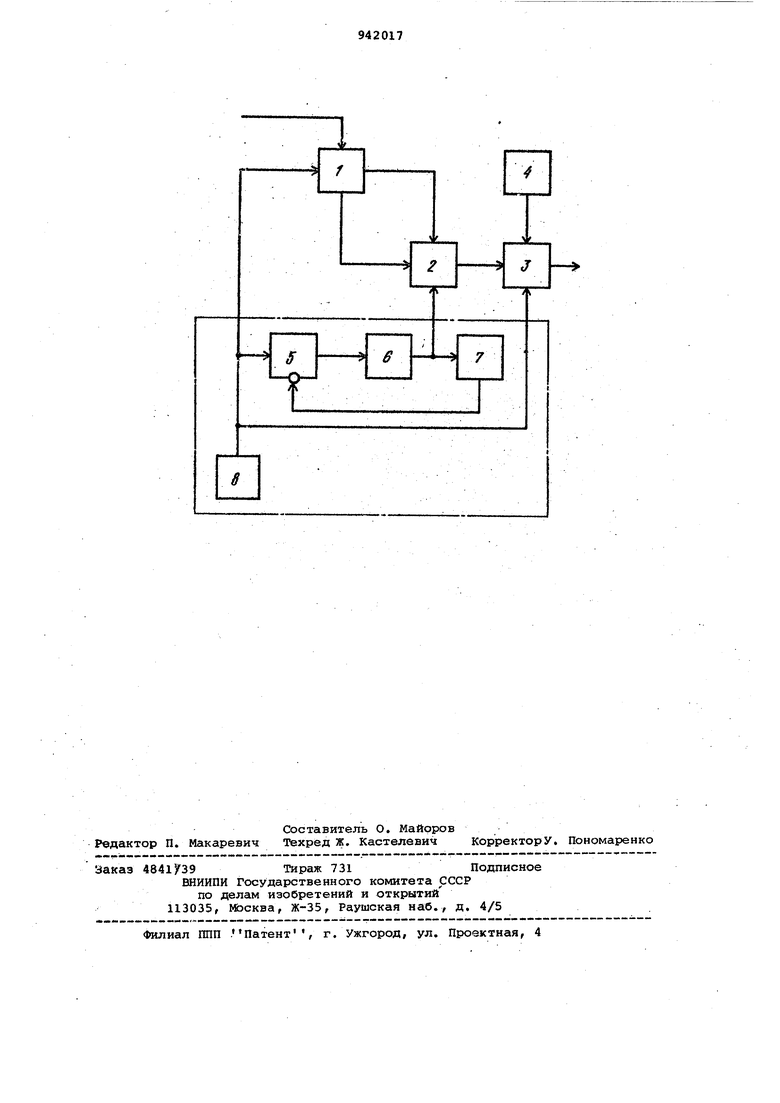

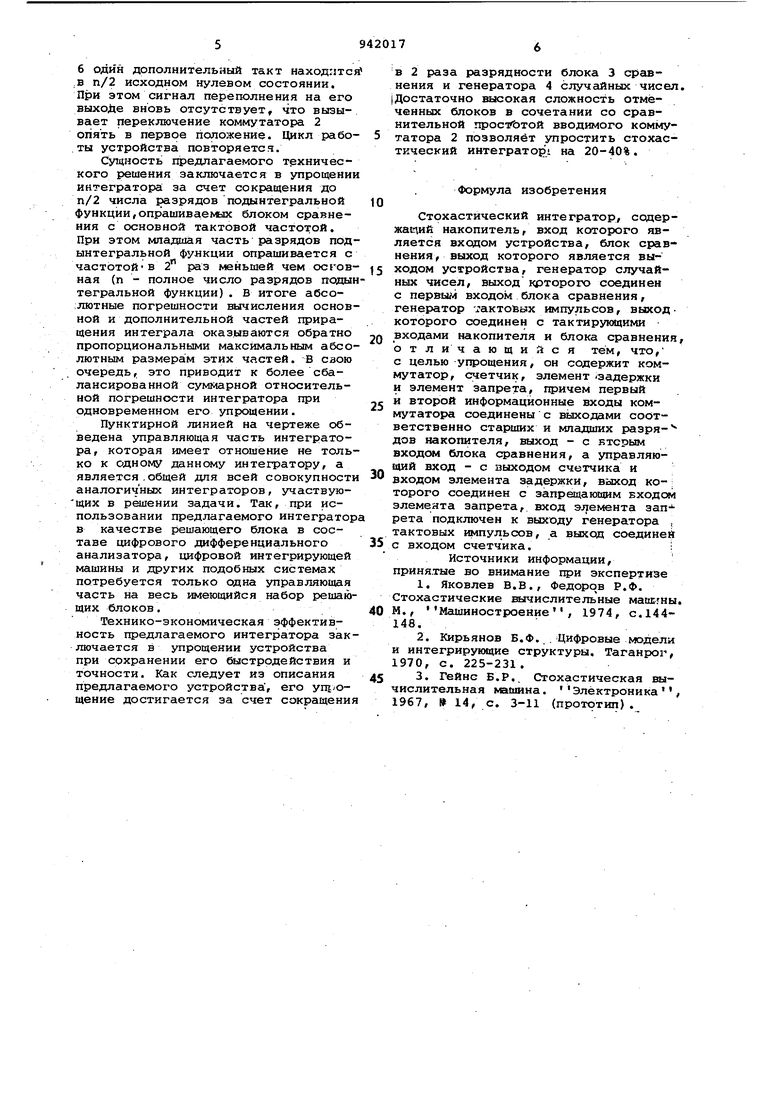

. :тем, что стохастический интегратор, содержащий накопитель,вход которого является входом устройства, блок сравнения, выход которого .является выходом устройства, генератор слу, .чайных чисел, которого соеди нен с первым входом блока сравнения. генератор тактовых импульсов, выход которого соединен с тактирующими входами накопителя и е5лока сравнени дополнительно содержит .атор, счетчик, элемент задержки и элемент запрета, причем первый и второй информационные входы коммутатора сое динены с выходами соответственно старших и младших разрядов накопите ля , выход - с вторым входом блока сравнения, а управляющий вход - с выходом счетчика и входетл элемента задержки, выход которого соединен с запрещающим входом элемента запрета вход элемента запрета подключен к выходу генератора тактовых импульсов, а выход соединен с входом счет чика, На чертеже представлена блок-схе ма стохастического интегратора. Интегратор содержит накопитель 1 коммутатор 2, блок 3 сравнения, генератор 4 слу1айных чисел, элемент запрета, счетчик б, элемент 7 задер ки, генератор & тактовых импульсов. Вход накопителя 1 является входом интегратора. Выходы п/2 старших и п/2 младших разрядов накопителя 1соединены соответственно с первым и вторым информационными входами ком,-.1утатора 2, выход которого соеди нэн со зторым входом блока 3 сравнения. Выход генератора 4 случайных чисел соединен с первым входом блок 2сравнения, выходкоторого являетс выходом интегратора. Выход генератора 8 тактовых импульсов соединен с тактирующими входами накопителя 1 и блока 3 сравнения, а также с входом элемента 5 запрета, выход которого соединен с входом счетчика 6. Выход счетчика 6 соединен с, управляющим входом коммутатора 2 и входом элемента 7 задержки, выход которого соединен с запрещающим вхо дом элемента 5 запрета. Интегратор работает следующим образом.. . Перед началом процесса вания в накопитель 1 заносится начальное п-разрядное значение подынтегральной функции у(х.) . Счетчик б находится в исходном - нулевом состоянии, которому соответству - т отсутствие сигнала переполнения на его выходе. Коммутатор 2, управляемый этим сигналом, находится в первом (из двух) положении, при котором второй вход блока 3 сравнения подключён к выходу старших п/2 разрядов накопителя. Процесс интегрирования инициируе ся тактовыми -т-тульсами, вьфабатываемыали-генератором 8 тактовых импульсов. При этом, счетчик б черея открытый элемент 5 запрета начинает подсчет поступающих на его вход так товых импульсов, а 1блок 3 сравнения бсуществляет преобразование содержимого старших п/2 разрядо:а насопителя 1 (.} в случайную последовательность .имАульсов: tftl U.t.Jf 41Л V.rW. f Siqcn У5.(Х.),еслиА 44 :)с(4НИ1): О, если(( i 0,1,2,... . где /л.(1) - случайные числа, равномерно распределенные ц интервале 0,1, вырабатываемые генератором 4 случайных чисел. Полученная последовательность L,.(i) поступает на выход интегратора. Накопленг е этой последовательности в соответствии с методом Монте-Карло позволяет получить приближенную оценку интеграла: i ZiX,-)plX)dX i/lXD t:j.(K), (I) . Xo где шаг интегрирования для основной частоты. (Операция накопления (2) выполняется, в другом аналогичном интеграторе или отдельнг.гл накопителе, входящем в состав вычислительного устройства). Одновременно с вьщачей последовательности 2(1) на вход иутегратора поступает входная случайная последовательность 1,(1), которая по мере накопления в накопителе 1 образует текущие значения подынтегральнсл функции у(х). y(X;i)y(x)+ л xvt(i) (3) 1 0,1,2,... В описанном режиме устройство работает до тех пор,пока счетчик 6 не заполнится до состояния 11 1 1. Л. m1/1 Тогда очередной тактовый импульс вызывает переход счетчика б в исходное нулевое состояние, а на его выходе формируется сигнал переполнения,, который переводит коммутатор 2 во второе положение. В этом положении блок 3 сравнения подключается к выходу младших п/2 разрядов накопителя 1 и за один такт осуществляет однократное преобразование содержимого младших п/2 разрядов накопителя 1 у(х,) в символ случайной- последовательности: ,(;). wlxjj еслиАО)|5„(х,,-Н ги Iо (1)(х)Ь (4) ,1,2,.. ., ,l,2,... В следующем такте задержанный в элементе 7 сигнал переполнения закрывает элемент 5 запрета. Псэследний .блокирует поступление на вход счетчика 6 очередного тактового импульса и тем самым задерживает на один такт переход счетчика в состояние 0000.,.01. В результате в счетчике

6 один дополнительный такт находите в п/2 исходном нулевом состоянии. При этом сигнал переполнения на его выходе вновь отсутствует, что вызывает переключение коммутатора 2 опять в первое положение. Цикл работы устройства повторяется.

Сущность предлагаемого трхнического решения заключается в упрощении интегратора: за счет сокращения до п/2 числа разрядов подынтегральной функции,опрашиваемлх блоком сравнения с основной тактовой частотой. При этом младдаая часть разрядов подынтегральной функции опрашивается с частотойВ 2 раз меньшей чем осговная (п - полное число разрядов подынтегральной функции). В итоге абсо;лютные погрешности вычисления основной и дополнительной частей приращения интеграла оказываются обратно пропорциональньоми максимальным абсолютным размера м этих частей. В саою очередь, это приводит к более сбалансированной суммарной относительной погрешности интегратора при одновременном его упрощении.

Пунктирной линией на чертеже обведена управляющая часть интегратора, которая имеет отношение не только к одному данному интегратору, а является.общей для всей совокупности аналогичных интеграторов, участвующих в решении задачи. Так, при использовании предлагаемого интегратор в качестве решающего блока в составе цифрового дифференциального анализатора, цифровой интегрирующей машины и других подобных системах потребуется только одна управляющая часть на весь имеющийся набор решающих блоков.

Технико-экономическая эффективность предлагаемого интегратора заключается в упрощении устройства при сохранении его быстродействия и точности. Как следует из описания предлагаемого устройства , его ущющение достигается за счет сокращения

в 2 раза разрядности блока 3 сравнения и генератора 4 случеийных чисел.

iДостаточно высокая сложность отмеченных блоков в сочетании со сравнительной вводимого коммутатора 2 позволяет упростить стохастический интегратор; на 20-40% .

Формула изобретения

Стохастический интегратор, содержасдий накопитель, вход которого является вхсадом устройства, блок сравнения, выход которого является выходом устройства, генератор случайных чисел, выход крторого соединен с первым входом блока сравнения, генератор такто вых импульсов, выходкоторого соединен с тактирующими входами накопителя и блока сравнения отличающийся тем, что, с целью упрощения, он содержит коммутатор, счетчик, элемент -задержки и элемент запрета, причем первый и второй информационные входы коммутатора соединеныс выходами соответственно старших и младших разрядов накопителя, выход - с нтсрым входом блока сравнения, а управляющий вход - с выходом счетчика и входом элемента задержки, выход ко-; торого соединен с запрещающим входом элемента запрета,, вход элемента запрета подключен к выходу генератора , тактовых импульсов, а выход соединей с входом счетчика.i

Источники информации, приня.тые во внимание щ)и экспертизе

1.Яковлев В.В., Федор9В Р.ф. Стохастические илчислительные машгтны Н., Машиностроение, 1974, с.144148.

2.Кирьянов Б.Ф. . Цифровые модели и интегрирующие структуры. Таганрог, 1970, с. 225-231.

3.Гейне Б.Р., Стохастическая вычислительная машина. Электроника 1967, 14, с. 3-11 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастический интегратор | 1978 |

|

SU744607A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| Следящий стохастический интегратор | 1979 |

|

SU789998A1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

| ПРЕЦИЗИОННЫЙ ИМИТАТОР РЕАЛИЗАЦИЙ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099785C1 |

| Псевдостохастический интегратор | 1981 |

|

SU962938A1 |

| Стохастическое вычислительное устройство | 1982 |

|

SU1062700A1 |

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

| Следящий стохастический интегратор | 1990 |

|

SU1728868A1 |

| Устройство для вероятностного моделирования | 1980 |

|

SU922707A2 |

Авторы

Даты

1982-07-07—Публикация

1980-11-19—Подача