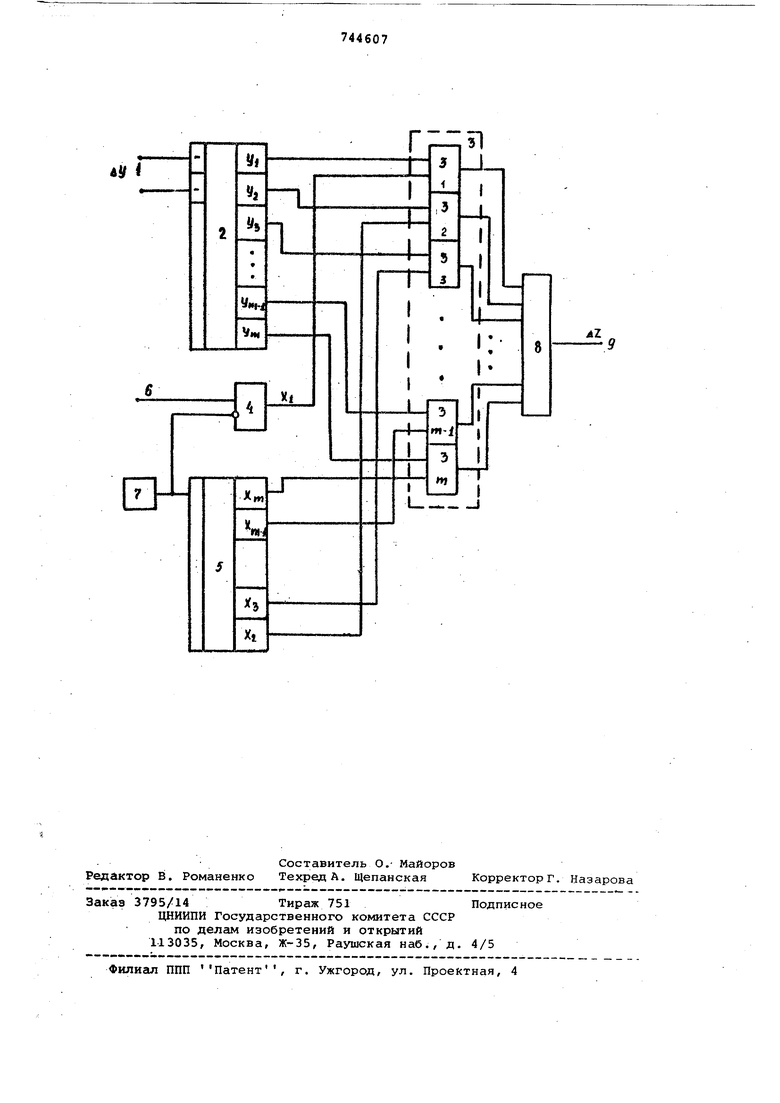

Изобретение относится к вычислительной технике и может быть использовано при построении стохастических вычислительных устройств. Известны стохастические интегра,торы, содержащие последовательно гаразрядный накопитель .подинтегральной функции, входы которого подключены к входам интегратора и блок стохастического кодирования; состоит из т-разрядной схемы сравнения чисел в параллельных кодах и генератора случайных чисел, представляющего собой m датчиков равновероятных случайных двоичных последовательностей 1 и 2 .Недостатком этих интеграторов являются большие аппаратурные затраты, необходимые для построения параллель ной схемы сравнения и многоразрядного генератора случайных чисел. Наиболее близок к предлагаемому стохастический интегратор, содержащий реверсивный счетчик,суммирую1ди счетчик, одноразрядный датчик случай ных чисел, группу элементов И и элемент ИЛИ, выход которого является вы ходе интегратора, входами интеграто являются входы реверсивного счетчина, выходы элементов И подключены ко входам элемента .ИЛИ, выход од нор аз- . рядного датчика случайных чисел соединен со входом суммирующего счетчика , выходы которого подключены к импульсным входам соответствующих элементов И, выход переполнения реверсивного счетчика через инвертор и выходной вентиль подключен к выходу интегратора 3. Однако такой интегратор имеет существенный недостаток - интеграл, текущее значение Y которого находится в реверсивном счетчике, преобразуется в выходную стохастическую последовательность Z с масштабом Р(х), т.е. Р(т)-Р fx). 9 где Р() - вероятность появления единицы в выходной последов ательности Р(Х)о,5 - вероятность появления единицы в последова тельнсЯйти X. Умножение на масштаб Р(х)0,5 при интегрировании приводит к увеличению веса последовательности Z, что в бсльшинстве применений весьма нежелательно, так как приводит к снижению точности интегрирования. Цель изобретения - повьвление точ нсх-ти и упрошение интегратора. Поставленная цель достигается те что в стохастический интегратор, со держа 4ий реверсивный счетчик ,-сумми рующий счетчик, одноразрядный датчик случайных чисел, группу элементов И и элемент ИЛИ, выход которого .является выходом интегратора, входа чи интегратор являются входы ревер сивного счетчика, выходы элементов И подключены ко входам элемента ИЛИ выход одноразрядного датчика случай чисел соединен со входом суммирующего счетчика, выходы которого подключены к импульсным входам соответ ствующих элементов И, соединенных своими потенциальными входа « И с выходами (т - 1) младигих разрядов реверсивного счетчика, дополнительн введен элемент запрета, выход которого подключен к импульсному входу элемента И, соединенного своим потенциальным входом с выходом старшего разряда реверсивного счетчика, запрещающий вход элемента зап рета соединен с выходом одноразрядного датчика случайных чисел, а прям вход элемента запрета является входом синхронизации интегратора; На чертеже предстгшлена блок-схе ма интегратора. Стохастический интегратор содержит входы 1 интегратора, реверсивны счетчик 2, группу элементов И 3, эл мент 4 запрета, сукадирующий счетчик 5, вход б синхронизации интегратора одноразрядный датчик 7 случайных чис элемент ИЛИ 8, выход 9 интегратора. Вход 1 приращений интеграла л у (положительных и отрицательных) .под ключен ко входу младшего т-го разряда реверсивного счетчика 2. Выходы числовых разрядов реверсивного счетчика 2 подключены к потенциальным входам m эпементов И 3;(,т), причем выход 1-го разряда (отсчет ведется со старшего разряда) подклю чен ко входу 1-го элемента З, . Импульсные входы элементов И под ключены к выходу элемента 4 запрета и к выходам счетчика 5. Причем вход элемента 3 подключен к выходу элемента 4 запрета, а вход каждого элемента 3; (1 2, т) подключен к выходу (т-1+1)-ого разряда счетчика 5. Прямой вход элемента 4 запрета подключен к шине б синхронизирующих импульсов СИ. Выход датчика 7 случайной двоичной последовательности X подключен к запрещаюцему входу элемента 4 и к счетному входу счетчика 5. Выходы всех элементов З; (,in) подключены ко входам элемента ИЛИ 3, выход которого подключен к выходу 9 интегратора. Устройство работает следующим образом.. . После включения питания хтатчик 7 формирует случайную последовательность X с вероятностью появле О и 1 ния двоичных символов в каждом такте Р ( х) ( х) 0 , 5 . Последовательность X поступает на запрещающий вход элемента 4 и на счетный вход счетчика 5. Нуль последовательности х разрешает прохождение импульса син- . хронизации СИ с шины б на выход элемента 4 - формируется единичный символ последовательности х . Поскольку в счетчике 5 при не переключается ни один разряд, то остальные последовательности х. 0. т формируемые на выходах счетчика &, имеют нулевые значения. Таким образом/ единичные значения последовательности с вероятностью Р(х )Р(х) 1 Р(х) 0,5 2 поступают на вход элемента 3), Единица последовательности х запрещает прохождение синхроимпульса на выход элемента 4 - формируется нулевой символ последовательности х.. При этом единица, поступающая на счетный вход счетчика 5 вызывает в последнем переключении в единичное состояние лишь одного из разрядов, например, (т - i + 1)-ого (,т-1). Переключение (т-i+l)-oro разряда из нуля в единицу врспринимается импульсным входом элемента 3; как единица последовательности х,, . Таким образом,: последовательности X, j/ f f входах элементов И образуют послеовательности несовместимых событий, т.е. в данном такте единица появляется только лишь в одной из последовательностей. Вероятность появления единицы в последовательностях x,j,X3,... Xrr,c учетом Р(х) 27равной соответственно ((. P(( P{X)P(xV2-f -.7 Перед началом процесса интегрирования в реверсивный счетчик 2 заносится начальное значение интеграла УО (в частном случае равное нулю) . В процессе интегрирования на вход 1 реверсивного счетчика 2 поступают стохастические последовательности положительных или отрицательных приращений интегралаtuУ . Поступающие приращения интеграла фиксируются реверсивным счетчиком 2, преобразующим интегральные стохастические последовательности ±ЛУ в двоичный код текущего значения интеграла У,которое в процессе интегрирования преобразуется в стохастическую последовательность приращений ftZ с помощью датчика 7, элемента 4, счетчика-5, элементов И 3 и элемента 8. Выходная последовательность приращений л Z представляе С-бой интеграл от входной последова тельности ду . Преобразование интеграла Y в стохастическую последовательность приращений осуществляется следующим образом. Последовательности х., х с вероятностями Р(х), Р(х)2, ..., Р (Хгг,) 2 опрашивают соответстУ счетчвенно разряды Y. i На выходах элементов 3 формируются стохасти - , 1 ческие последовательности вероятностями P(z,y.2 p((V-v.a Указанное фОЕЭмирование последов тельности Z; (,т) заключается в пропускании на выход элемента 3j символов последовательности Х| в тактах, в которых Y-, 1 . В тактах, когда Y-J О, символы последователь ности Х; на выход элемента 3-, не пропускаются, т.е. в последователь сти Zj в эти такты формируются нул Поскольку последовательности то несовместными являются последовательности Z, , Z , . . . , Z и, следовательно, на элементе ИЛИ 8 осуществляется сложение указанных последовательностей с полным суммиро нием вероятностей. Р(z) P(z ,- , р (тс j .5 V, Q- У, т.е. выходная последовательность имеет математическое ожидание (вероятность) появления единицы в каждом такте, в точности равное текущему значению интеграла без до полнительных масштабных множителей В предлагаемом стохастическом интеграторе математическое ожидани (вероятность) появления единицы в выходной стохастической последовательности равно текущему значени интеграла. Это означает равенство весов входной и выходной стохастич ких последовательностей, что при реализации сложных математических зависимостей позволяет исключить блоки выравнивания весов стохастич ких последовательностей и приводит к уменьшению аппаратурных затрат при решении сложных математически зависимостей, систем уравнений и т.п. Дополнительное уменьшение .п оборудования в предлагаемом интеграторе происходит от замены достпточно сложного счетного триггера суммирующего счетчика более простым элементом запрета. Кроме того, отсутствие эффекта увеличения в ее: а импульса выходной последовательности (отсутствие эффекта прореживания) предлагаемом интеграторе обеспечивает снижение дисперсии этой последовательности в два раза, а погрешности случайного отклонения стохастического представления - в VT раз по сравнению с дисперсией и погрешностью известного интегратора. Формула изобретения Стохастический интегратор, содержащий реверсивный счетчик, суммирующий счетчик, одноразрядный датчик случайных чисел, группу элементов И и элемент ИЛИ,выход которого является выходом интегратора, входами интегратора являются входы реверсивного, счетчика, выходы элементов И подключены ко входам элемента ИЛИ, выход одноразрядного датчика слу- : чайных чисел соединен со входом суммирующего счетчика, выходы которого подключены к импульсным входам соответствующих элементов И, соединенных своими потенциальными входами с выходами (т - 1) младших разрядов реверсивного счетчика, о тличающийся тем, что, с целью поБЬЕнения точности и упрощения интегратора, он дополнительно сбдержит элемент запрета( выход которого подключен к импульсному входу элемента И, соединенного своим потенциальным входом с выходом старшего разряда реверсивного счетчика, запрещающий вход элемен-, та запрета соединен с выходом одноразрядного датчика случайных чисел, а прямой вход элемента запрета является входом синхронизации интегратора. Источники инфор мапии, принятые во внимание при экспертизе 1.Яковлев В.В., Федоров Р.Ф. Стохастические вычислительные машины. Л., 1974 с. 148 - 150. 2.Авторское свидетельство СССР 491139, кл. G Об J 1/02, 1975. 3.Авторское свидетельство СССР 344458, кл. G Об F 15/36, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стохастический интегратор | 1984 |

|

SU1215120A1 |

| ДЕТЕРМИНИРОВАННО-ВЕРОЯТНОСТНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1972 |

|

SU428412A1 |

| Следящий стохастический интегратор | 1990 |

|

SU1728868A1 |

| Стохастический интегратор | 1980 |

|

SU942017A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| Стохастическое вычислительное устройство | 1982 |

|

SU1062700A1 |

| СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР | 1972 |

|

SU344458A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Следящий стохастический интегратор | 1982 |

|

SU1061141A1 |

Авторы

Даты

1980-06-30—Публикация

1978-01-09—Подача