(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОПТИМАЛЬНЫХ ПАРАМЕТРОВ МИКРОЭЛЕКТРОННЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Система автоматической оптимизации | 1983 |

|

SU1125602A1 |

| Система автоматической оптимизации | 1986 |

|

SU1310773A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ ОПТИМИЗАЦИИ | 2006 |

|

RU2320006C2 |

| Устройство для синтеза регрессионных моделей многомерной статистики | 1980 |

|

SU942031A1 |

| Устройство для прогнозирования состояния технических объектов | 1982 |

|

SU1104533A1 |

| Оптимизатор | 1974 |

|

SU514270A1 |

Изобретение оi ioci/тся к вычислительной технике и может быть использовано для определения оптимальных параметров микроэлектронных схем при их разрабо гке и проектировании.

Известно устройство, содержащее блок формирования управляющих сигналов, генератор тактовых импульсов, распределитель опроса параметров модели, элементы коммутации, блок физической модели, блок контроля выходных параметров физической модели, блек памяти параметров отказов по параметрам, блок сдвиговых регистров,блок счетчиков формирования допусковой области, блок регистров коррекции положения допусковой области, блок выдачи команд проверки работоспособности f1.

Однако в данном устройстве не учитываются особенности технологических операций подготавливаемых схем.

2

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее блок памяти, блок хранения матриц и последовательно соединенные блок регистрации блок умножения, первый сумматор, блок деления, управляемый блок умножения, второй сумматор, блок сравнения и компаратор, причем первый выход блока хранения матриц подключен

10 к второму входу управляемого блока умножения, а второй его выход связан с первым входом блока регистрации, вход блока хранения матриц подсоединен к входу устройства,второй выход управ15ляемого блока умножения связан с вторым входом блока регистрации,выход второго сумматора подключен к входу блока памяти, выход;которого соединен с вторым входом блока сравнения, связанного по выходу с управляющим входом управляемого блока умножения 2,

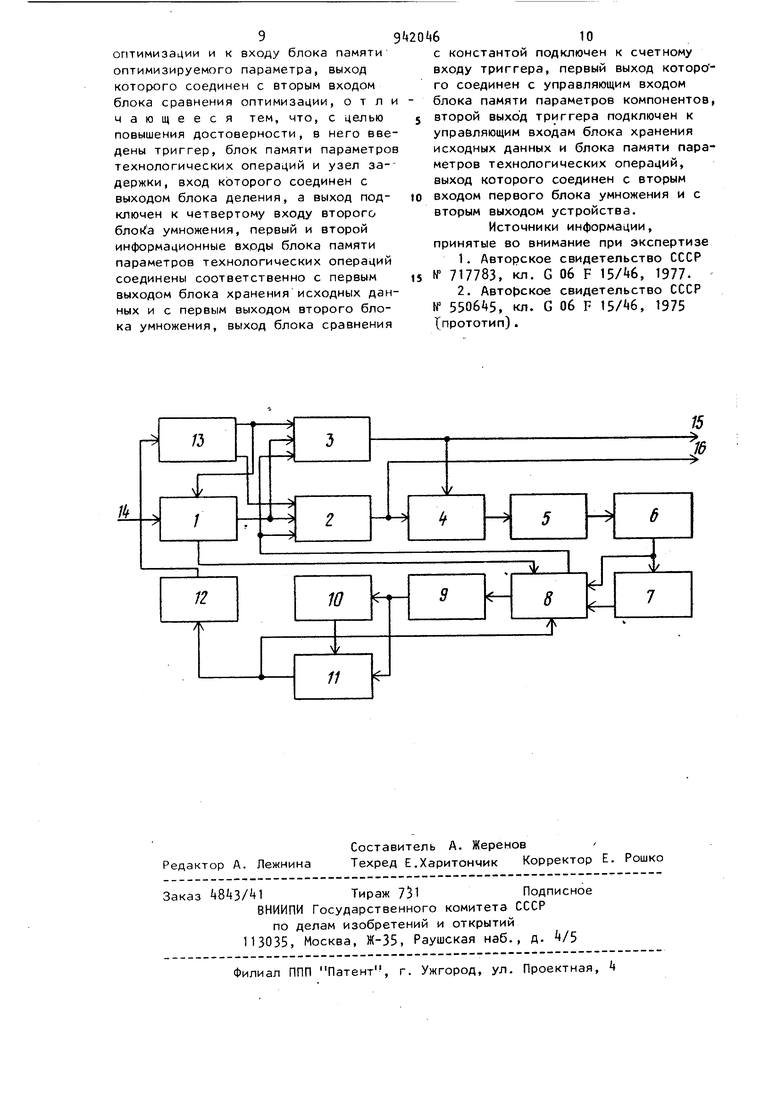

Однако в данном устройстве недостаточно эффективно используется ходная информация, которая поступает на вход и используется для построения регрессионной зависимости, связывающей выходные параметры схем и параметры ее компонентов. Кроме того, в случае проектирования микроэлектронных схем эта информация, обычно представляемая в виде результатов реализации матрицы планирования активного эксперимента, который может быть легко реализован при изготовлении опытной ггартии проектируемых схем, содержит сведения не только о параметрах компонентов в выходных характеристиках схемы, а также о статистических и функциональных связях этих параметров и характеристик, но и об особенностях технологических операций техпроцесса изготовления этих схем, что никаким образом не учитывается в известных устройствах оптимизации К этому следует также добавить, что известное устройство предполагает мо дег Ирование электронной схемы путем автоматической сборки физической модели, а это практически неприемлеМО при проектировании микроэлектронных схем, с:так как вносит большую погрешность в конечный результат изза неадекватности физической модели и реальной микросхемы. Цель изобретения - повышение достоверности получаемых результатов при работе устройства. Поставленная цель достигается тем что в устройство, содержащее блок памяти оптимизируемого параметра, блок хранения исходных данных, первы блок умножения, выход которого соеди нен с входом первого сумматора, выход которого соединен с входом блок деления, второй блок умножения, вто рой сумматор, блок сравнения оптими зации, блок сравнения с константой и блок памяти параметров компонентов, выход которого соединен с первым входом первого блока умножения и с первым выходом устройства, информационный вход блока хранения исходных данных является входом устройства,первый и второй выходы блока хранения исходных данных подключены соответственно к первому информационному входу блока памяти параметров компонентов и к первому входу второго блока умножения второй вход которого и вход блока срав нения с константой соединены с выходом блока сравнения оптимизации, третий вход второго блока умножения соединен с выходом блока деления, первый выход подключен к второму информационному входу блока памяти параметров компонентов, второй выход второго блока умножения соединен с входом второго сумматора, выход которого подключен к первому входу блока сравнения оптимизации и к входу блока памяти оптимизируемого параметра, выход которого соединен с вторым входом блока сравнения оптимизации, введены триггер, блок памяти параметров технологических операций и узел задержки, вход которого соединен с выходом блока деления, а выход подключен к четвертому входу второго блока умножения, первый и второй информационные входы блока памяти параметров технологических операций соединены соответственно с первым выходом блока хранения исходных данных и с первым выходом второго блока умножения, выход блока сравнения с константой подключен к счетному входу триггера, первый выход которого соединен с управляющим входом блока памяти параметров компонентов, второй выход триггера подключен к управляющим входам блока хранения исходных данных и блока памяти параметров технологических операций, выход которого соединен с вторым входом первого блока умножения и с вторым выходом устройства. На чертеже представлена схема предлагаемого устройства. Схема включает блок 1 хранения исходных данных, блок 2 памяти параметров компонентов, блок 3 памяти параметров технологических операций, блок умножения, сумматор 5, блок 6 деления, узел 7 задержки, блок 8 умножения, сумматор 9, блок 10 памяти оптимизируемого параметра, блок 11 сравнения оптимизации, блок 12 равнения с константой, триггер 13, выходы 15 и 16 устройства. ход Блок 1 предназначен для хранения результатов реализации матрицы планирования активного эксперимента, которые получают при изготовлении опытной партии микросхем. Блок 2 служит для записи части данных матрицы, содержащейся в блоке 1 и несущей информации о выходных характеристиках и параметрах компонентов микросхемы, а также для запоминания текущих и окончательных результатов оптимизации этой схемы. Блок 3 предназначен для записи части данных матрицы, содержащейся в блоке 1 и несущей информацию о вы ходных характеристиках и параметрах технологических операций реализации микросхем, а также для запоминания -текущих и окончательных результатов оптимизации этих операций. Блок А умножения, блок 6 деления и сумматор 5 служат для вычисления коэффициентов уравнения регрессии. Узел 7 задержки предназначен для задержки информации с выхода блока А на время, равное времени вычисления оптимизируемого выходного параметра. Блок 8 умножения необходим для определения шагов изменения парамет ров при движении по градиенту оптимизируемой характеристики, Сумматор 9 предназначен для вычи ления величины оптимизируемого выход ного параметра на каждом шаге оптимизации . Блок 10 служит для запоминания значения оптимизируемого параметра. Блок 1I сравнения оптимизации Предназначен для сравнения оптимизи руемого параметра на разных шагах оптимизации. , Блок 12 сравнения с константой представляет собой пороговое устрой ство, состояние которого изменяется на противоположное,, если входной сигнал становится меньше определенной наперед заданной величины. Триггер 13 предназначен для упра ления блоками 2 и 3, а также блоком Рассмотрим работу устройства в сл чае, когда информация, поступающая на его вход 14, представляет собой реализацию матрицы планирования активного эксперимента, полученную в процессе проектирования пленочной микросхемы, которое обычно включает в себя и изготовление опытной партии этих схем. Составление плана и реали зация такого эксперимента в данном случае предполагает, что варьируемыми параметрами, т.е. принудительно изменяемыми в процессе реализации опытной партии микросхемы, являются не только параметры компонентов, но и параметры оптимизируемых технологических операций.-Допустим, что параметром качества микросхемы служи один . из ее выходных параметров, а оптимизируемой технологической опера цией является операция, наиболее важ НйЯ с точки зрения ее влияния на разброс параметров компонентов. Например, в случае пленочной технологии такой операцией является напыление на подложку разистивного слоя. Задача оптимизации решается данным устройством в два этапа. На первом этапе определяется режим операции напыления, обеспечивающий минимальный разброс параметров пленочных резисторов. Это и позволяет значительно улучшить результаты оптимизации на втором этапе, когда производится параметрическая оптимизация микроэлектронной .схемы. Устройство работает следующим образом. При включении устройства блок 12 находится в одном из устойчивых состояний, последнее устанавливается при воздействии на его вход начального выходного сигнала блока 11, который по величине значительно превышает порог опрокидывания блока 12 за счет введения в блок 10 произвольной константы. Если блок 12 собран на базе логической схемы ИЛИ, то при вышеупомянутых условиях на ее выходе устанавливается логическая 1, что, в свою очередь, установит триггер 13 в сойтояние, когда сигнал с его выхода открывает информационные входы блока 3. При этом со входа 1 устройства в блок 1 поступает информация о результатах реализации матрицы планирования активного эксперимента, которая запоминается этим блоком. Одновременно с этим в блок 3 из блока 1 переписывается масть хранящейся там матрицы реализованного активного эксперимента, относящаяся к варьированию параметров оптимизируемой технологической операции. Далее эта информация последовательно поступает в блок Ц умножения, сумматор 5 и блок 6 дег.. ления для вычисления коэффициентов регрессионной зависимости, связывающей в нашем случае параметр качества с оптимизируемыми параметрами техноогической операции. После этого информация с выхода блока 6 деления поступает навход блока 8 умножения, а затем в сумматоре 9 определяется параметр качества, значение которого заносится в блок 10 вместо содеращейся там константы. Последние ри операции занимают время, равное адержке, обеспечиваемой узлом 7 7 g задержки, после чего информация с выхода блока 6 деления через узел задержки поступает также на вход блока 8 умножения. В результате этог в последнем определяются наги перемещения по каждому из параметров. Информация поступает на вход блока 8 умножения с выхода блока 1 - Да. 8 сумматоре 9 определяются нозые зна чения параметров и новое з амение параметра качества. Вычисленное знамение параметра качества полается вблоки 10 и П. Одновременно имеющееся ранее в блоке iO значение подается на вход блока 11, где и проис ходит сргзвнение стаоого и riosoro зна чений параметра качества, 8 зависимости от результата сра8Ь ения производится ил/1 коррекция паоа.етроз н блоке 3 под воздействием но-.ормац.ии о шагах, поступающей с выхода блока 8 умножения., и однозременная коррекция шагов путем воздействи.я выходного сигнала блока 1 на вход б.пока 8 в каждо.м цикле оптимизации., или noe ращение процесса оптим дза1;ии . если вновь полученное .значезние параметра качества отличается от ранее вычисленного на величину, не прееьниающук: порога срабатывания блока 12. В по-след не.м с.гучае состояние 2 изменяется на противоположное, это в свою очередь, вызьшает сраба ыеа-н и е три г г ера 1 3 и , к а к с: л - д с т в и е , запирание Информационнь к р)одпг бло ка 3, отпирание аналогично ;-; входов блока 2 и перепись в пос.ледь ий и блока 1 части резупьт -1ру ; це; ;- атри;; активного эксперимента5 аарьировачит; парамР:-ро;/ ко;-П; -я; -оп микросхемы, после чего ;- а- 1-нае-; ся второй этап оптимизации- папаметрическая оптимизация прош- ипупг ой микросхемы. Работа устройства з это случае происходит aHano -ii-;i-ic . -сак м на первом этапе,, с тем ,1ить ;;1г:1ииием, что на блока 2 в Ko-iiie процесса оптиг изации по.лу -ае;-: опт-:-1мальные неличинь параметров микросхемы, в то время как HG выходе бло КЗ 3 после окончания первого этапа оптимизации получаем оптимальные зн чения параметров ре;кима оптимизир,уе мой технологической операции, Очевидно, что оптимизация параме ров режимов технологических операци позволяет значительно уменьшить раз брос- параметров компонентов как а п делах одной партии микросхема, и 8 от партии к Г|артии,. что, в свою очередь, вы.; ыаает уменьи1ение разбросов В|- Ходных параметров микросхе.м. Поскольку наря.ду с этим определяются и оптимальные параметры компонентов микросхемы, уже на этапе реализации второй партии микросхем можно получить улу-киение их выходных характеристик, значительно превышающее эф от чисто параметрической оптимизации компонентов, что как раз и обусловлено возможностью одновременного использования результатов оптимизации и операций техпроцесса и .внутренних параметров микросхем. 11спользо8ание предлагаемого устройства р автоматических системах управления производством микроэлектронных устройств позволит значительно улучшить технические характеристики последних, а также существе.ино повысить процент выхода годных микросхем при их серийнхом производстве. Формула изобретения Устройство ,для вычисления оптимальных пapa eтpoв гмикроэлектронных схем, с-одержа1цее блок памяти оптимизируемого пап-аметра, блок хранения исходных даннь1Х.; первый блок умножения, ь;:оторого соединен с входом первогосу.чматора, которого соединен с входом блока деления, второй блок у--1ножения, второй сумматор, блок сравнения ог1тимизации. б,пок сравнения г константой Si блок памяти параметрог5 компонентов, выход которого соедиHei-i с первым входом первого блока У|-.;: |(;пкения и г первым выходом устройства, инф-ормацион: Ь1Й вход блока хра -1ения исходных данных является входом ,; т ройства , перзьй и второй аыходы блока .хранения исходных данных подключены соответственно к первому информационн.ому входу блока памяти параметров компонентов и к первому входу второго блока у.множения, второй вход которого и вход блока сравнения с константой соединены с выходом блока сравнения оптимизации, третий вход второго блока умножения соединен с выходом блока деления, первый выход подключен к второму информационному входу б.лока памяти параметров компонентов. второй выход второго блока умножения соединен с входом второго с: мматора, выход которого подключен к первому эходу блока сравнения оптимизации и к входу блока памяти оптимизируемого параметра, выход которого соединен с вторым входом блока сравнения оптимизации, о т л чающееся тем, что, с целью повышения достоверности, в него вве дены триггер, блок памяти параметро технологических операций и узел задержки, вход которого соединен с выходом блока деления, а выход подключен к четвертому входу второго блон(а умножения, первый и второй информационные вхрды блока памяти параметров технологических операций соединены соответственно с первым выходом блока хранения исходных дан ных и с первым выходом второго блока умножения, выход блока сравнения 610 с константой подключен к счетному входу триггера, первый выход которого соединен с управляющим входом блока памяти параметров компонентов, второй выход триггера подключен к управляющим входам блока хранения исходных данных и блока памяти параметров технологических операций, выход которого соединен с вторым входом первого блока умножения и с вторым выходом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 717783, кл. G 06 F , 1977. 2.ABTofjcKoe свидетельство СССР W . кл. G 06 F 15/«6, 1975 1 прототип) .

Авторы

Даты

1982-07-07—Публикация

1980-10-30—Подача