ны с первыми входами первого блока умножения, вторые входы которого подключены к выходам первого блока памяти и третьим выходам блока вычитания, выходы которого подключены к вторым входам блока возведения в степень, выходы которого подключены к вторым входам второго блока умножения, третьи входы которого соединены с выходами счетчиков измеренных значений, а выходы - с вторыми входами второго сумматора, выход которого подключен к третьего входу второго блока деления, первый и второй выходы которого соединены соответственно с первым и вторым входами блока сравнения, третий вход которого подключен к выходу второго блока памяти, а выход первого сумматора подключен к третьему входу первого блока деления,первый выход которого подключен к третьему входу блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Цифровой коррелометр | 1983 |

|

SU1113806A1 |

| Устройство для определения ядер нелинейных объектов | 1981 |

|

SU1008747A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Цифровой фазометр | 1982 |

|

SU1033983A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

УСТРОЙСТВО ДЛЯ.ПРОГНОЗИРОВАНИЯ СОСТОЯНИЯ ТЕХНИЧЕСКИХ ОБЪЕКТОВ, содержащее блок сравнения, блок возведения в степень, блок индикации, блок управления, первый блок умножения, выходы которого соединены с первыми входами первого сумматора, первые выходы первого блока деления подключены к первым выходам блока вычитания, отличающееся тем, что, с целью повышения точности и достоверности значений прогнозируемых параметров, оно- содержит аналого-цифровой преобразователь, счетчик импульсов, счетчик числа измерений, счетчики измеренных значений, первый и второй блоки памяти, второй блок умножения, второй сумматор, второй блок деления, блок согласования, причем первый выход блока управления подключен к первому входу аналого-цифрового преобразователя, блока согласования и к первому входу счетчика импульсов, второй выход - к первому входу счетчика числа измерений, третий вьпсод - к первому входу второго блока памяти, четвертый выход - к второму входу счетчика числа измерений, к первым входам счетчиков измеренных значений и к второму входу второго блока памяти, пятый выход к первому входу первого блока памяти, первьй вход - к первому входу второго блока деления, а второй вход к первому выходу счетчика числа измерений и первому входу блока индикации, а третий вход - к выходу блока сравнения, второму входу блока индикации, первьй выход аналого-цифрового преобразователя соединен с вторым входом счетчика импульсов, второй выход - с третьим входом счетчика импульсов и третьим входом счетчика числа измерений, второй выход I которого соединен с первыми входами первого и второго блоков деСО ления, третий выход - с четвертым с входом блока управления и вторым входом блока согласования, третий;. вход которого соединен с вторым выходом первого блока деления, выход-с вторым входом первого блока памяти и с вторыми входами счетчиков измеренных значений, второй вы4 ход - с вторым входом первого сумел со матора, третий выход - с вторым входом первого блока деления, четвертый со выход - с вторым входом блока вычита-ния и третьим входом первого блока памяти, пятый выход - с первым входом блока возведения в степень, шестой выход - с первыми входами второго блока умножения и третьими входами счетчиков; измеренных значений, седьмой выход - с первьм входом второго сумматора, а восьмой выход - с вторым входом второго блока деления, выходы счетчика импульсов соединены с четвертыми входами счетчиков измеренных значений, выходы которых связа

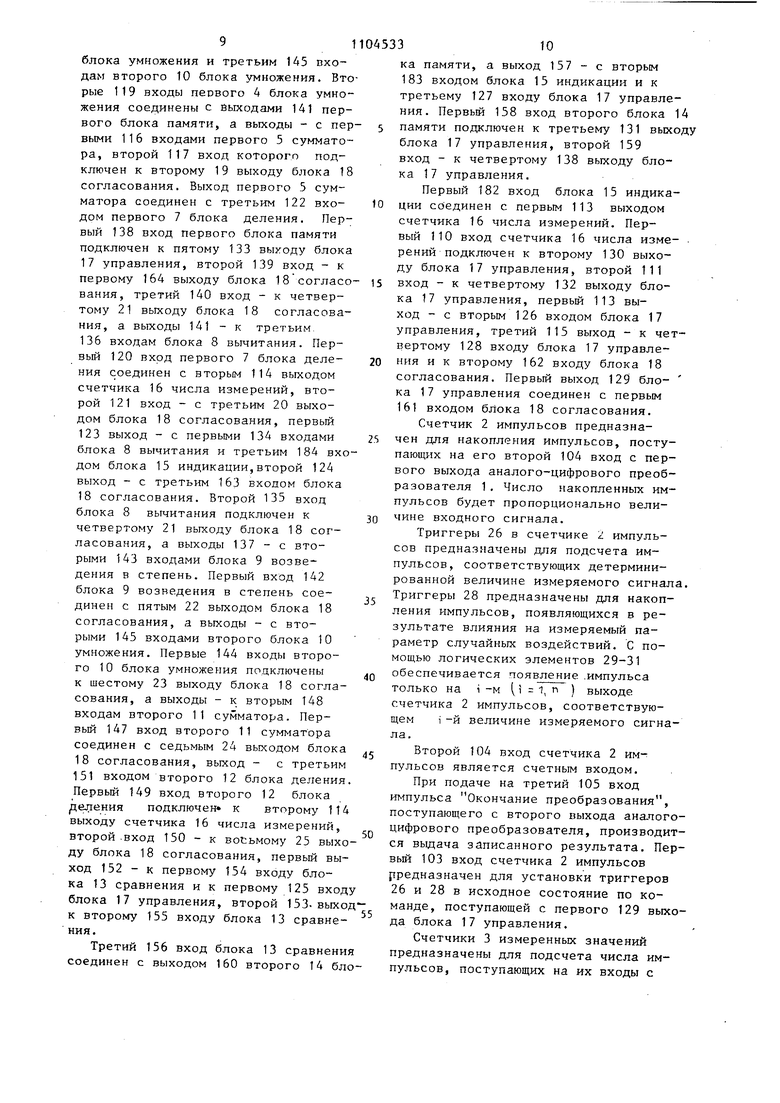

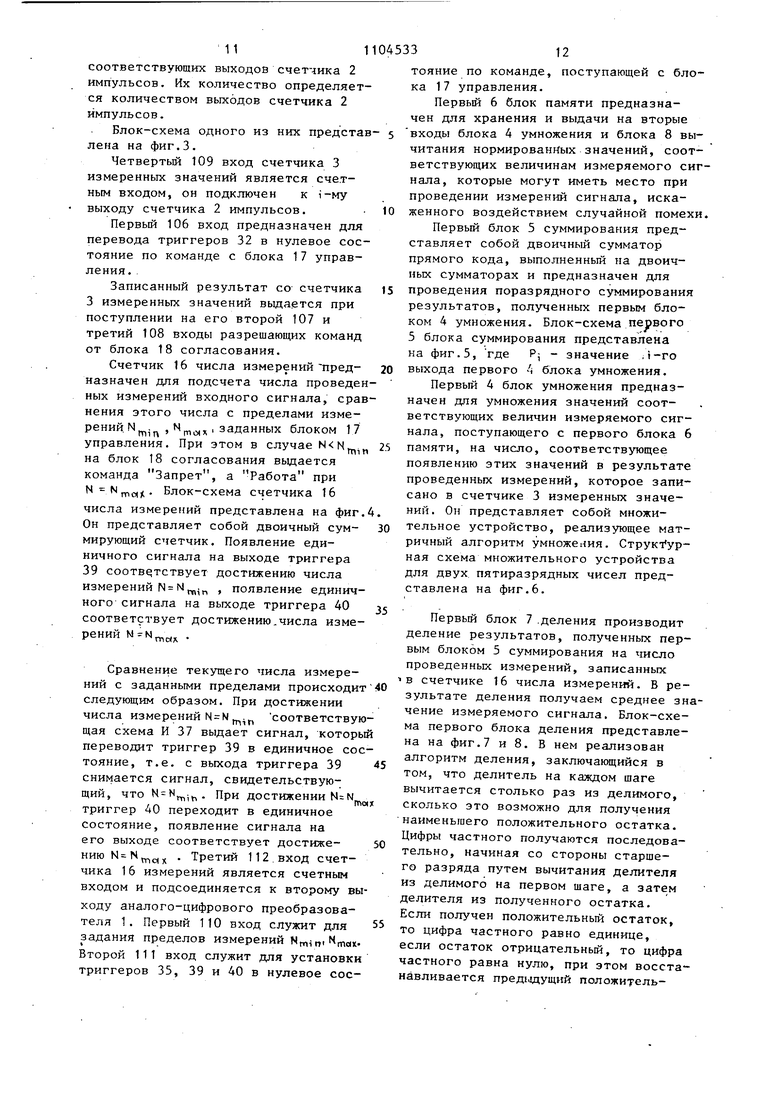

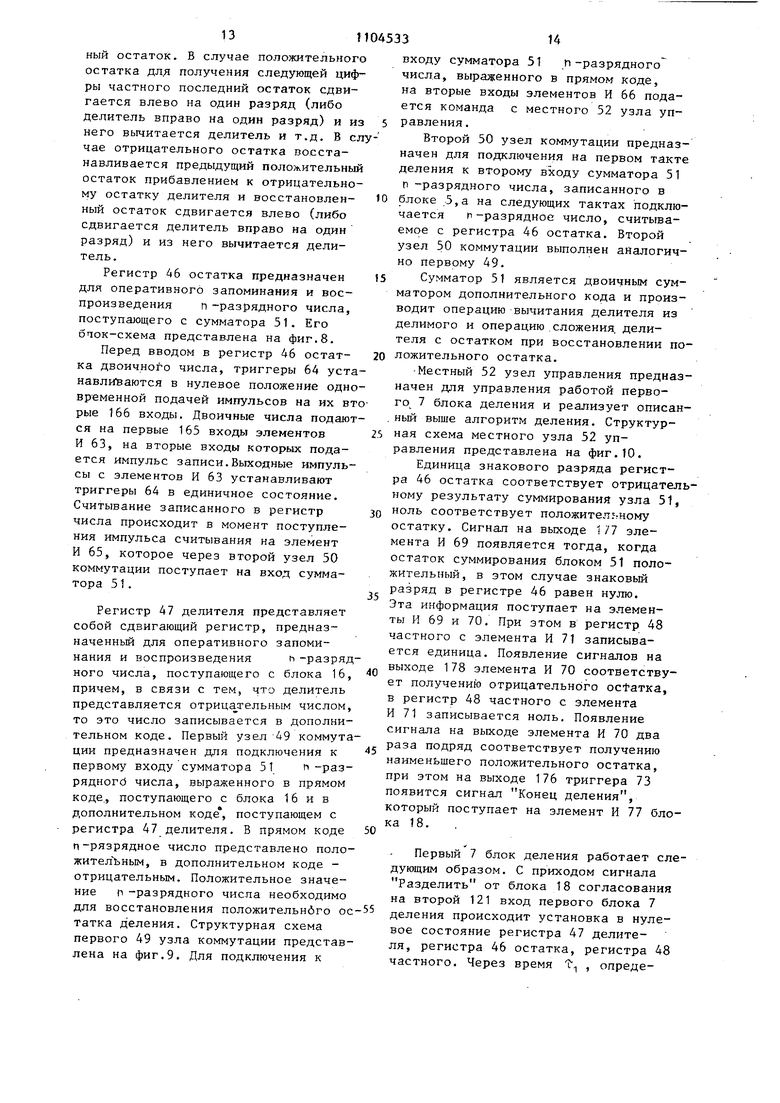

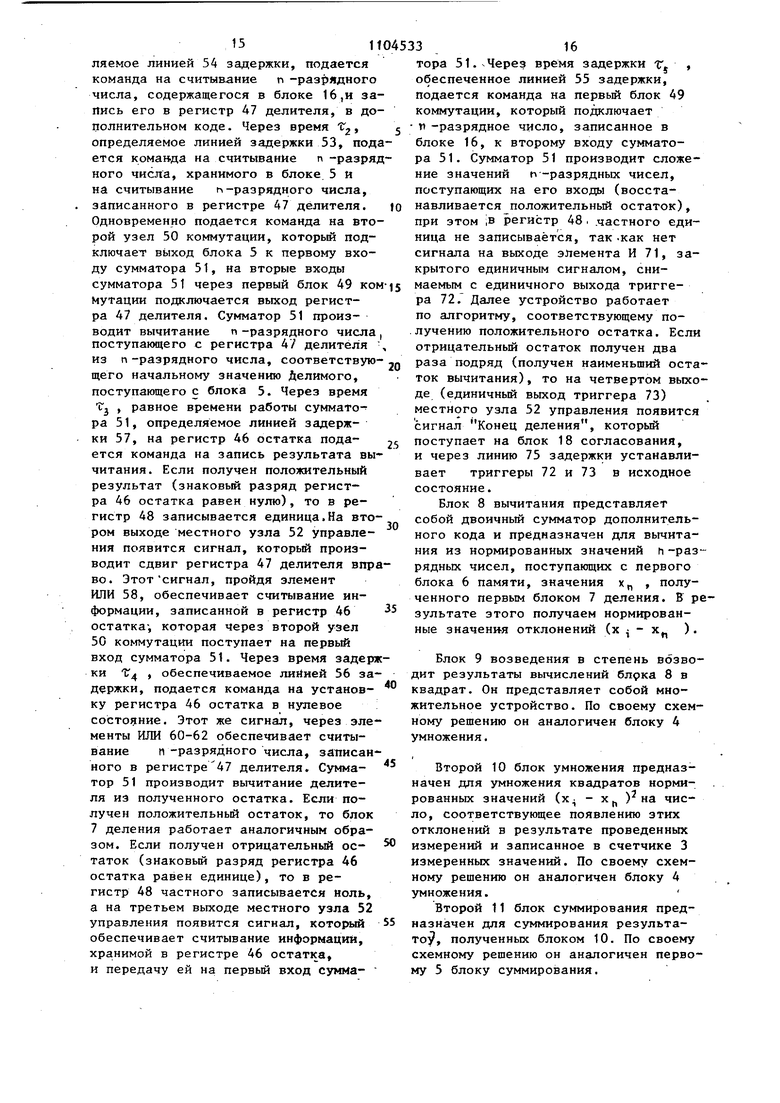

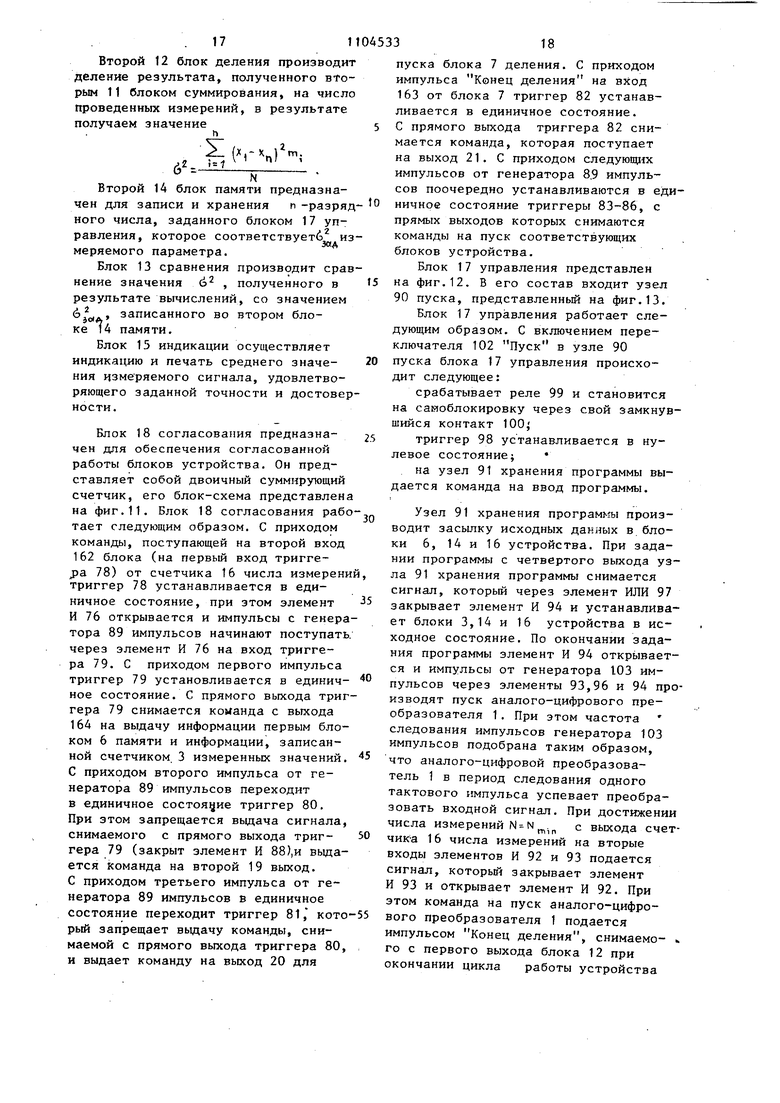

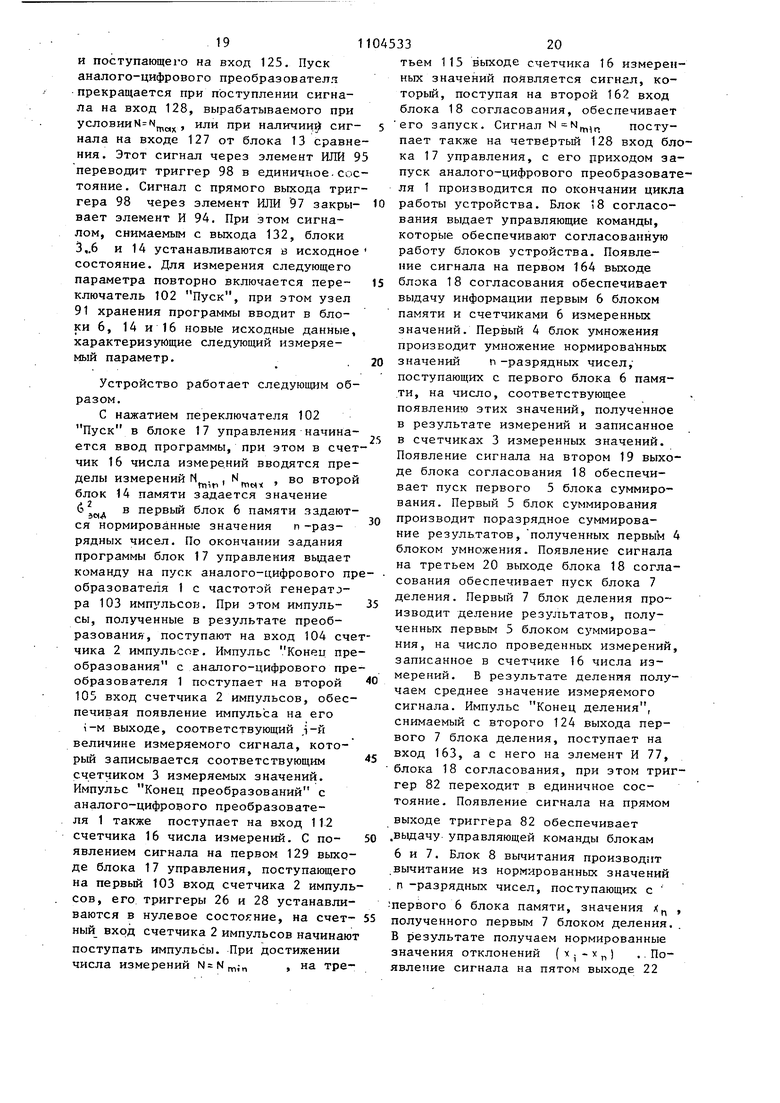

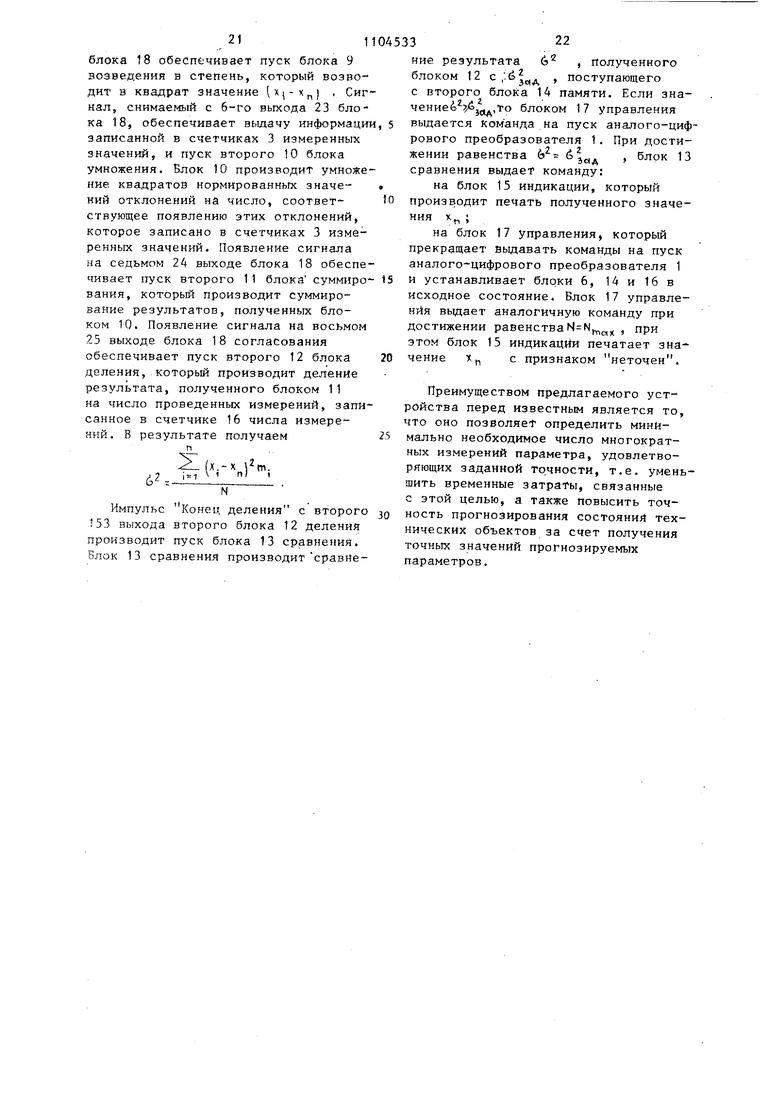

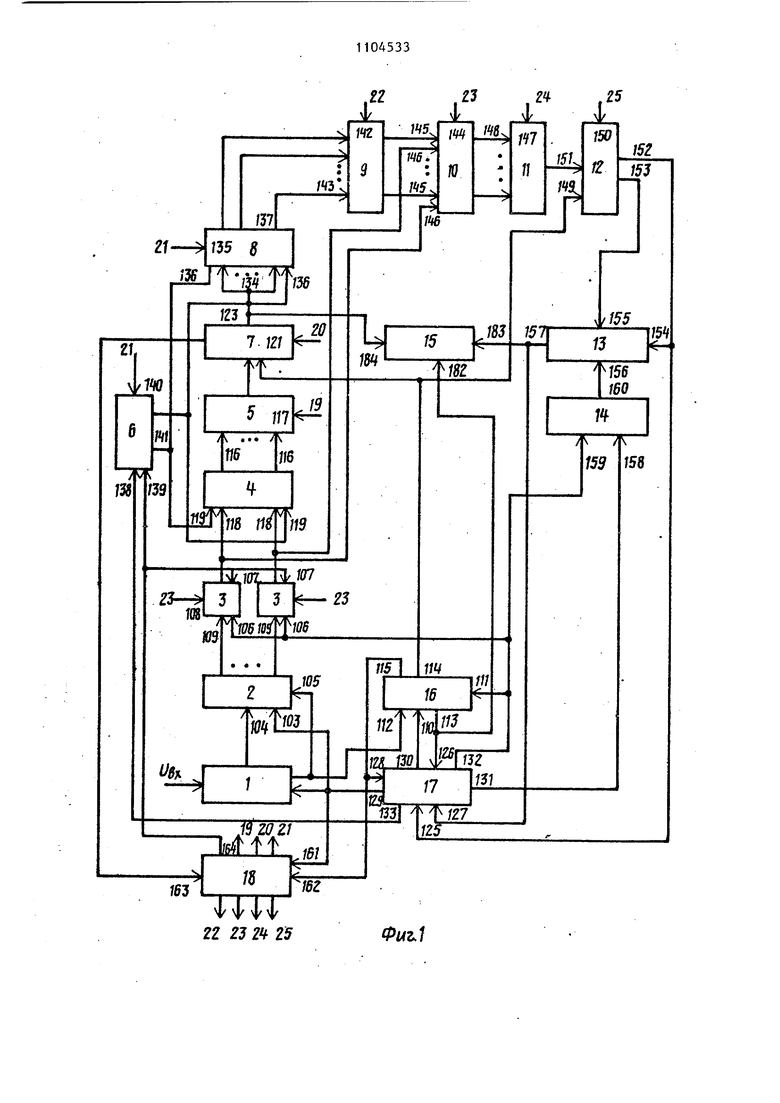

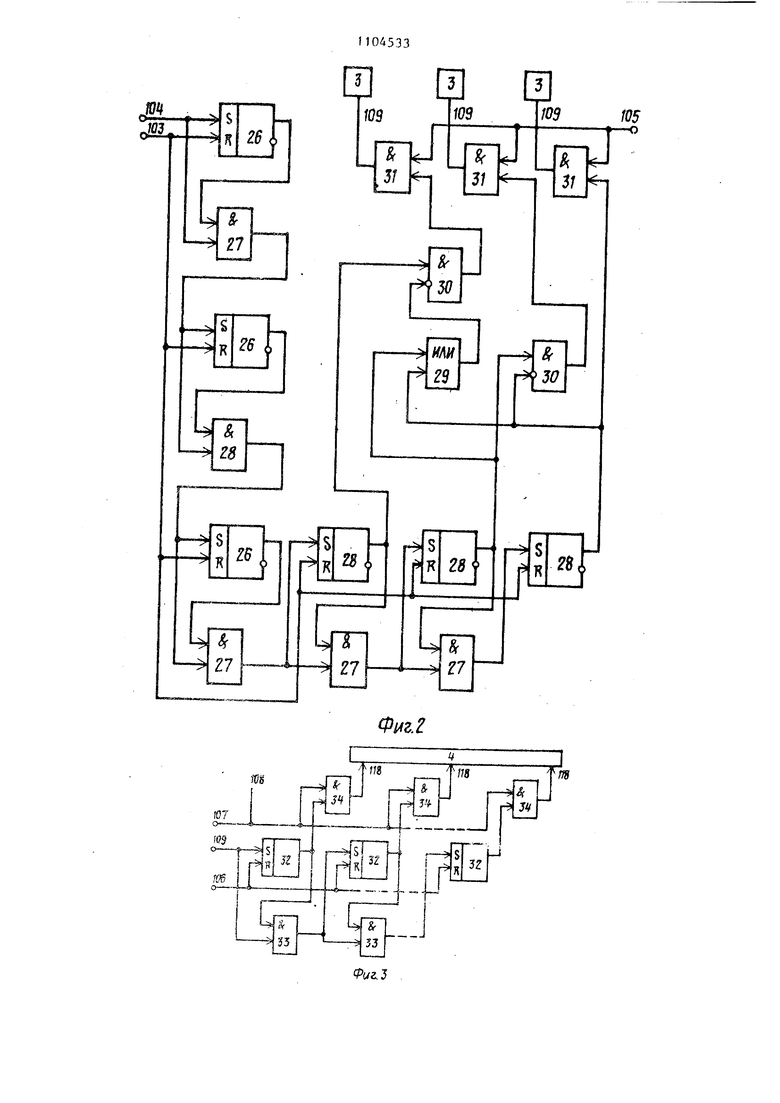

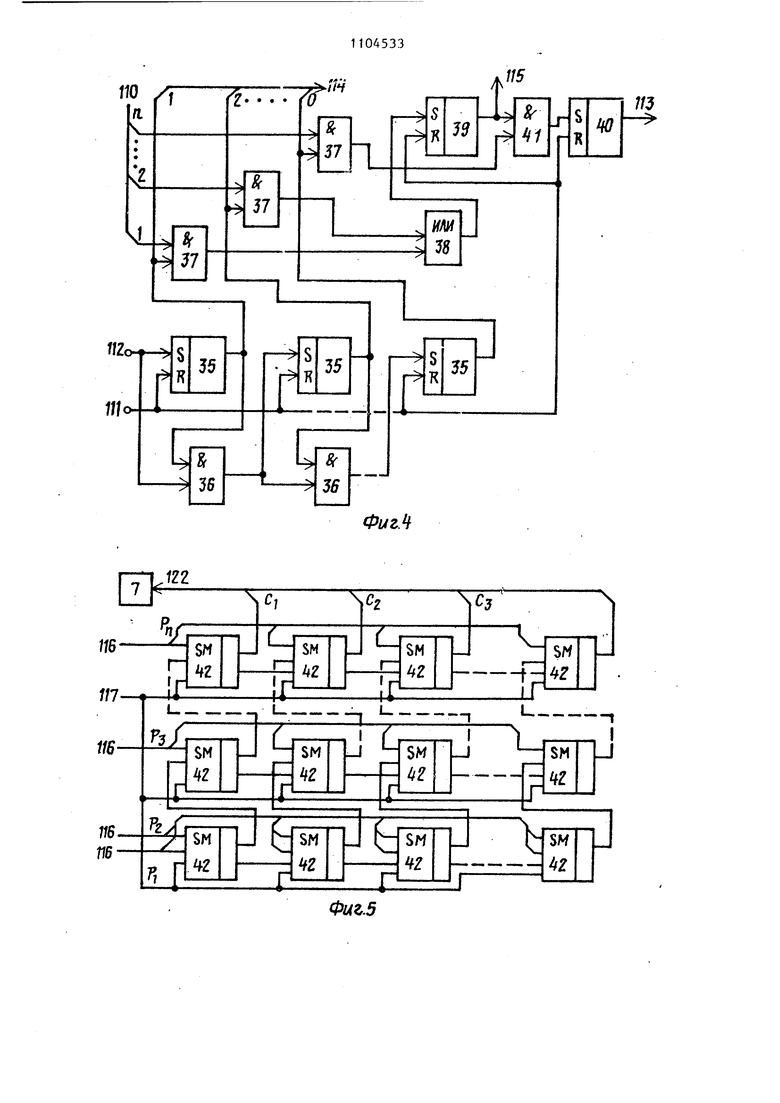

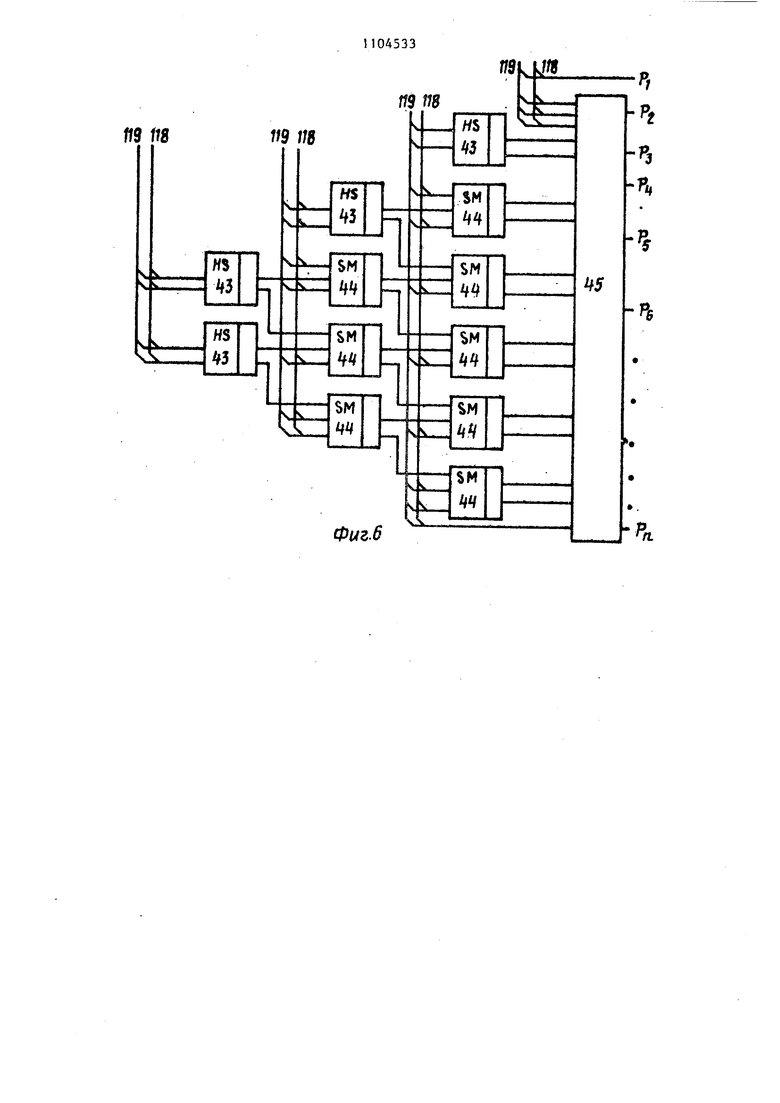

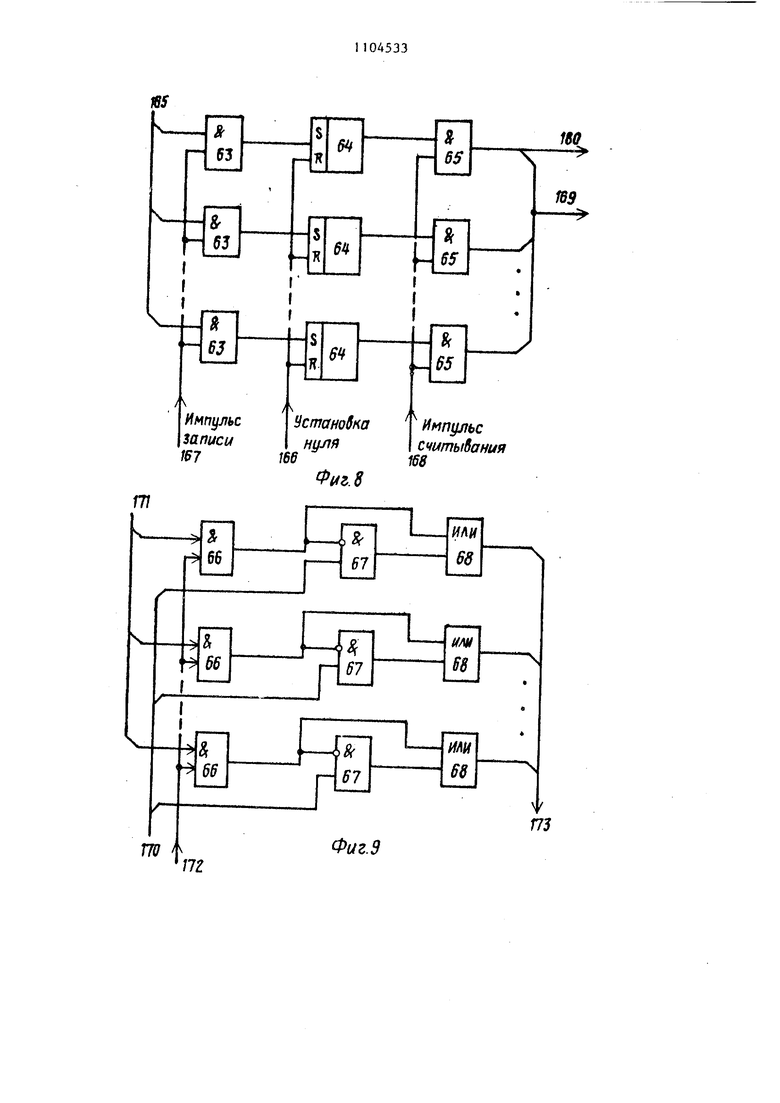

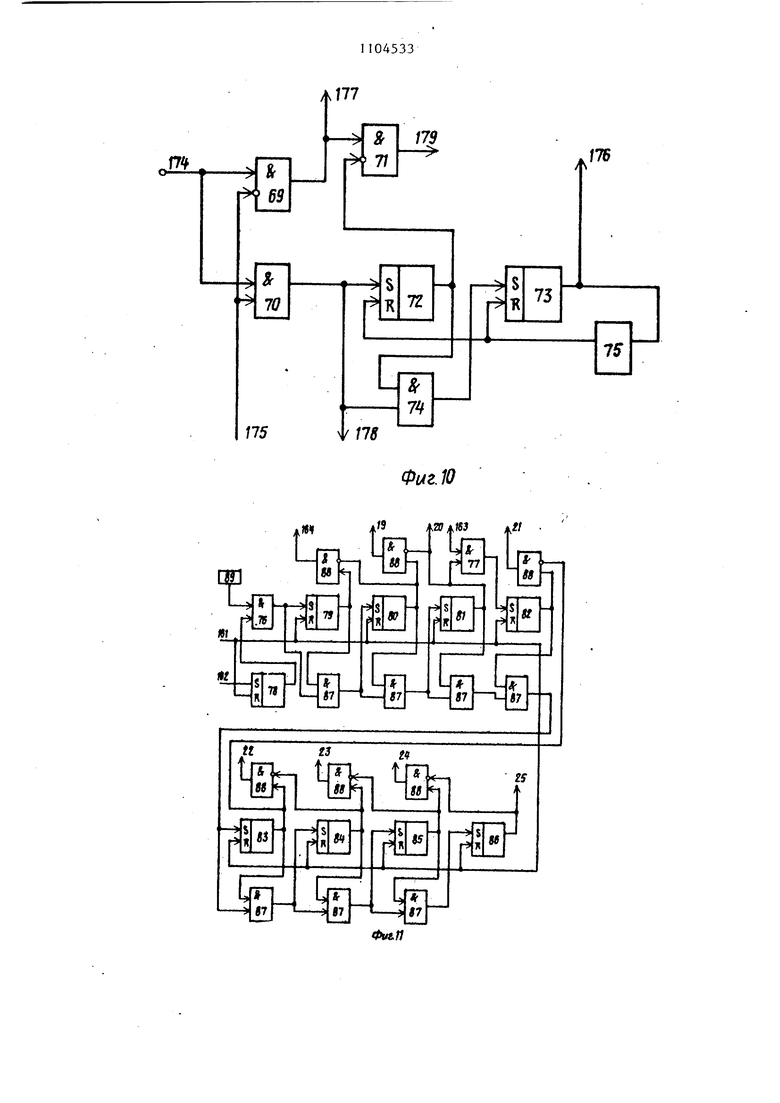

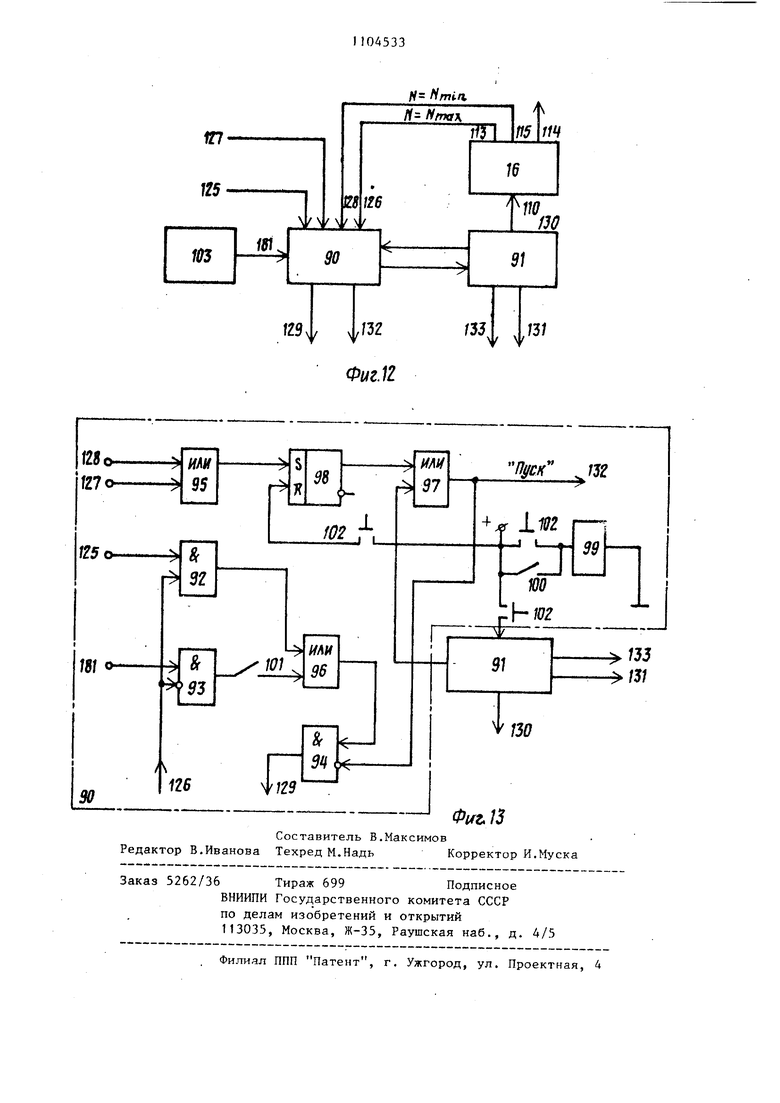

Изоб1)етение относится к вычислительной технике и автоматике и може быть использовано при прогнозировании технического состояния объектов контроля. Известно устройство для прогнози рования параметрической надежности узлов радиоэлектронной аппаратуры, содержащее элементы И, счетчики шагов, запрещенных кодов и задания числа шагов, шаговый коммутатор, бл анализа и блок установки входных параметров, блок управления, выход которого подключен к управляющим входам блоков перебора реализаций, формирования тестовых сигналовjMoделирования, задания допусков и коммутации, первый вход которого со динен с первым выходом генератора тактовых импульсов, второй выход которого подключен к первому входу блока коммутации, третий выход к первому входу блока задания допусков. Выход блока коммутации соединен с первым входом блока моделирования, второй вход которого подключен к выходу блока формирования тестовых сигналов, выход - к втором входу блока задания допусков, первый выход которого соединен с входо счетчика отказов, блок установки входных параметров своим выходом подключен к третьему входу блока моделирования, первый выход блока перебора реализации через пер вый ключ соединен с вторым входом блока коммутации, другой вход перво го блока объединен с вторым входом блока управления и подключен к выходу блока анализа, входы блока анализа подключены к выходам соответствующих элементов И, первые входы которых соединены с вторым выходом блока перебора реализаций, второй вход каждого элемента И подключен к выходу соответствующего счетчика запрещенньгх кодов, вход каждого из которых соединен с соответствующим выходом шагового коммутатора, вход которого соединен с выходом второго ключа, первый вход второго ключа соединен с третьим выходом блока перебора реализаций, второй вход - с вторым выходом блока задания допусков. Выходы счетчика шагов и счетчика задания числа шагов через третий ключ соединены с входом генератора тактовых импульсов, четвертый выход которого подключен к входам блока установки входных параметров и счетчика шаговО . сдостатком данного устройства является невозможность получения значений прогнозируемых параметров, удовлетворяющих требуемой точности и достоверности. Наиболее близким техническим решением к изобретению является устройство для прогнозирования надежности, содержащее коррелятор, выход которого соединен с первыьт яходом анализатора случайного процесса, а вход является первым входом устройства, анализатор своим вторым входом подключен к первому входу устройства, а выходом - к входу вычислительного блока, выход вычислительного блока соединен с первым входом блока возведения в степень, второй вход которого подключен к выходу блока управления, а выход к первому входу блока произведения, второй вход которого соединен через блок дифференцирования с вторым входом сумматора, первый вход сумматора подключен к выходу блока управления, а выход через регистрирующий бл к первому выходу устройства, выход регистрирующего блока соединен с вхо дом блока сравнения, выход которого подключен к входу блока управления, один из выходов блока управления соединен с первым входом блока деления, второй вход которого является третьим входом устройства, а выход через блок вычитания подключен к вто рому выходу устройстваГ2. Недостатком известного устройства является невозможность получения значений прогнозируемых параметров, удовлетворяющих требуемой точности и достоверности. Целью изобретения является повыше ние точности и достоверности значений прознозируемых параметров. Поставленная цель достигается тем что в устройство для прогнозирования состояния технических объектов, содержащее блок сравнения, блок возведения в степень, блок индикации, блок управления, первый блок умножения, выходы которого соединены с первыми входами первого сумматора, первые выходы первого блока деления подключены к первым выходам блока вычитания, введены аналого-цифровой преобразователь, счетчик импульсов счетчик числа измерений, счетчики из меренных значений, первьй и второй блоки- памяти, второй блок умножения второй сумматор, второй блок деления, блок согласования, причем первый выход блока управления подключен к первому входу аналого-цифрового преобразователя, блока согласования и к первому входу счетчика импульсов, второй выход - к первому входу счетчика числа измерений, третий выход - к первому входу второ го блока памяти, четвертый выход к второму входу счетчика числа измерений, к первым входам счетчиков измеренных значений и к второму входу второго блока памяти, пятый выход - к первому входу первого .блока памяти, первый вход - к пер1334 вому входу второго блока деления, а второй вход - к первому выходу счетчика числа измерений и первому входу блока индикации, а третий вход - к выходу блока сравнения, второму входу блока индикации, первый выход аналого-цифрового преобразователя соединен с вторым входом счетчика импульсов, второй выход с третьим входом счетчика импулЪсов и третьим входом счетчика числа измерений, второй вьпсод которого соединен с первыми входами первого и второго блоков деления, третий выход с четвертым входом блока управления и вторым входом блока согласования, третий вход которого соединен с вторым выходом первого блока деления, первый выход - с вторым входом первого блока памяти и с вторыми входами счетчиков измеренных значений, второй выход - с вторым входом первого сумматора, третий выход - с вторым входом первого блока деления, четвертый выход - с вторым входом блока вычитания и третьим входом первого блока памяти, пятый выход - с первым входом блока возведения в степень, шестой выход - с первыми входами второго блока умножения и третьими входами счетчикоь измеренных значений, седьмой выход - с первым входом второго сумматора, а выход - с вторым входом второго блока деления, выходы счетчика импульсов соединены с четвертьми входами счетчиков измеренных значений, выходы которых связаны с первыми входами первого блока умножения, вторые входы которого подключены к выходам первого блока памяти и третьим выходам блока вычитания, выходы которого подключены к вторым входам блока возведения в степень, выходы которого подключены к вторым входам второго блок умножения, третьи входы которого соединены с выходами счетчиков измеренных значений, а выходы - с вторыми входами второго сумматора, выход которого подключен к третьему входу второго блока деления, первый и второй выходы которого соединены соответственно с первым и вторым входами блока сравнения, третий вход которого подключен к выходу второго блока памяти, а выход первого сумматора подключен к третьему входу первого блока деления, первый выход которого подключен к третьему входу блока индикации. На достоверность результатов, полученных при прогнозировании технического состояния объектов диагностирования,оказывают влияние множество внешних и внутренних факторов. К ним относятся помехи, возникающие в объекте, погрешности измерительных цепей и оператора, влияние различного рода случайных воздействий. Для того, чтобы повысить точность прогнозирования состояния технических объек тов и достоверность принятия решения необходимо провести многократные измерения прогнозируемых параметров. В ходе прогнозирования невозможно получить точное совпадение теоретически рассчитанной величины прогнозирования с практически полу.ченноД величиной, поэтому вполне зако номерным является выделения области значений прогнозируемого параметра, в которой он будет находиться с задан ной вероятностью. Вероятность откло нения прогнозируемого параметра от своего среднего значения на величину Таким образом, чем больше относительное отклонение (меньше 6 ) (3 , тем с большей вероятностью можно утверждать, что интервал t f будет содержать рассматриваемую величину. Из формулы (2) видно, что среднеквадратическое отклонение уменьшается с ростом числа измерений, велич на среднеквадратического отклонения измеряемого параметра зависит от раз броса его значений. Для того, чтобы обеспечить требуемую достоверность прогнозирования необходимо, исход из таблицы выполнить условие ПаАСледовательно, необходимо провест такое количество измерений гнозируемого параметра, при котором Практически, для каждого прогнозируемого параметра, учитывая веыраженная через функцию Лаплает вид )2Ф(е/б1-2Фи), d) - измеренное значение прогнозируемого параметра; X - среднее значение (математическое ожидание) прогнозируемого параметё) - среднеквадратическое отклонение параметра |f2;(r-.i п - число измерений, гп; - число, определяющее появление значений соответствующих х- в результате проведения п измерений . блице приведены значения достовероятности Рд ( 6 х ) относительного отсимости от ия. личины возможных случайных воздействий, можно установить необходимое количество измepeнийN .,лежащее в пределах N iN , N mm треВ то1л Если количество Измерений обеспечивает выполнение условия 6 ъо полученное значение прогнозируемого параметра следует считать удовлетворяющим требуемой досто;верности и на этом закончить его измерение. На фиг.1 представлена блок-схема устройства; на фиг.2 - схема счетчика импульсов; на фиг.З - схема счетчика измеренных значений; на фиг.4 схема счетчика числа измерений; на фиг.З - схема первого блока суммирования j на фиг.6 - схема первого блока умножения; на фиг.7 - схема первого блока деления; на фиг. 8схема регистра остатка первого блока деления; на фиг.9 - схема узла коммутации первого блока деления -J на фиг.10 - схема местного узла управления первого блока деления} на фиг.11 - схема блока согласования-, на фиг. 12 - схема блока управления, на фиг. 13 схема узла пуска блока управления. Устройство содержит (фиг.1) аналого-цифровой преобразователь 1, счетчик 2 импульсов, счетчик 3 изме ренных значений, первый 4 блок умно жения, первый 5 блок суммирования, первый 6 блок памяти, первый 7 блок деления, блок 8 вычитания, блок 9 возведения в степень, второй блок 1 умножения, второй сумматор 11, второй блок 12 деления, блок 13 сравне ния, второй блок 14 памяти, блок 15 индикации, счетчик 16 числа измерений, блок 17 управления и.блок 18 согласования с выходами 19-25. . Счетчик 2 импульсов (фиг.2) содержит триггеры 26, элементы И 27, триггеры 28,элемент ИЛИ 29, элемент И 30 с одним инверсным входом и элемент И 31. Счетчик 3 измеренных значений (фиг.З) содержит триггеры 32 и элементы И 33 и 34. Счетчик 16 числа измерений (фиг.4) содержит триггеры 35, элементы И 36 и 37, элемент ИЛИ 38, триггеры 39 и 40 и элемент И 41. Первый сумматор (фиг.5) содержит двоичный сумматор 42. Первьш блок 4 умножения (фиг.6) держит двоичный полусумматор 43, дв ичный сумматор 44 и сумматор 45. Первый блок 7 деления (фиг.7) со жит регистр 46 остатка, регистр 47 лителя, регистр 48 частного, первый 49 и второй 50 узлы коммутации, сум матор -51, местный узел 52 управлени линии 53-57 задержки, элементы ИЛИ 58-61 и элемент И 62. Регистр 46 остатка (фиг.8) содер жит элемент И 63, триггер 64 и элемент И 65. Первый узел 49 коммутации (фиг.9 содержит элемент И 66, элемент И 67 с одним инверсным входом и элемент ИЛИ 68. Местньм узел 52 управления (фиг. содержит элемент И 69 с одним инвер ным входом, элемент И 70, элемент И 71 с одним инверсным входом, триг геры 72 и 73, элемент И 74 и линию 75 задержки.. Блок 18 согласования (фиг.11) содержит элементы И 76-78, триггеры 78-86 элементы И 87, элементы И 88 с одним инверсным входом и генератор 89 импульсов. Блок 17 управления (фиг.12) содержит узел 90 пуска, узел 91 хранения программы. Узел 90 пуска (фиг.13) содержит элемент И 92, элемент И 93 с одним инверсным входом, элемент И 94, элементы ИЛИ 95-97, триггер 98, реле 99 с первым 100 и вторым 101 контактами, переключатель 102 Пуск. Блок 17 (фиг.12) содержит также генератор 103 импульсов. Счетчик 2 имеет входы 104 и 105, счетчик 3 - входы 106-109, счетчик 16 входы 110-112 и выходы 113-115, сумматор 5 - входы 116 и 117, блок 4 входы 118 и 119, блок 7 - входы 120122 и выходы 123 и 124, блок 17 - вхо- ды 125-128 и выходы 129-133, блок 8входы 134-136 и выход 137, блок 6 входы 138-140 и выход 141, блок 9 входы 142 и 143, блок 10 - входы 144-146, сумматор 11 - входы 147 и 148, блок 12 - входы 149-151 и выходы 152 и 153, блок 13 - входы 154-156 и выход 157, блок 14 - входы 158 и 159 и выход 160, блок 18 - входы 161 163 и выход 164, регистр 46 - выходы 165-168 и выход 169, узел 49 входы - 170-172 и выход 173, узел 52входы 174 и 175 и выходы 176-179, регистр 46 - выход 180, узел 90 вход 181 и блок 15 - входы 182-184. - Первый выход аналого-цифрового преобразователя 1 соединен с вторым 104 входом счетчика 2 импульсов, втоРОЙ выход - с третьим входом счетчика 2 импульсов и третьим 112 входом счетчика 16 числа измерений, а первый вход - с первым 129 выходом блока 17 управления. Первый 103 вход счетчика 2 импульсов подключен к первому 129 выходу блока 17 управления, а выходы соединены с четвертыми 109 входами счетчиков 3 измеренных значений. Первые 106 входы счетчиков 3 измеренных значений подключены к четвертому 132 выходу блока 117 управления, вторые 107 входы - к первому 164 выходу блока 18 согласования, третьи 108 входы - к шестому 23 выходу блока 18 согласования, а выходы - к первым 118 входам первого 4 блока умножения и третьим 145 входам второго 10 блока умножения. Вто рые 119 входы первого А блока умножения соединены с выходами 141 первого блока памяти, а выходы - с пер выми 116 входами первого 5 сумматора, второй 117 вход которого подключен к второму 19 выходу блока 18 согласования. Выход первого 5 сумматора соединен с третьим 122 входом первого 7 блока деления. Первый 138 вход первого блока памяти подключен к пятому 133 выходу блока 17управления, второй 139 вход - к первому 164 выходу блока 18 согласо вания, третий 140 вход - к четвертому 21 выходу блока 18 согласования, а выходы 141 - к третьим, 136 входам блока 8 вычитания. Первый 120 вход первого 7 блока деления соединен с вторым 114 выходом счетчика 16 числа измерений, второй 121 вход - с третьим 20 выходом блока 18 согласования, первый 123 выход - с первыми 134 входами блока 8 вычитания и третьим 184 вхо дом блока 15 индикации,второй 124 выход - с третьим 163 входом блока 18согласования. Второй 135 вход блока 8 вычитания подключен к четвертому 21 выходу блока 18 согласования, а выходы 137 - с вторыми 143 входами блока 9 возведения в степень. Первый вход 142 блока 9 возведения в степень соединен с пятым 22 выходом блока 18 согласования, а выходы - с вторыми 145 входами второго блока 10 умножения. Первые 144 входы второго 10 блока умножения подключены к шестому 23 выходу блока 18 согласования, а выходы - к вторым 148 входам второго 11 сумматора. Первый 147 вход второго 11 сумматора соединен с седьмым 24 выходом блока 18 согласования, выход - с третьим 151 входом второго 12 блока деления Первый 149 вход второго 12 блока деления подключен к второму 11 выходу счетчика 16 числа измерений, второй .вход 150 - к восьмому 25 вых ду блока 18 согласования, первьш вы ход 152 - к первому 154 входу блока 13 сравнения и к первому 125 вход блока 17 управления, второй 153-вых к второму 155 входу блока 13 сравне ния. Третий 156 вход блока 13 сравнени соединен с выходом 160 второго 14 бл ка памяти, а выход 157 - с вторьм 183 входом блока 15 индикации и к третьему 127 входу блока 17 управления. Первый 158 вход второго блока 14 памяти подключен к третьему 131 выходу блока 17 управления, второй 159 вход - к четвертому 138 выходу блока 17 управления. Первый 182 вход блока 15 индикации соединен с первым 113 выходом счетчика 16 числа измерений. Первый 110 вход счетчика 16 числа изме- . рений подключен к второму 130 выходу блока 17 управления, второй 111 вход - к четвертому 132 выходу блока 17 управления, первьй 113 выход - с вторьпч 126 входом блока 17 управления, третий 115 выход - к четвертому 128 входу блока 17 управления и к второму 162 входу блока 18 согласования. Первый выход 129 блока 17 управления соединен с первым 161 входом блока 18 согласования. Счетчик 2 импульсов предназначен для накопления импульсов, поступающих на его второй 104 вход с первого выхода аналого-цифрового преобразователя 1. Число накопленных импульсов будет пропорционально величине входного сигнала. Триггеры 26 в счетчике 2 импульсов предназначены для подсчета импульсов, соответствующих детерминированной величине измеряемого сигнала. Триггеры 28 предназначены для накопления импульсов, появляющихся в результате влияния на измеряемый параметр случайных воздействий. С помощью логических элементов 29-31 обеспечивается появление .импульса только на 1 -м ( i 1, п ) выходе счетчика 2 импульсов, соответствующем i-и величине измеряемого сигнала. Второй 104 вход счетчика 2 импульсов является счетным входом. При подаче на третий 105 вход импульса Окончание преобразования, поступающего с второго выхода аналогоцифрового преобразователя, производится выдача записанного результата. Первьй 103 вход счетчика 2 импульсов рредназначен для установки триггеров 26 и 28 в исходное состояние по команде, поступающей с первого 129 выхода блока 17 управления. Счетчики 3 измеренных значений предназначены для подсчета числа импульсов, поступающих на их входы с 111 соответствующих выходов счетчика 2 импульсов. Их количество определяет ся количеством выходов счетчика 2 импульсов. Блок-схема одного из них предста лена на фиг.З. Четвертый 109 вход счетчика 3 измеренных значений является счетным входом, он подключен к i-му выходу счетчика 2 импульсов. Первый 106 вход предназначен для перевода триггеров 32 в нулевое сос тояние по команде с блока 17 управления. Записанный результат со счетчика 3 измеренных значений вьщается при поступлении на его второй 107 и третий 108 входы разрешающих команд от блока 18 согласования. Счетчик 16 числа измерений предназначен для подсчета числа проведе ных измерений входного сигнала, сра нения этого числа с пределами измерений. Nj. , N| , заданных блоком 17 управления. При этом в случае на блок 18 согласования выдается команда Запрет, а Работа при Блок-схема счетчика 16 числа измерений представлена на фиг Он представляет собой двоичный суммирующий счетчик. Появление единичного сигнала на выходе триггера 39 соответствует достижению числа измерений N N появление единич ного сигнала на выходе триггера 40 соответствует достижению.числа изме рений N-N . Сравнение текущего числа измерений с заданными пределами происходи следующим образом. При достижении числа измерений N N j, соответству щая схема И 37 выдает сигнал, котор переводит триггер 39 в единичное со тояние, т.е. с выхода триггера 39 снимается сигнал, свидетельствующий, что . При достижении триггер 40 переходит в единичное состояние, появление сигнала на его выходе соответствует достижеТретий 112.вход счетнию N N чика 16 измерений является счетным входом и подсоединяется к второму в ходу аналого-цифрового преобразователя 1. Первый 110 вход служит для задания пределов измерений N„,( Второй 111 вход служит для установк триггеров 35, 39 и 40 в нулевое сос 3 12 поступающей с блотояние по команде, ка 17 управления. Первый 6 блок памяти предназначен для хранения и выдачи на вторые входы блока 4 умножения и блока 8 вычитания нормированных значений, соответствующих величинам измеряемого сигнала, которые могут иметь место при проведении измерений сигнала, искаженного воздействием случайной помехи. Первый блок 5 суммирования представляет собой двоичный сумматор прямого кода, выполненный на двоичных сумматорах и предназначен для проведения поразрядного суммирования результатов, полученных первым блоком 4 умножения. Блок-схема 5 блока суммирования представлена на фиг. 5, где Р; - значение ;i-ro выхода первого м блока умножения. Первый 4 блок умножения предназначен дпя умножения значений соответствующих величин измеряемого СИ1- нала, поступающего с первого блока 6 памяти, на число, соответствующее появлению этих значений в результате проведенных измерений, которое записано в счетчике 3 измеренных значений. Он представляет собой множительное устройство, реализующее матричный алгоритм умножения. Структурная схема множительного устройства для двух пятиразрядных чисел представлена на фиг.6. Первый блок 7.деления производит деление результатов, полученных первым блоком 5 суммирования на число проведенных измерений, записанных в счетчике 16 числа измерений. В результате деления получаем среднее значение измеряемого сигнала. Блок-схема первого блока деления представлена на фиг.7 и 8. В нем реализован алгоритм деления, заключающийся в том, что делитель на каждом шаге вычитается столько раз из делимого, сколько это возможно для получения наименьшего положительного остатка. Цифры частного получаются последовательно, начиная со стороны старшего разряда путем вычитания делителя из делимого на первом шаге, а затем делителя из полученного остатка. Если получен положительньш остаток, то цифра частного равно единице, если остаток отрицательный, то цифра частного равна нулю, при этом восстанавливается пред1адущий положительный остаток. В случае положительног остатка дл.я получения следующей циф ры частного последний остаток сдвигается влево на один разряд (либо делитель вправо на один разряд) и и него вычитается делитель и т.д. В с чае отрицательного остатка восстанавливается предыдущий положительны остаток прибавлением к отрицательно му остатку делителя и восстановленный остаток сдвигается влево (либо сдвигается делитель вправо на один разряд) и из него вычитается делитель. Регистр 46 остатка предназначен для оперативного запоминания и воспроизведения п-разрядного числа, поступающего с сумматора 51. Его бток-схема представлена на фиг.8. Перед вводом в регистр 46 остатка двоичного числа, триггеры 64 уста навливаются в нулевое положение одно временной подачей импульсов на их вт рые 166 входы. Двоичные числа подают ся на первые 165 входы элементов И 63, на вторые входы которых подается импульс записи.Выходные импульсы с элементов И 63 устанавливают триггеры 64 в единичное состояние. Считывание записанного в регистр числа происходит в момент поступления импульса считывания на элемент И 65, которое через второй узел 50 коммутации поступает на вход сумматора 51. Регистр 47 делителя представляет собой сдвигающий регистр, предназначенный для оперативного запоминания и воспроизведения п-разря ного числа, поступающего с блока 16 причем, в связи с тем, что делитель представляется отрицательным числом то это число записывается в дополни тельном коде. Первый узел-49 коммут ции предназначен для подключения к первому входу сумматора 51 п-раз рядного числа, выраженного в прямом коде., поступающего с блока 16 и в дополнительном коде, поступающем с регистра 47 делителя. В прямом коде п-рязрядное число представлено поло жителЪным, в дополнительном коде отрицательным. Положительное значение п-разрядного числа необходимо для восстановления положительнбго о татка деления. Структурная схема первого 49 узла коммутации представ лена на фиг.9, Для подключения к t 3 входу сумматора 51 п-разрядного числа, выраженного в прямом коде, на вторые входы элементов И 66 подается команда с местного 52 узла управления. Второй 50 узел коммутации предназначен для подключения на первом такте деления к второму входу сумматора 51 п -разрядного числа, записанного в блоке 5,а на следующих тактах подключается п-разрядное число, считываемое с регистра 46 остатка. Второй узел 50 коммутации выполнен аналогично первому 49. Сумматор 51 является двоичным сумматором дополнительного кода и производит операцию вычитания делителя из делимого и операцию сложения, делителя с остатком при восстановлении положительного остатка. -Местный 52 узел управления предназначен для управления работой первого 7 блока деления и реализует описанньй выше алгоритм деления. Структурная схема местного узла 52 управления представлена на фиг.10. Единица знакового разряда регистра 46 остатка соответствует отрицательному результату суммирования узла 51, ноль соответствует положителггному остатку. Сигнал на выходе 1/7 элемента И 69 появляется тогда, когда остаток суммирования блоком 51 положительный, в этом случае знаковый разряд в регистре 46 равен нулю. Эта информация поступает на элементы И 69 и 70. При этом в регистр 48 частного с элемента И 71 записывается единица. Появление сигналов на выходе 178 элемента И 70 соответствует получению отрицательного octaTxa, в регистр 48 частного с элемента И 71 записывается ноль. Появление сигнала на выходе элемента И 70 два раза подряд соответствует получению наименьшего положительного остатка, при этом на выходе 176 триггера 73 появится сигнал Конец деления, который поступает на элемент И 77 блока 18. Первый 7 блок деления работает следующим образом. С приходом сигнала Разделить от блока 18 согласования на второй 121 вход первого блока 7 деления происходит установка в нулевое состояние регистра 47 делителя, регистра 46 остатка, регистра 48 частного. Через время Т , определяемое линией 54 задержки, подается команда на считывание п -разрядного числа, содержащегося в блоке 16,и за пись его в регистр 47 делителя, в до полнительном коде. Через время f2 , определяемое линией задержки 53, под ется команда на считывание п -разря ного числа, хранимого в блоке 5 и на считывание п-разрядного числа, записанного в регистре 47 делителя. Одновременно подается команда на вто рой узел 50 коммутации, который подключает выход блока 5 к первому входу сумматора 51, на вторые входы сумматора 51 через первый блок 49 ко Мутации подключается выход регистра 47 делителя. Сумматор 51 производит вычитание п-разрядного числа поступающего с регистра 4/ делителя из г -разрядного числа, соответствую щего начальному значению Делимого, поступающего с блока 5. Через время Т , равное времени работы суммато ра 51, определяемое линией задержки 57, на регистр 46 остатка подается команда на запись результата вы читания. Если получен положительный результат (знаковый разряд регистра 46 остатка равен нулю), то в регистр 48 записывается единица.На вто ром выходе местного узла 52 управления появится сигнал, который производит сдвиг регистра 47 делителя впр во. Этотсигнал, пройдя злемент ИЛИ 58, обеспечивает считывание информации, записанной в регистр 46 остатка-, которая через второй узел 50 коммутации поступает на первый вход сумматора 51. Через время задер ки обеспечиваемое лийией 56 за держки, подается команда на установку регистра 46 остатка в нулевое состояние. Этот же сигнал, через эле менты РШИ 60-62 обеспечивает считывание п -разрядного числа, записан ного в регистре47 делителя. Сумматор 51 производит вычитание делителя из полученного остатка. Если получен положительный остаток, то блок 7 деления работает аналогичным образом. Если получен отрицательный остаток (знаковый разряд регистра 46 остатка равен единице), то в регистр 48 частного записывается ноль, а на третьем выходе местного узла 52 управления появится сигнал, который обеспечивает считывание информации, хранимой в регистре 46 остатка, и передачу ей на первый вход сумматора 51.Через время задержки TJ , обеспеченное линией 55 задержки, подается команда на первый блок 49 коммутации, который подключает ti -разрядное число, записанное в блоке 16, к второму входу сумматора 51. Сумматор 51 производит сложение значений п-разрядных чисел, поступающих на его входы (восстанавливается положительный остаток), при этом iB регистр 48 . .частного единица не записывается, так -как нет сигнала на выходе элемента И 71, закрытого единичным сигналом, снимаемым с единичного выхода триггера 72. Далее устройство работает по алгоритму, соответствующему получению положительного остатка. Если отрицательный остаток получен два раза подряд (получен наименьший остаток вычитания), то на четвертом выходе (единичный выход триггера 73) местного узла 52 управления появится сигнал Конец деления, который поступает на блок 18 согласования, и через линию 75 задержки устанавливает триггеры 72 и 73 в исходное состояние. Блок 8 вычитания представляет собой двоичный сумматор дополнительного кода и предназначен для вычитания из нормированных значений п-разрядных чисел, поступающих с первого блока 6 памяти, значения х„ , полученного первым блоком 7 деления. В результате этого получаем нормированные значения отклонений (х - х ). Блок 9 возведения в степень возводит результаты вычислений блрка 8 в квадрат. Он представляет собой множительное устройство. По своему схемному решению он аналогичен блоку 4 умножения. Второй 10 блок умножения предназначен для умножения квадратов нормированных значений (х - х ) на число, соответствующее появлению этих отклонений в результате проведенных измерений и записанное в счетчике 3 измеренных значений. По своему схемному решению он аналогичен блоку 4 умножения. Второй 11 блок суммирования предназначен для суммирования результато, полученных блоком 10. По своему схемному решению он аналогичен первому 5 блоку суммирования. 1711 Второй 12 блок деления производит деление результата, полученного вторым 11 блоком суммирования, на число проведенных измерений, в результате получаем значение ;(г Второй 14 блок памяти предназначен для записи и хранения п-разрядного числа, заданного блоком 17 управления, которое соответствуетб и меряемого параметра. Блок 13 сравнения производит срав нение значения полученного в результате вычислении, со значением 6j., записанного во втором блоке 14 памяти. Блок 15 индикации осуществляет индикацию и печать среднего значения измеряемого сигнала, удовлетворяющего заданной точности и достовер ности. Блок 18 согласования предназначен для обеспечения согласованной работы блоков устройства. Он представляет собой двоичный суммирующий счетчик, его блок-схема представлен на фиг.11. Блок 18 согласования раб тает следующим образом. С приходом команды, поступающей на второй вход 162 блока (на первый вход триггера 78) от счетчика 16 числа измерен триггер 78 устанавливается в единичное состояние, при зтом элемент И 76 открывается и импульсы с генера тора 89 импульсов начинают поступать через элемент И 76 на вход триггера 79. С приходом первого импульса триггер 79 установливается в единичное состояние. С прямого выхода триг гера 79 снимается коианда с выхода 164 на выдачу информации первым блоком 6 памяти и информации, записанной счетчиком. 3 измеренных значений С приходом второго импульса от генератора 89 импульсов переходит в единичное состояние триггер 80. При зтом запрещается вьщача сигнала снимаемого с прямого выхода триггера 79 (закрыт элемент И 88),и выдается команда на второй 19 выход. С приходом третьего импульса от генератора 89 импульсов в единичное состояние переходит триггер 81, кото рый запрещает вьщачу команды, снимаемой с прямого выхода триггера 80 и выдает команду на выход 20 для 3 пуска блока 7 деления. С приходом импульса Конец деления на вход 163 от блока 7 триггер 82 устанавливается в единичное состояние. С прямого выхода триггера 82 снимается команда, которая поступает на выход 21. С приходом следующих импульсов от генератора 8.9 импульсов поочередно устанавливаются в единичное состояние триггеры 83-86, с прямых выходов которых снимаются команды на пуск соответствующих блоков устройства. Блок 17 управления представлен на фиг.12. В его состав входит узел 90 пуска, представленный на фиг.13. Блок 17 управления работает следующим образом. С включением переключателя 102 Пуск в узле 90 пуска блока 17 управления происходит следующее: срабатывает реле 99 и становится на самоблокировку через свой замкнувшийся контакт lOOj триггер 98 устанавливается в нулевое состояние; на узел 91 хранения программы выдается команда на ввод программы. Узел 91 хранения программы производит засылку исходных данных в блоки 6, 14 и 16 устройства. При задании программы с четвертого выхода узла 91 хранения программы снимается сигнал, который через элемент ИЛИ 97 закрывает элемент И 94 и устанавливает блоки 3,14 и 16 устройства в исходное состояние. По окончании задания программы элемент И 94 открывается и импульсы от генератора 103 импульсов через элементы 93,96 и 94 производят пуск аналого-цифрового преобразователя 1. При этом частота следования импульсов генератора 103 импульсов подобрана таким образом, что аналого-цифровой преобразователь 1 в период следования одного тактового импульса успевает преобразовать входной сигнал. При достижении числа измерений . с выхода счетчик-а 16 числа измерений на вторые входы элементов И 92 и 93 подается сигнал, KOTopbtfi закрывает элемент И 93 и открывает элемент И 92. При этом команда на пуск аналого-цифрового преобразователя 1 подается импульсом Конец деления, снимаемо- го с первого выхода блока 12 при окончании цикла работы устройства

и поступающего на вход 125. Пуск аналого-цифрового преобразователя прекращается при поступлении сигнала на вход 128, вырабатываемого при условииN Nj , или при наличии) сигнала на входе 127 от блока 13 сравнения. Этот сигнал через элемент ИЛИ 95 переводит триггер 98 в единичное.состояние. Сигнал с прямого выхода триггера 98 через элемент ИЛИ 97 закрывает элемент И 94, При этом сигналом, снимаемым с выхода 132, блоки 3,.6 и 14 устанавливаются в исходное состояние. Для измерения следующего параметра повторно включается переключатель 102 Пуск, при этом узел 91 хранения программы вводит в блоки 6, 14 и 16 новые исходные данные, характеризующие следующий измеряемый параметр.

Устройство работает следующим образом.

С нажатием переключателя 102 Пуск в блоке 17 управления начинается ввод программы, при этом в счетчик 16 числа измерений вводятся пределы измерений N. , f , во второй блок 14 памяти задается значение 6 . в первый блок 6 памяти задаются нормированные значения п-разрядных чисел. По окончании задания программы блок 17 управления выдает команду на пуск аналого-цифрового преобразователя 1 с частотой генератора 103 импульсов. При этом импульсы, полученные в результате преобразования, поступают на вход 104 счетчика 2 импульсор. Импульс Конец преобразования с аналого-цифрового преобразователя 1 поступает на второй 105 вход счетчика 2 импульсов, обеспечивая появление импульса на его

i-M выходе, соответствующий . величине измеряемого сигнала, который записывается соответствующим счетчиком 3 измеряемых значений. Импульс Конец преобразований с аналого-цифрового преобразователя 1 также поступает на вход 112 счетчика 16 числа измерений. С появлением сигнала на первом 129 выходе блока 17 управления, поступающего на первый 103 вход счетчика 2 импульсов, его триггеры 26 и 28 устанавливаются в нулевое состо5сние, на счетный вход счетчика 2 импульсов начинают поступать импульсы. При достижении числа измерений , на третьем 115 выходе счетчика 16 измеренных значений появляется сигнал, который, поступая на второй 162 вход блока 18 согласования, обеспечивает

его запуск. Сигнал ,,, поступает также на четвертый 128 вход блока 17 управления, с его рриходом запуск аналого-цифрового преобразователя 1 производится по окончании цикла работы устройства. Блок i8 согласования выдает управляющие команды, которые обеспечивают согласованную работу блоков устройства. Появление сигнала на первом 164 выходе блока 18 согласования обеспечивает выдачу информации первым 6 блоком памяти и счетчиками 6 измеренных значений. Первый 4 блок умножения производит умножение нормирова ных значений п -разрядных чисел, поступающих с первого блока 6 памяти, на число, соответствующее появлению этих значений, полученное в результате измерений и записанное в счетчиках 3 измеренных значений. Появление сигнала на втором 19 выходе блока согласования 18 обеспечивает пуск первого 5 блока суммирования. Первый 5 блок суммирования производит поразрядное суммирование результатов, полученных первым 4 блоком умножения. Появление сигнала на третьем 20 выходе блока 18 согласования обеспечивает пуск блока 7 деления. Первый 7 блок деления производит деление результатов, полученных первым 5 блоком суммирования, на число проведенных измерений, записанное в счетчике 16 числа измерений. В результате деления получаем среднее значение измеряемого сигнала. Импульс Конец деления, снимаемый с второго 124 выхода первого 7 блока деления, поступает на вход 163, ас него на элемент И 77,

блока 18 согласования, при этом триггер 82 переходит в единичное состояние. Появление сигнала на прямом

выходе триггера 82 обеспечивает выдачу управляющей команды блокам 6 и 7. Блок 8 вычитания производит вычитание из нормированных значений п -разрядных чисел, поступающих с первого 6 блока памяти, значения х , полученного первым 7 блоком деления. В результате получаем нормированные значения отклонений ( х. - х ) .. Появление сигнала на пятом выходе 22 21 блока 18 обеспечивает пуск блока 9 возведения в степень, который возводит в квадрат значение () . Сиг мал, снимаег-1ый с 6-го выхода 23 бло ка 18, обеспечивает выдачу информаци записанной в счетчиках 3 измеренных значений, и пуск второго 10 блока умножения. Блок 10 производит умноже ние квадратов нормированных значекий отклонений на число, соответствующее появлению этих отклонений, которое записано в счетчиках 3 измеренных значений. Появление сигнала на седьмом 24 выходе блока 18 обеспе чивает пуск второго 11 блока суммиро вания, который производит суммирование результатов, полученных блоком 10. Появление сигнала на восьмом 25 выходе блока 18 согласования обеспечивает пуск второго 12 блока деления, который производит деление результата, полученного блоком 11 на число проведенных измерений, запи санное в счетчике 16 числа измерений. В результате получаем Импульс Конец деления с второг 153 выхода второго блока 12 деления производит пуск блока 13 сравнения. Блок 13 сравнения производитсравне 3 ние результата , Полученного блоком 12 с .(зчА , поступающего с второго блока 14 памяти. Если значение , то блоком 17 управления выдается команда на пуск аналого-цифрового преобразователя 1. При достижении равенства 6 JCIA блок 13 сравнения выдает команду: на блок 15 индикации, который производит печать полученного значения х ; на блок 17 управленияJ который прекращает вьщавать команды на пуск аналого-цифрового преобразователя 1 и устанавливает блоки 6, 14 и 16 в исходное состояние. Блок 17 управления выдает аналогичную команду при достижении равенства , при этом блок 15 индикации печатает зна чение с признаком неточен Преимуществом предлагаемого устройства перед известным является то, то оно позволяв определить минимально необходимое число многократных измерений параметра, удовлетворяющих заданной то.чности, т.е. уменьшить временные затраты, связанные с этой целью, а также повысить точность прогнозирования состояний технических объектов за счет получения точных значений прогнозируемых параметров.

1ЧЪ

/37

2fГ35 5

/т...

. /Ttj

2ij

/36

123

V

/5

5 Н7

№f

/fk ГГ 7

Г/6

Пб

/39

Ш

V V

Ы

/f3

10

ж

23

23-

T/Pg/g 7 gg

.W5

mm,

%

WWZJ

it

/6/

/5

m

фффф

2Z Л Г« 2

75

f

f

W5.

W

m

/501

147 П

I

/5 Ш

/5Г

ff. /f

Ю

M

//5.

IP

/46

/55

183

/5

1571

15

0

/ч

/

Г5(

т /60

V

л

158

159

liTl

т

//;

16

113

т

т

Ш

130

/3

17

ТЖ

Щ

/

/25

мг./

Фиг.5

ФигМ

ffi

регистра

JZO

я

M

7

m

. /7(C7

/

5

Выдача

или

61

Ч

53

57

$

5k ;67 №в т Результат.

ИЛИ 60

им

56

59

/

ИЛИ

56

f Знанобь, разряд

Фи1.7

Фиг. 8

Фиг. 10

ц

1 f

77

яет

tp

It;

L «7 -t-

ttt3Й

linVi tr

г

Г

DFT

«7

-J

Cn

IS

г

Н Hfnin,

ФигМ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для прогнозирования параметрической надежности узлов радиоэлектронной аппаратуры | 1975 |

|

SU525106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для прогнозирования надежности | 1978 |

|

SU746350A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-23—Публикация

1982-06-18—Подача