Изобретение относится к вычислитель ной и измерительной технике. Известен усилитель выборки н запоми. нания, соаержаший цифференииальный уев- лктвПз, промежуточный каскаа, выходной каскао, шины питания и разрешение считывания, инвертор, псвторитета герератор тока и разаелительные э;Бменты 11. Неоостаток данного усилителя - низкая течность и малое время памяти. , Нокболее близким по -технической cyijiности к предлагаемому является усилитель, содержащий предварительный каскад усиления, выход которого через первый ключ соединен с накопительным конденсатором и входами второго и третьего ключа, выходной каскад, вход которого соединен с выходом второго ключа, а выход подключен к входу аналого-цифрового преобразователя (АЦП ) и два триггера, выход первого из ксугорых соединен с входами управшния первого н второго ключей, а выход второго трнгге- ра соединен с входом управления третьего ключа . 2.. Недостатком известного усилвтеля я&- ляется н оэможность проверки и коррекшш его параметров, что ведет к уменьшению точности преобразования. Цель изобретения - повышение точвостк кштроля и коррекции пефаметров усиления. Поставлевная цель достигается тем, что в усиштель, содержащий предварительный каскад , вход которого соещгаеи с входной шиной, а вьвсоц: поокл|С1Чен через первый ключ к накопительному конденсатору и входам второго в третьего ключей, вькодной каскад jrceлевия, вход которого соединен с выходом второго ключа, два триггера, первые входы которых соединены между и с первой шиной управляющего сигнала, выходы первого Tpiirrepa подключены к входам управления первого в второго ключей , рторой вход )эторого триггера соединен с второй шиной сигеала уп39

равления, а его выхоц поцключен к ьхоцу управления третьего ключа, выход которого соединен с шиной, а также аналого-цифровой преобразователь, введены дополнительно два ключа, нуль-орган, счет чик, делитель частоты с переменным кра} 41ткентом деления и генератор импульсов, выход которого через делитель частоты с переменным коэф(||1циентом оеления соединен с вторым входом первого триггера, а через первый дополнительный ключ - с входом счетчика, вход управления первого дополнительного ключа соединен с выходом нуль-органа, один вход которого соединен с входной шиной и первым входом второго дополнительного ключа, второй вход которого соединен с выходом выхооного каскада усиления, а выход подключен ко входу аналого-цифрового преобразователя и второму входу нуль-органа,

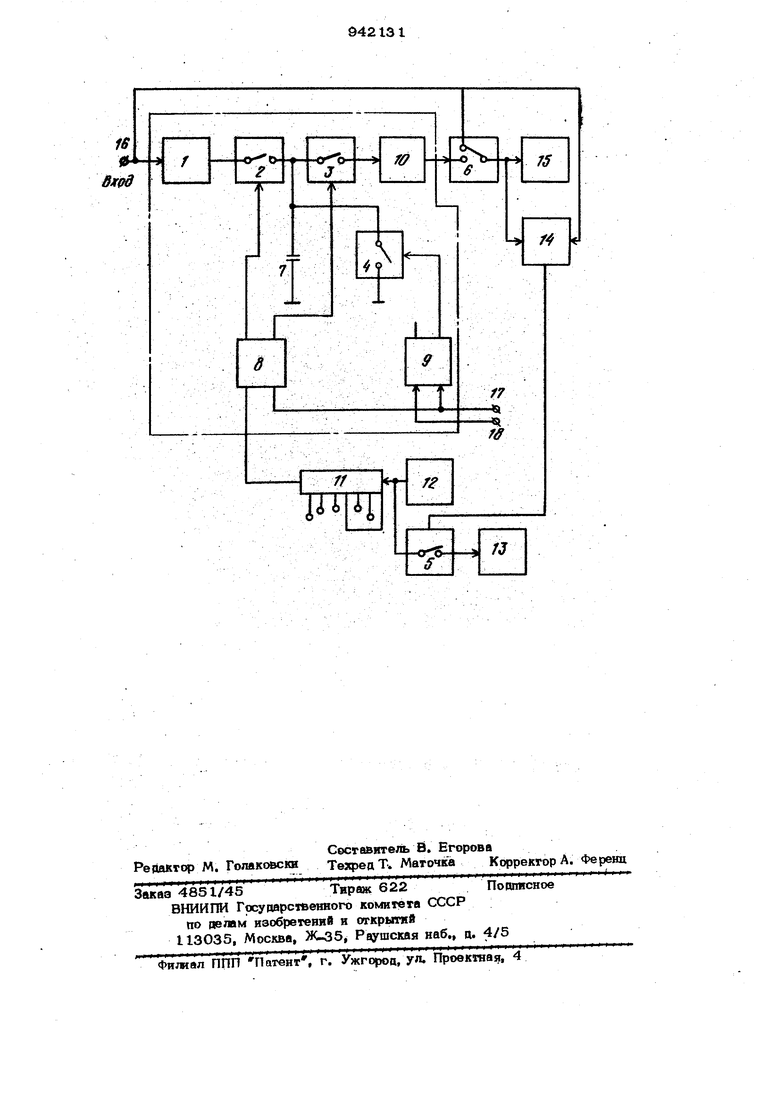

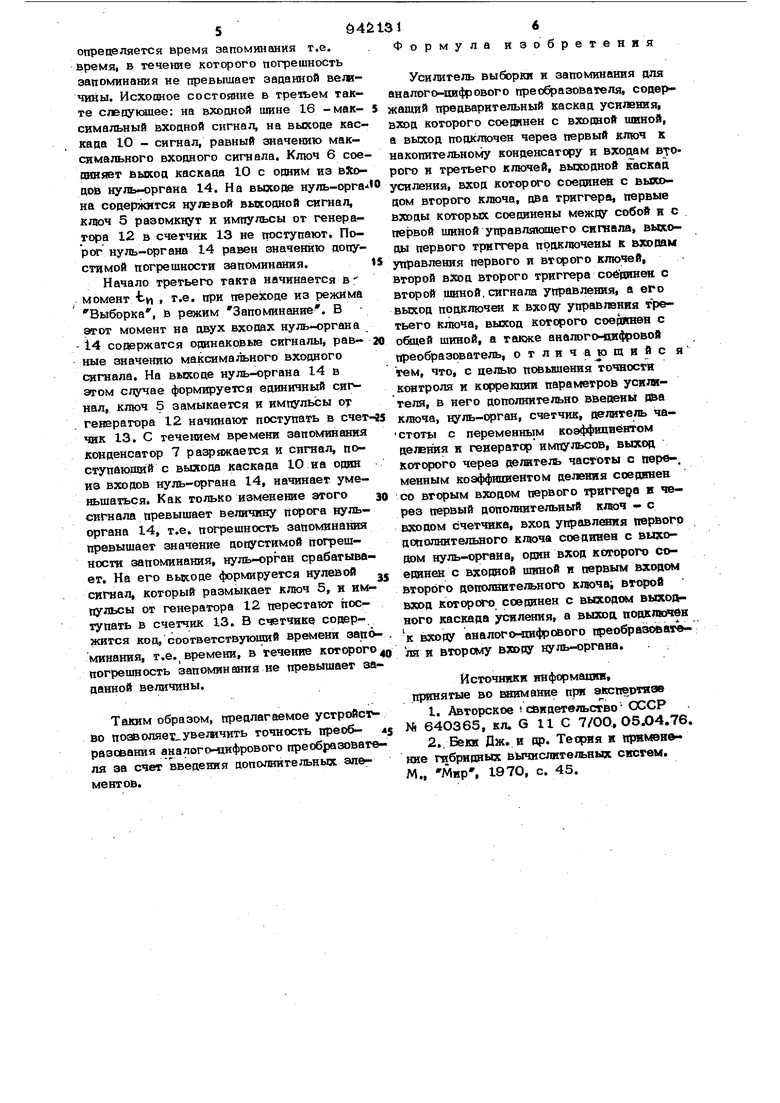

На чертеже приведена структурная схема усилителя.

Усилитель выборки и запоминания содержит предварительный каскад I усиления, ключи 2-6, накопительный кшденсатор 7, триггеры 8 и 9, выходной каскад Ш усиления, делитель 11 частоты с переменным коэффициентом деления, генератор 12 импульсов, счетчик 13 и нуль-фган 14, также аналого-да14ровой преобразователь 15. Преобразуемый сигнал подается на входную ишну 16, а на шины 17 и 18 подаются сигналы управления.

Принцип работы усилителя заключается в следующем.

Устройство работает в три такта. В первом такте вход преобразователя 15 через ключ 6 подключен непосредственно ко входной шнне 16. Максимальный входной сигнал преобразуется в преобразователе 15 в цифровой код. На это(Л первый такт работы устройства заканчивается.

ч..

Исходное состояние во втором такте следукяцее Вход преобразсйауеля 15 отключен от вяйдной шины 16 и подключен через ключ 6 к выходу каскада 10. Триггер 8 и триггер 9 находятся в единичном состоянии. В йтом случае ключ 2 разомкнут, а ключи 3 и 4 замыкаются. Накопительный конденсатор 7 через ключ 4 заземлен, а через ключ 3, каскад Ю и ключ 6 подключен ко входу преобразователя 15. Коэффициент деления дедателя II, выбираемый с помощью какого либо переключателя (ие показан) равен минимальному значению. Импульсы от генератора 12 в делитель II не поступают. На выходе иуль-органа 14 в пер1314

вом и во Втором тактах сод жится ну/к- вой сигнал, ключ 5 разомкнут, импульсы от генератора 12 в счетчик 13 не поступают.

В момент to на один из управляющих входов триггера 8 поступает сигнал Выборка, В этом спучйе оба триггера 8 и

9переходят из единичного состояния в нулевое, при этом ключ 2 замыкается, а ключи 3 и 4 размыкаются. Максимальный входной сигнал через каскад 1 и ключ 2 заряжает конденсатор 7. Импульсы от генератора 12 поступают в делитель. В мо ..) в соответствии с заданным коэффициентом деления на другом входе, триггера 8 появляется сигнал Запоминание и переводит этот триггер в единичное состояние. При этом ключ 2 размыкается, а ключ 3 замыкается. Напряжение на конденсаторе 7 через ключ 3, каскад

10и ключ 6 поступает на вход преобразователя 15. После .окончания процесса аналого-аи4 ового преобразования про- исходит сравнение цнфровьсс кодов, попученйьос в первом и во втором тактах. Ее- ПК погрешность выборки вешка, значит время выборки должно быть увеличено.

В этом случае устройство переводятся в исхошое состояние, для чего на другой управляюпшй вход триггера 9 подается сигнал Разряд, и переводит его в единичное состояние. В этом случае ключ 4 замыка1ется и через него конденсатор 7 разряжается. Затем коэффициент деления делителя II увеличивается на единицу по отношению к предыдущему значению, что соответствует времени выборки -to- -Ьу, после чего процесс работы во втором такте повторяется. Бели погрешность выборки опять велика, то этот процесс пов- теч яегся снова, причем время выборки опять увеличивается с помощью изменения коэффициента делания. Такое увеличение времени выборки продолжается до тех пор п{жа насфяжение на ксв1денсаторе 7 достигает Качения максимального входного сигнала. В этом сдучае цифровой кой порченный на первом такте, равен аяфр вому коду, подучэнному на втором такте. Время выборки при достигается такое (х является необходимьлм временем выборки и запоминания. устан авл шаетс я с точностью преобразователя 15 и равно произведению периода следования импульсов генератора 12 импульссв на коэффициент деления делителя 11. На этом заканчивается второй такт работы

После окончания второго такта начинается третий такт работы, на котором

О11редаляется время запоминания т.е. время, в течение которого погрешность запоминания не превышает заданной вешчины. Исходное состояние в третьем такте следующее: на входной шине 16 - максимальный входной сигнал, на выходе каскада 10 - сигнал, равный значению максимального входного сигнала. Ключ 6 соединяет выход каскада 10 с одним из ВУО)дов нуль-органа 14. На выходе Hynb-opra на содержится нушвой выходной сигнал, ключ 5 разомкнут и импульсы от генератора 12 в счетчик 13 не поступают. Порог нуль-органа 14 равен значению допустимой погрешности запоминания.

Начало третьего такта начинается в момент tVI , т.е. при переходе из режима Выборка, в режим Запоминание. В этот момент на двух входах нуль-органа 14 содержатся одинаковые сигналы равные значению максимального входного сигнала. На выходе нуль-органа 14 в этом случае формируется единичный сигнал, ключ 5 замыкается и импульсы от генератора 12 начинают поступать в счетчик 13. С течением времени запоминания конденсатор 7 разряжается и сигнал, поступающий с выхода каскада 10 на ошга из входов нуль-органа 14, начинает уменьшаться. Как только изменеше этого сигнала превышает величину порога нульоргана 14, т.е. погрешность запоминания превышает значение допустимой погрешности запоминания, нуль-орган срабатываег. На его вькоде формируется нулевой сигнал, который размыкает ключ 5, и импульсы от генератора 12 перестают поступать в счегчик 13. В счетчике содержится код, соответствуюишй времени зап& минания, т.е. времени, в течение которого погрешность запо шнания не превышает заданной величины.

Таким образом, предлагаемое устройств во позволяет„увел1чить точность преобразования аналогсмаифрового преобразователя за счет введения дополнительных элементов.

Формула изобретения

Усилитель выборки и запоминания для аналого-цифрового преофазователя, содержащий предварительный $аскад усиления, вход которого соегкнен с входной швной, а выход подключен через первый ключ к накопительному конденсатору и входам второго и третьего ключей, выходной каскад усиления, вход которого соединен с выходом второго ключа, два триггера, первые входы которых соединены между собой и с первой шиной управляющего снгеала, выходы первого триггера подключены к входам управления первого и второго ключей, второй вход второго триггера соёирнен. с второй шиной, сигнала управления, а его выход подключен к входу управления третьего ключа, выход которого соедкнен с общей шиной, а также аналого-цифровой преобразователь, отличающийс я тем, что, с целью повьяиеиия точности контроля и параметров усилителя, в него дополнительно введены пва ключа, нуль-орган, счетчик, даглитель частоты с переменным коэффициентом детстася и генераторимпульсов, выход, котфого через делитель частоты с пере-, менным козффшщеятом деления соединен со вторым входом первого триггера и через первый дополнительный ключ - с входом счетчика, вход управлваия первого дополнительного ключа соединен с выходом нуль-органа, один вход коггорого соединен с входной шиной и первым входом второго дополнительного ключам второй вход которого соединен с выход1м выходного каскада усиления, а выхоа подклкпдв К входу аналогонгояфрсжого преобразоватв- лн к второму входу нуль-органа.

Источники информацнн, принятые во внимание при экспертиав 1. Авторское (свидетельство СССР N 640365, кл. G 11 С 7/ОО, OS.O4,76

2.. Беки Дж. и др. Теория и применение гибридных вычислительных снсгем. М., Мир, 1970, с. 45.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| МНОГОКАСКАДНЫЙ УСИЛИТЕЛЬ | 1992 |

|

RU2106740C1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1480127A1 |

| Усилитель выборки и запоминания | 1988 |

|

SU1589323A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

Авторы

Даты

1982-07-07—Публикация

1978-02-20—Подача