ВхоЗ

I 33

rqJfi Wf-fTll

..-V

Saixod

Ш

(O

cr

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Усилитель выборки и запоминания для аналого-цифрового преобразователя | 1978 |

|

SU942131A1 |

| Многоразрядный логарифмический аналого-цифровой преобразователь | 1983 |

|

SU1170614A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Аналоговое запоминающее устройство | 1988 |

|

SU1535232A1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ | 2007 |

|

RU2389070C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

| Устройство для контроля длительности импульсов | 1980 |

|

SU901949A1 |

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2018980C1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

Изобретение относится к аналого-цифровым и цифроаналоговым устройствам и может быть использовано в вычислительной и измерительной технике. Цель изобретения - повышение быстродействия и расширение области применения за счет увеличения класса решаемых задач усилителя выборки и запоминания. Усилитель выборки и запоминания содержит предварительный и выходной каскады усиления, ключи, элементы памяти, компараторы, триггеры, генератор импульсов, элементы И и ИЛИ, источники пороговых напряжений и сдвиговый регистр. Цель изобретения достигается за счет изменения постоянной времени цепи заряда накопительного конденсатора в зависимости от скорости изменения входного сигнала. 1 з.п.ф-лы, 1 ил.

CR

00

Изобретение относится к аналого-цифро- чае, если входной сигнал в начальный мо- вым и цифроаналоговым устройствам и мент времени находится вне зоны измерения может быть использовано в вычислитель- скорости изменения и меньше ее нижней ной и измерительной технике.границы, задаваемой источником 28, то комЦель изобретения - повышение быстро- паратор 25 находится в единичном состоя действия и расширение области применения усилителя за счет увеличения класса решаемых задач путем изменения постоянной времени цепи заряда накопительного элемента в зависимости от скорости изменения входного сигнала.

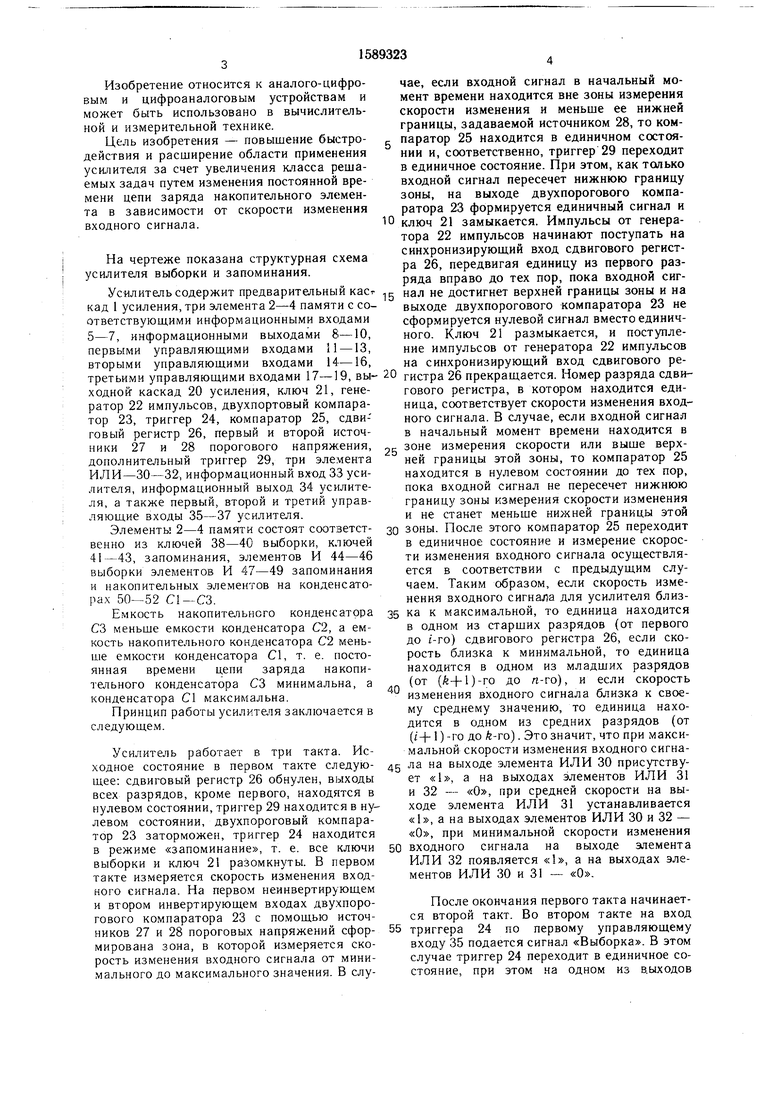

На чертеже показана структурная схема усилителя выборки и запоминания.

НИИ и, соответственно, триггер 29 переходит в единичное состояние. При этом, как только входной сигнал пересечет нижнюю границу зоны, на выходе двухпорогового компаратора 23 формируется единичный сигнал и 10 ключ 21 замыкается. Импульсы от генератора 22 импульсов начинают поступать на синхронизируюш,ий вход сдвигового регистра 26, передвигая единицу из первого разряда вправо до тех пор, пока входной сиг- Усилитель содержит предварительный каст g нал не достигнет верхней границы зоны и на кад 1 усиления, три элемента 2-4 памяти с со- выходе двухпорогового компаратора 23 не ответствуюшими информационными входами сформируется нулевой сигнал вместо единкч- 5-7, информационными выходами 8-10, ного. Ключ 21 размыкается, и поступле- первыми управляюшими входами 11-13, ние импульсов от генератора 22 импульсов вторыми управляюшими входами 14-16, на синхронизируюш,ий вход сдвигового ре- третьими управляюш,ими входами 17-19, вы- 20 гистра 26 прекращается. Номер разряда сдви- ходной- каскад 20 усиления, ключ 21, гене- гового регистра, в котором находится единица, соответствует скорости изменения входного сигнала. В случае, если входной сигнал

„„, .,„„ .,.в начальный момент времени находится в

НИКИ 27 и 28 порогового напряжения, зоне измерения скорости или выше верх- дополнительный триггер 29, три элемента ней границы этой зоны, то компаратор 25

находится в нулевом состоянии до тех пор, пока входной сигнал не пересечет нижнюю границу зоны измерения скорости изменения и не станет меньше нижней границы этой

ратор 22 импульсов, двухпортовый компаратор 23, триггер 24, компаратор 25, сдви- говый регистр 26, первый и второй источИЛИ-30-32, информационный вход 33 усилителя, информационный выход 34 усилителя, а также первый, второй и третий управ- ляюш,ие входы 35-37 усилителя.

Элементы 2-4 памяти состоят соответст- зо зоны. После этого компаратор 25 переходит

венно из ключей 38-40 выборки, ключей 41-43, запоминания, элементов И 44-46 выборки элементов И 47-49 запоминания и накопительных элементов на конденсаторах 50-52 С1-СЗ.

в единичное состояние и измерение скорости изменения входного сигнала осуществляется в соответствии с предыдущим случаем. Таким образом, если скорость изменения входного сигнала для усилителя близ- Емкость накопительного конденсатора 35 ка к максимальной, то единица находится

СЗ меньше емкости конденсатора С2, а ем-в одном из старших разрядов (от первого

до i-ro) сдвигового регистра 26, если скорость близка к минимальной, то единица находится в одном из младших разрядов (от (k-i-)-ro до п-го), и если скорость изменения входного сигнала близка к своему среднему значению, то единица находится в одном из средних разрядов (от (г+1) -го до /г-го). Это значит, что при макси- Усилитель работает в три такта. Ис- мальной скорости изменения входного сигнаходное состояние в первом такте следую- 45 - выходе элемента ИЛИ 30 присутствует «1, а на выходах элементов ИЛИ 31 и 32 - «О, при средней скорости на выходе элемента ИЛИ 31 устанавливается «1, а на выходах элементов ИЛИ 30 и 32 - ;0, при минимальной скорости изменения

кость накопительного конденсатора С2 мень- aie емкости конденсатора С1, т. е. постоянная времени цепи заряда накопительного конденсатора СЗ минимальна, а конденсатора С1 максимальна.

Принцип работы усилителя заключается в следующем.

40

щее: сдвиговый регистр 26 обнулен, выходы всех разрядов, кроме первого, находятся в нулевом состоянии, триггер 29 находится в нулевом состоянии, двухпороговый компаратор 23 заторможен, триггер 24 находится

ИЛИ 32 появляется «1, а на выходах элементов ИЛИ 30 и 31 -

в режиме «запоминание, т. е. все ключи 50 входного сигнала на выходе алемента выборки и ключ 21 разомкнуты. В первом такте измеряется скорость изменения входного сигнала. На первом неинвертирующем и втором инвертирующем входах двухпорогового компаратора 23 с помощью источПосле окончания первого такта начинается второй такт. Во втором такте на вход

НИКОВ 27 и 28 пороговых напряжений сфор- 55 триггера 24 по первому управляющему мирована зона, в которой измеряется ско-входу 35 подается сигнал «Выборка. В этом

случае триггер 24 переходит в единичное состояние, при этом на одном из в.ыходов

рость из {енения входного сигнала от минимального до максимального значения. В слуИЛИ 32 появляется «1, а на выходах элементов ИЛИ 30 и 31 -

входного сигнала на выходе алемента

элементов И 44-46 устанавливается единичный сигнал. Если скорость входного сигнала максимальна, то на другом входе элемента И 46 тоже устанавливается единичный сигнал (см. работу в первом такте), ключ 40 замыкается и конденсатор 52 СЗ заряжается до величины входного сигнала. При минимальной скорости входного сигнала на другом входе элемента И 44 устанавливается единичный сигнал, ключ 38 замыкается и конденсатор 50 С1 заряжается до величины входного сигнала. При средней скорости входного сигнала происходит заряд конденсатора 51 С2 до величины входного сигнала. Таким образом, постоянная времени цепи заряда накопительного конденсатора выбирается в зависимости от скорости изменения входного сигнала.

В третьем такте на вход триггера 24 по второму управляющему входу 36 поступает сигнал «Запоминание. В этом случае триггер 24 переходит в нулевое состояние, 0 при этом на одном из входов элементов И- 47-49 устанавливается единичный сигнал. В зависимости от скорости входного сигнала на другом входе одного из элементов И 47-49 тоже устанавливается единичный сигнал и соответствующим из ключей 41 - 43 запоминания переводится из разомкнутого в замкнутое состояние, в то время как подключенный своим выходом к входу этого ключа запоминания ключ выборки из

та ИЛИ, двухпороговый ком.параюр с дву мя источниками пороговых напряжений, ком паратор, дополнительный триггер, сдвиговый регистр, синхровход которого соедиж-и 5 с сигнальным выходом к.пюча, з установоч ный вход - с третьим управляющим входом усилиталя и вторым входом дополнительного триггера, выход которого чен к стробирующему входу двухпорТ)гово- го компаратора, первый вход дополнительного триггера подключен к выходу компаратора, инвертирующий вход которого подключен к первому инвертирующему и второму неинвертирующему входам двухпорогово- го компаратора и информационному вхо15. ДУ усилителя, неинвертирующий вход компаратора соединен с одним из источников порогового напряжения и вторым инвертирующим входом двухпорогового компаратора, первый неинвертирующий вход которого соединен с другим источником порогового напряжения, выход двухпорогового компаратора соединен с управляющим входом ключа, второй вход триггера является вторым управляющим входом усилителя, а единичный выход соединен с первыми

25 управляющими входами элементов памяти, нулевой выход триггера соединен с вторыми управляющими входами элементов памяти., третьи управляющие выходы элементов памяти соединены соответственно с выходами первого, второго и третьего элементов

замкнутого состояния переходит в разомкну- 30 ИЛИ, входы которых соединены с сооттое. Таким образом, на информационном выходе усилителя формируется сигнал, равный входному, который сохранится в течение всего времени запоминания. После окончания третьего такта усилитель устанавливается в исходное состояние с помощью сигнала установки, поступающего на третий управляющий вход усилитатя.

Формула изобретения

35

40

ветствующими выходами сдвигового регистра, информационные входы и выходы второго и третьего элементов памяти соединены соответственно с информационными входом и выходом первого элемента памяти. 2. Усилитель по п. 1, отличающийся тем, что элемент памяти содер.жит ключ выборки, ключ запоминания, накопительный элемент на конденсаторе, элемент И выборки, элемент И запоминания, сигнальный вход ключа выборки является информационным входом элемента памяти, сигналь ный выход ключа выборки соединен с первым выводом конденсатора и с сигнальным входом ключа запоминания, сигнальный выход которого является информацивходом усилителя, а выход соединен с инфор- 45 онным выходом элемента памяти, второй

мационным входом элемента памяти, информационный выход которого соединен с входом выходного каскада усиления, выход которого является информационным выходом усилителя, триггер, первый вход которого является первым управляющим входом усилителя, генератор импульсов, выход которого соединен с сигнальным входом ключа, отличающийся тем, что, с целью повыщения быстродействия и расширения области применения усилителя за счет увеличения класса рещаемых задач, в пего введены два дополнительных элемента памяти, три элеменвыБОд конденсатора соединен с общей шиной, yпpaвv яющий вход ключа выборки подсоединен к первому элементу И выборки, первый вход которого является первым управляющим входом элемента памяти, а второй 50 соединен с вторым входом элемента И запоминания и является третьим управляющим входом элемента памяти, первый вход элемента И запоминания является вторым управляющим входом элемента памяти, выход элемента И запоминания подключен к управляющему входу ключа запоминания.

55

0

та ИЛИ, двухпороговый ком.параюр с дву мя источниками пороговых напряжений, ком паратор, дополнительный триггер, сдвиговый регистр, синхровход которого соедиж-и 5 с сигнальным выходом к.пюча, з установоч ный вход - с третьим управляющим входом усилиталя и вторым входом дополнительного триггера, выход которого чен к стробирующему входу двухпорТ)гово- го компаратора, первый вход дополнительного триггера подключен к выходу компаратора, инвертирующий вход которого подключен к первому инвертирующему и второму неинвертирующему входам двухпорогово- го компаратора и информационному вхо5. ДУ усилителя, неинвертирующий вход компаратора соединен с одним из источников порогового напряжения и вторым инвертирующим входом двухпорогового компаратора, первый неинвертирующий вход которого соединен с другим источником порогового напряжения, выход двухпорогового компаратора соединен с управляющим входом ключа, второй вход триггера является вторым управляющим входом усилителя, а единичный выход соединен с первыми

5 управляющими входами элементов памяти, нулевой выход триггера соединен с вторыми управляющими входами элементов памяти., третьи управляющие выходы элементов памяти соединены соответственно с выходами первого, второго и третьего элементов

ИЛИ, входы которых соединены с соот5

0

ветствующими выходами сдвигового регистра, информационные входы и выходы второго и третьего элементов памяти соединены соответственно с информационными входом и выходом первого элемента памяти. 2. Усилитель по п. 1, отличающийся тем, что элемент памяти содер.жит ключ выборки, ключ запоминания, накопительный элемент на конденсаторе, элемент И выборки, элемент И запоминания, сигнальный вход ключа выборки является информационным входом элемента памяти, сигналь ный выход ключа выборки соединен с первым выводом конденсатора и с сигнальным входом ключа запоминания, сигнальный выход которого является информацивыБОд конденсатора соединен с общей шиной, yпpaвv яющий вход ключа выборки подсоединен к первому элементу И выборки, первый вход которого является первым управляющим входом элемента памяти, а второй соединен с вторым входом элемента И запоминания и является третьим управляющим входом элемента памяти, первый вход элемента И запоминания является вторым управляющим входом элемента памяти, выход элемента И запоминания подключен к управляющему входу ключа запоминания.

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU391610A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Усилитель выборки и запоминания для аналого-цифрового преобразователя | 1978 |

|

SU942131A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-21—Подача