Изобретение относится к информаUHOHHto-HSMapHTenbHofl и вычислитедьнрй технике: и может быть испрльзовано, например, для приема накопления и Обработки данных по отдельному региону наб.пюдательной сети всетлирной службы погоды.

Известна система уплотнения данных, которая блок памяти, адресный регистр, регистр кода повторителя, логический блок управления кодом повторителя, блок 5а1равления, элемент И, регистр адреса прираще- , ния, числовой регистр Г1}.

Недостатком системы является необходимость запоминания в блоке памяти специальных кодов повторителей. Уплотнение записи информационного кода приводит к появлению дополнительных признаков - кодов указателей, снижающих эффективность зтого уплотнения, повыпакяцих время выбор ки информационного кода из блока памяти из-за необходимости ангшиза дополнительных признаков.

Увеличение времени выборки и, как следствие, обработки данных делает невозможным использование такой системы для оперативного анализа

экстремальных метеорологических явлений .

Наиболее близким к предлагаемой систе является устройство сжатия информации, содержащее псевдослучайный, преобразователь, подключе нный через входной регастр к источнику информации, выход блока псевдослучайного преобразователя через последовательно соединенные регистр адреса и блок памяти соединен с перВЕ м входом регистра числа, второй вход которого объединен с первым входом блока вькисления кодового расстоя 5 ния и подключен к входу блока псевдослучайного преобразования, выходы которого соединены с третьим и четвертым входами регистра чисйа, пятый

„ вход которого соединен с выходом

регистра сдвига, хронизатор соединен с вторым входом блока вычисления кодового расстояния и первым входом регистра сдвига, втсрой вход которого соединен с вторым выходом

25 блока псевдослучайного преобразователя 2 .

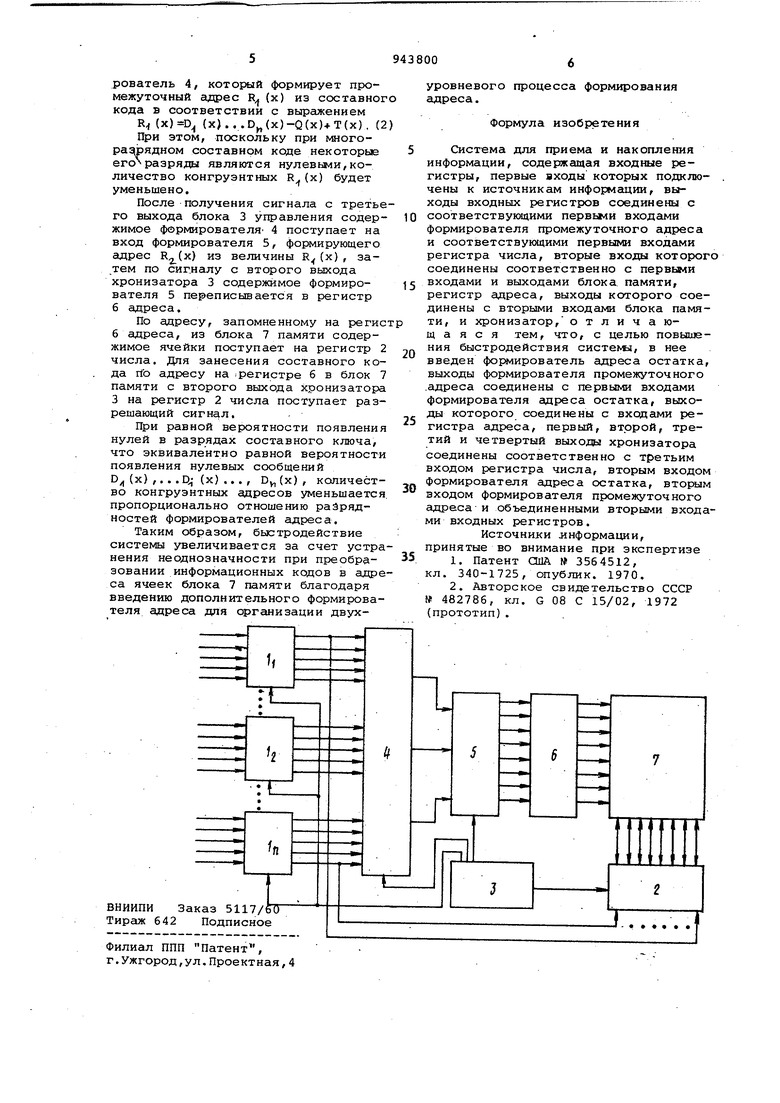

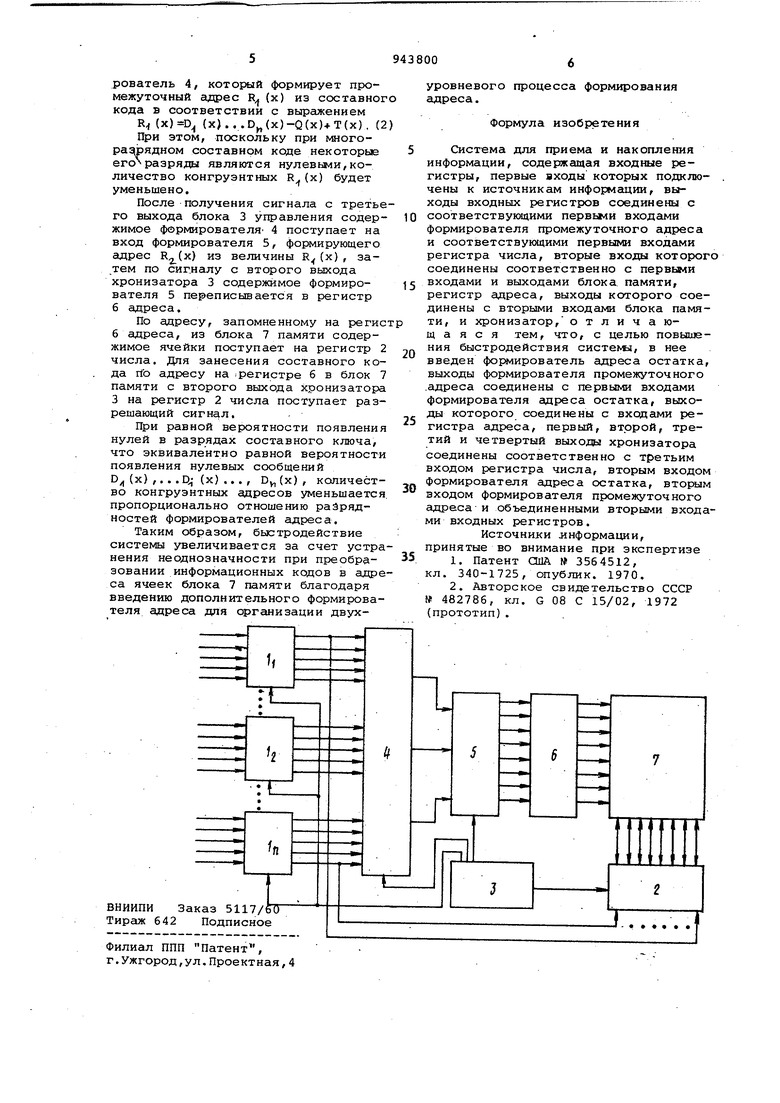

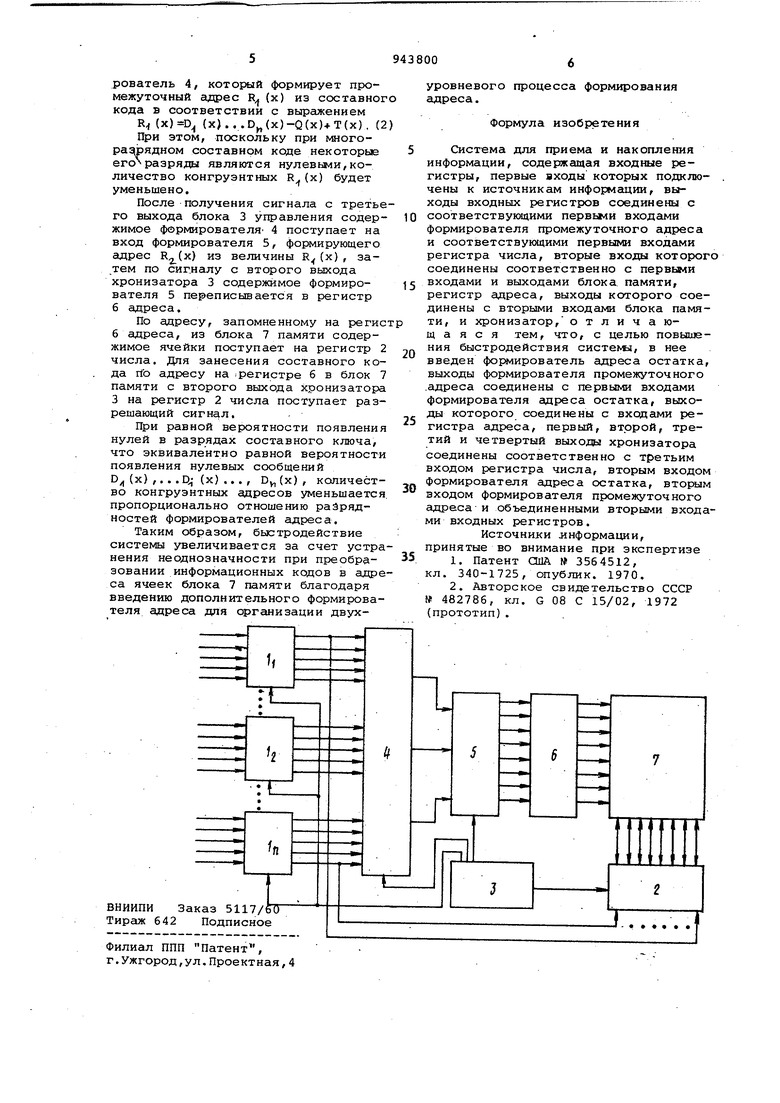

В зтом устройстве входные инфсфмационные коды Ц х),.. .0.,- (х) , .. ,D(x) последовательно во времени пос.тупают на вход- блока псевдослучайного пре.образователя, где формируется адрес в соответствии с входныг4 информационным кодом. Содержи «5е блок псевдослучайного преобразования пос тупает в регистр адреса. При эчсм функциональная связь меязду информационным входным кедом (x) и,содер жимым R (х) регистра адреса обеспечивается за счет жесткой внутренней структуры блока псевдослучайног преобразования, реализукадего выраясе ние Щ(х} D (X) - Q,-(x). Т(х), (1 где вид многочлена Т{х) определяет структуру блока преобразования. В выражении (1) величина (х), являющаяся остатком от деления мног члена D (х) на многочлен Q (х) , используется в качестве прямого адрес памяти. Вид многочлена Т(х), определяюще го структуру блока преобразователя, выбирается таким образом, чтобы пол чить равномерное распределение адре сов R(x) по всему диапазону ячеек iблока памяти. При разрядности регистра адреса R(x). 4 многочлен Т(х) имеет следующий вид Т(х)1- т (х)+0 Т(х)+1 Т(х)+1. Время доступа k произвольной ячейке блока памяти в известной сие теме уменьшается за счет обеспечени одновременно со сжатием информации жесткой функциональной (в соответствии с (1) связи между входным сообщением и адресом ячейки памяти. Недостатком такой системы является неоднозначность функционального преобразования информационных кодов в адреса ячеек блока памяти, что приводит к уменьшению быстродействия устройства. Это вызвано необходимостью просмотра дополнительных областей памяти и модификации адресов в случаях конгруэнтност Rj, (X) . Цель изобретения - увеличение быстродействия системы. Поставленная цель достигается тем, что в систему для приема и накопления информации, Содержащую входные регистры, первыз входы которых подключены к источникам инфор мации, выходы входных регистров сое динены с соответствующими первыми входами формирователя промежуточног адреса и соответствующими первыми входами регистра числа, вторые вход которого соединены соответственно с первыми входами и выходами блока памяти, регистр адреса, выходы кото рого соединены с вторыми входами блока памяти, хронизатор, введен формирователь адреса, остатка, выходы формирователяпромежуточного адреса соединены с первьвчи входами формирователя адреса остатка, выхо.Йы которого соединены с входами регистра адреса, первый, второй, третий и четвертый выходы хронизатора соединены соответственно с третьим входом регистра числа, вторым входом формирователя адЬеса остатка, втор)дал входом формирователя промежуточного адреса и объединенными вторьми входами входных регистров. На чертеже приведена блок-схема предлагаемой системы. Система содержит входные регистры 1 -Ij,, регистр 2 числа, хронизатор 3, формирователь 4 промежуточного адреса, формирователь 5 адреса остатка, регистр 6 адреса, блок 7 памяти. Входные двоичные регистра 1 -1 предназначены для хранения и одновременной записи входных информационных сообщений D (х) - D((x). Формирователь 4 служит для фо ирования промежуточного адреса R(х) из последовательной записи п кодов D (х),0(х),...0 (х) .. .D(х), являющегося составным кодом при кодадресном преобразовании входньк сообщений в номер ячейки блока 7 памяти. Формирователь 5 предназначен для формирования адреса, R2.{x) из промежуточного адреса R(х), при этом разрядность R.2(x) выбирается равной разрядности регистра б адреса. Регистр адреса 6 служит для хранения R(x) адреса обращения к блоку 7 памяти, который осуществляет хранение информации. Регистр 2 числа обеспечивает кратковременное запоминание при считывании или записи из блока 7 памяти составного ключа, поступающего одновременно в регистр 2 числа. Хронизатор 3 предназначен для . управления и временной синхронизации остальных блоков системы. Система работает следующим образом. Входное сообщения D (х) ,. , .D,- (х) .. . Dy,(x), характеризующие исследуемый физический объект по ряду признаков, например D (х) - географические координаты, D2(x) - номера станций всемирной службы погоды, D,- (х) - тип и временные параметры измерений, D(x) - двоичные значения физических величин, поступают на регистры Необходимым условием эффективной работы предлагаемой-системы является наличие нулевых значений кодов в информативных сообщениях D (х) , D2(x) ,.. .0 (х) ,.. .Ои(х) . При этом общее количество входных ненулевых информационных сообщений не должно превышать общее количество ячеек блока 7 памяти. По сигналам с выхода хронизатора 3 эти сообщения поступают в формирователь 4, который формирует промежуточный адрес R (х) из составног кода в соответствии с выражением R (x)D (x)...D(x)-Q(x)+T(x). (2 При этом, поскольку при многораэшядном составном коде некоторые его разряды являются нулевьми,количество конгруэнтных R(х) будет уменьшено. После получения сигнала с третье го выхода блока 3 управления содержимое формирователя 4 поступает на вход формирователя 5, формирующего адрес R2(x) из величины R (х) , затем по сигналу с второго выхода хронизатора 3 содержимое формирователя 5 переписывается в регистр б адреса. По адресу, запомненному на регис б адреса, из блока 7 памяти содержимое ячейки поступает на регистр числа. Для занесения составного кода rto адресу на регистре б в блок памяти с второго выхода хронизатора 3 на регистр 2 числа поступает разрешающий сигнал. При равной вероятности появлени нулей в разрядах составного ключа, что эквивалентно равной вероятности появления нулевых сообщений D (х) ,,,,Ц,- (х) ,,,, Dy,(x), количест во конгруэнтных адресов уменьшаетс пропорционально отношению разрядностей формирователей адреса. Таким образом, быстродействие системы увеличивается за счет устр нения неоднозначности при преобразовании информационных кодов в адр са ячеек блока 7 памяти благодаря введению дополнительного формирова теля адреса для организации двухровневого процесса формирования дреса. Формула изобретения Система для приема и накопления информации, содержащая входные регистры, первые входы которых подклю- . чены к источникам информации, выходы входных регистров соединены с соответствукядими первыми входами формирователя промежуточного адреса и соответствующими первыми входами регистра числа, вторые входы которого соединены соответственно с первьлли входами и выходами блока памяти, регистр адреса, выходы которого соединены с вторыми входами блока памяти, и хронизатор, отличающаяся тем, что, с целью повышения быстродействия систеыл, в нее введен фо5 1ирователь адреса остатка, выходы формирователя промежуточного .адреса соединены с первыми входами формирователя адреса остатка, выходы которого соединены с вхсдами регистра адреса, первый, второй, третий и четвертый выходы хронизатора соединены соответственно с третьим входом регистра числа, вторым входом формирователя адреса остатка, вторым входом формирователя промежуточного ащреса и объединенными вторыми входами входных регистров. Источники информации, принятые во внимание при экспертизе 1,Патент США 3564512, кл, 340-1725, опублик, 1970, 2,Авторское свидетельство СССР № 482786, кл, G 08 С 15/02, 1972 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оперативного накопления информации | 1982 |

|

SU1075287A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Декодирующее устройство | 1989 |

|

SU1644223A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

Авторы

Даты

1982-07-15—Публикация

1980-06-26—Подача