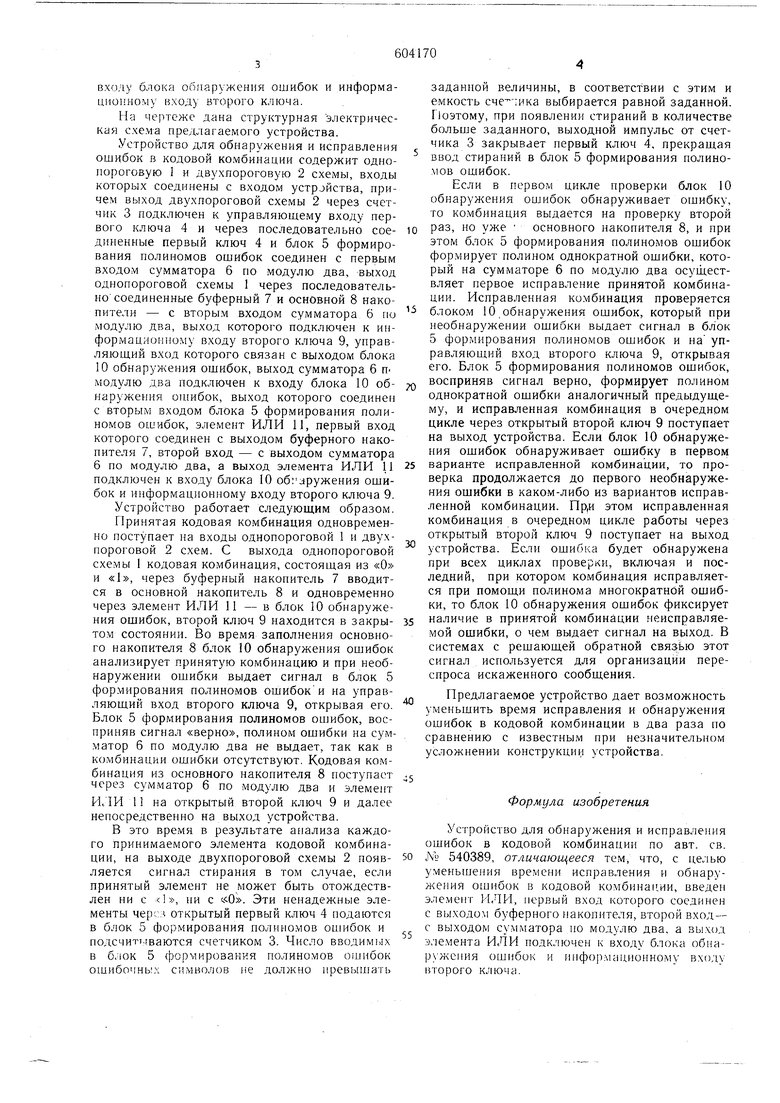

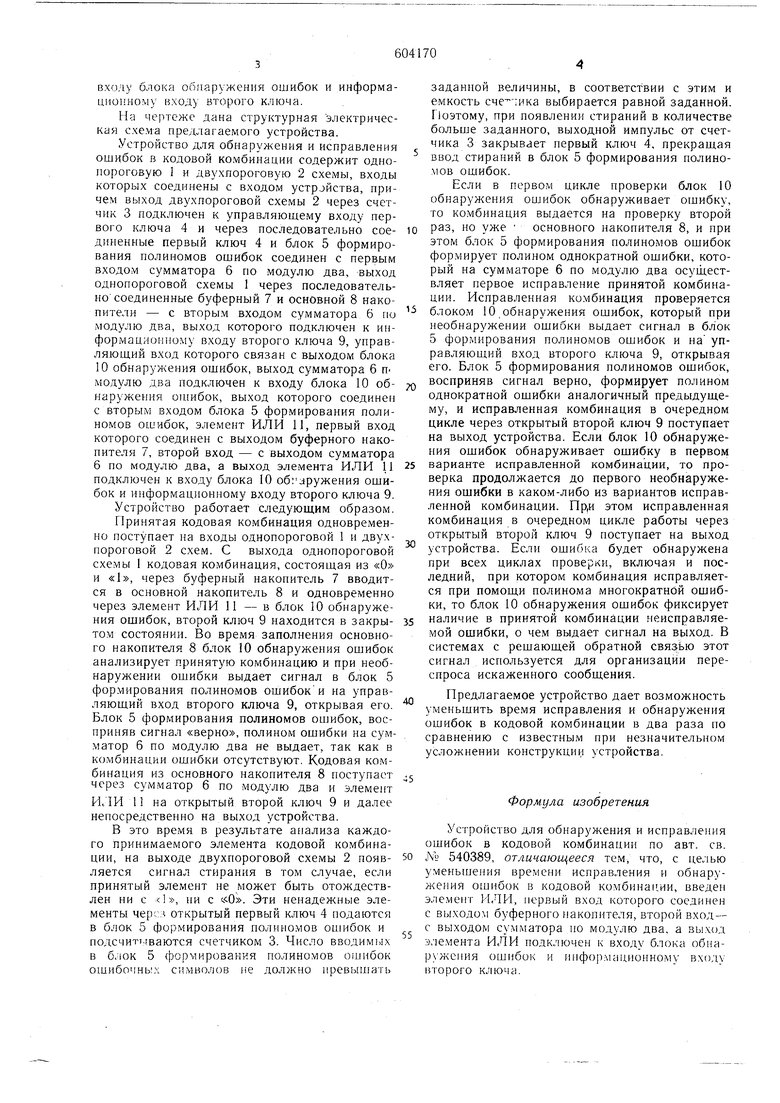

Изобретение относится к технике связи и может использоваться в устройствах защиты от ошибок аппаратуры передачи данных. По основному авт. св. № 540389 известно устройство для обнаружения и исправления ошибок в кодовой комбинации, содержаш,ее однопороговую и двухпороговую схемы, входы которых соединены с входом устройства, причем выход двухпороговой схемы через счетчик подключен к управляющему входу первого ключа и через последовательно соединенные первый ключ и блок формирования полиномов ошибок соединен с первым входом сумматора по модулю два, выход однопороговой схемы через последовательно соединенные буферный и основной накопители - с вторым входом сумматора по модулю два, выход которого подключен к информационному входу второго ключа, управляющий вход которого связан с выходом блока обнаружения ошибок, выход сумматора по модулю два подключен к входу блока обнаружения ошибок, выход которого соединен с вторым входом блока формирования полиномов ошибок. Однако такое устройство для обнаружения и исправления ошибок в кодовой комбинации обладает большим временем исправления и обнаружения ошибок в кодовой комбинации. Цель изобретения - уменьшение времени исправления и обнаружения ошибок в кодовой комбинации. Для этого в устройство для обнаружения и исправления ошибок в кодовой комбинации, содержащее однопороговую и двухпороговую схемы, входы которых соединены с входом устройства, причем выход двухпороговой схемы через счетчик подключен к управляющему входу первого ключа и через последовательно соединенные первый ключ и блок фор.мирования полиномов ошибок соединен с первым входом сумматора по модулю два, выход однопороговой схемы через последовательно соединенные буферный и основной накопители - с вторым входом сумматора по модулю два, выход которого подключен к информационному входу второго ключа, управляющий вход которого связан с выходом блока обнаружения ошибок, выход сумматора по . два подключен к входу блока обнаружения ошибок, выход которого соединен с вторым входом блока формирования полиномов ошибок, введен элемент ИЛИ, первый вход которого соединен с выходом буферного накопителя, второй вход - с выходом сумматора по модулю два, а выход элемента ИЛИ подключен к вхолу блока обнаружения ошибок и информационному входу второго ключа. На чертеже дана структурная электрическая схема предлагаемого устройства. Устройство для обнаружения и исправления ошибок в кодовой комбинации содержит однопороговую 1 и двухпороговую 2 схемы, входы которых соединены с входом устройства, причем выход двухпороговой схемы 2 через счетчик 3 подключен к управляющему входу первого ключа 4 и через последовательно соединенные первый ключ 4 и блок 5 формирования полиномов ошибок соединен с первым входом сумматора 6 по модулю два, выход однопороговой схемы 1 через последовательно соединенные буферный 7 и основной 8 накопители - с вторым входом сумматора 6 по модулю два, выход которого подключен к информационному входу второго ключа 9, управляющий вход которого связан с выходом блока 10 обнаружения ощибок, выход сумматора 6 пмодулю два подключен к входу блока 10 обнаружения ошибок, выход которого соединен с вторым входом блока 5 формирования полиномов ошибок, элемент ИЛИ 11, первый вход которого соединен с выходом буферного накопителя 7, второй вход - с выходом сумматора 6 по модулю два, а выход элемента ИЛИ 11 подключен к входу блока 10 об:аружения ошибок и и})формац 1онному входу второго ключа 9. Устройство работает следующим образом. Принятая кодовая комбинация одновременно поступает на входы однопороговой 1 и двухпороговой 2 схем. С выхода однопороговой схемы 1 кодовая комбинация, состоящая из «О и «1, через буферный накопитель 7 вводится в основной накопитель 8 и одновременно через элемент ИЛИ 11 - в блок 10 обнаружения ошибок, второй ключ 9 находится в закрытом состоянии. Во время заполнения основного накопителя 8 блок 10 обнаружения ошибок анализирует принятую комбинацию и при необнаружении ошибки выдает сигнал в блок 5 формирования полиномов ошибоки на управляющий вход второго ключа 9, открывая его. Блок 5 формирования полиномов ошибок, восприняв сигнал «верно, полином ошибки на сумматор 6 по модулю два не выдает, так как в комбинации ошибки отсутствуют. Кодовая комбинация из основного накопителя 8 поступает через сумматор 6 по модулю два и элемент ИЛИ 11 на открытый второй ключ 9 и далее непосредственно на выход устройства. В это время в результате анализа каждого принимаемого элемента кодовой комбинации, на выходе двухпороговой схемы 2 ноявляется сигнал стирания в том случае, если принятый элемент не .может быть отождествлен ни с , ни с -f-Q. Эти ненадежные элементы чер:.:. открытый первый ключ 4 подаются в блок 5 формирования полиномов ошибок и подсчитьшаются счетчиком 3. Число вводимых в блок 5 формирования полиномов ошибок ошибочных символов jie должно превышать заданной неличины, в соответствии с этим и емкость выбирается равной заданной. Г1оэтому, при появлении стираний в количестве больше заданного, выходной импульс от счетчика 3 закрывает первый ключ 4, прекращая ввод стираний в блок 5 формирования полиномов ошибок. Если в первом цикле проверки блок 10 обнаружения ошибок обнаруживает ошибку, то комбинация выдается на проверку второй раз, но уже основного накопителя 8, и при этом блок 5 формирования полиномов ошибок формирует полином однократной ошибки, который на сумматоре 6 по модулю два ocyiiiecTвляет первое исправление принятой комбинации. Исправленная комбинация проверяется блоком 10 обнаружения ошибок, который при необнаружении ошибки выдает сигнал в блок 5 формирования полиномов ошибок и на управляющий вход второго ключа 9, открывая его. Блок 5 формирования полиномов ошибок, восприняв сигнал верно, формирует полином однократной ошибки аналогичный предыдущему, и исправленная комбинация в очередном цикле через открытый второй ключ 9 поступает на выход устройства. Если блок 10 обнаружения ошибок обнаруживает ошибку в первом варианте исправленной комбинации, то проверка продолжается до первого необнаружения ощибки в каком-либо из вариантов исправленной комбинации. Пр,и этом исправленная комбинация в очередном цикле работы через открытый второй ключ 9 поступает на выход устройства. Если ошибка будет обнаружена при всех циклах проверки, включая и последний, при котором комбинация исправляется при помощи полинома многократной ошибки, то блок 10 обнаружения ощибок фиксирует наличие в принятой комбинации неисправляемой ошибки, о чем выдает сигнал на выход. В системах с решающей обратной связью этот сигнал используется для организации переспроса искаженного сообщения. Предлагаемое устройство дает возможность уменьшить время исправления и обнаружения ошибок в кодовой комбинации в два раза но сравнению с известным при незначительном усложнении конструкции устройства. Формула изобретения Устройство для обнаружения и исправления ошибок в кодовой комбинации по авт. св. Л1 540389, отличающееся тем, что, с целью уменынения времени исправления и обнаружения ошибок в кодовой комбина1,ии, введен элемент ИЛИ, первый вход которого соединен с выходом буферного накопителя, второй вход- с выходом сумматора но модулю два, а выход элемента ИЛИ подключен к входу блока обнаружения ошибок и инфор:м;)1;нонному входу второго ключа.

ОшиЬна

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ииСпРАВлЕНия ОшибОК B КОдОВОйКОМбиНАции | 1979 |

|

SU801283A2 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1974 |

|

SU540389A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1976 |

|

SU599267A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1974 |

|

SU526898A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1078655A2 |

| Устройство магнитной записи для коррекции цифровой информации | 1979 |

|

SU949717A1 |

| Устройство для исправления ошибок в кодовой комбинации | 1977 |

|

SU634469A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1287296A1 |

Авторы

Даты

1978-04-25—Публикация

1976-08-01—Подача