1

Изобретение относится к связи и может быть использовано в аппаратуре сиотемы передачи данных для синхронизации рекуррентными последовательностями при приеме информации по R каналам с временным разделением каналов на различных скоростях (например, 1,2; 2,4, 4,8 9, 6 кГц).

Известен анализатор рекуррентного . сигнала фазового пуска содержащий после-, доватепьно соединенные анализатор ошибок, блок памяти и коммутатор, к второ му входу которого подключен выход nepBt го блока сравнения и первый вход второго блока сравнения, второй вход которого j объединен с третьим входом коммутатора и 5юляется информационньщ входом устройства LI}.

Недостатком данного анализатора является его применение только в однока- 20 нальных системах с фиксированной скоростыб. В устройстве присутствует шина тактовых импульсов с одной фиксированной скоростью, равной скорости пришма-i

мой информации, в результате чего ог раничивается применяемость известного анализатора. Лля прнменеивя в многоканальных системах потребовалось бы количество известных анализаторов, ра&ное количеству каналов.

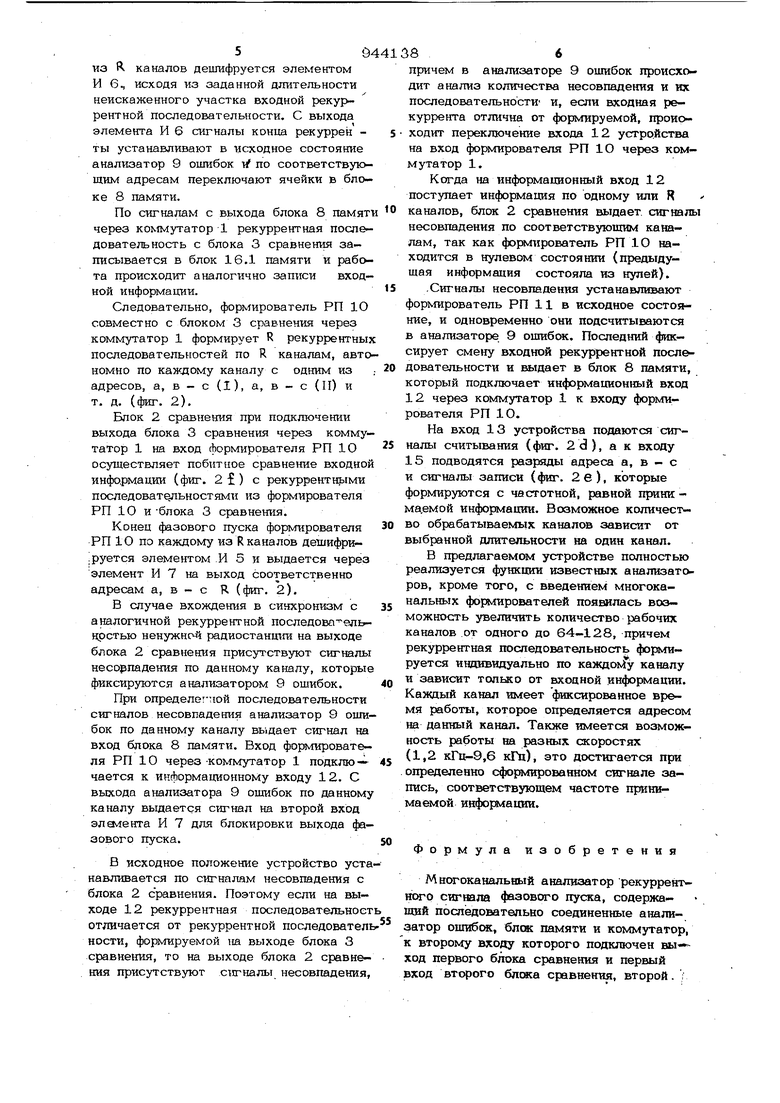

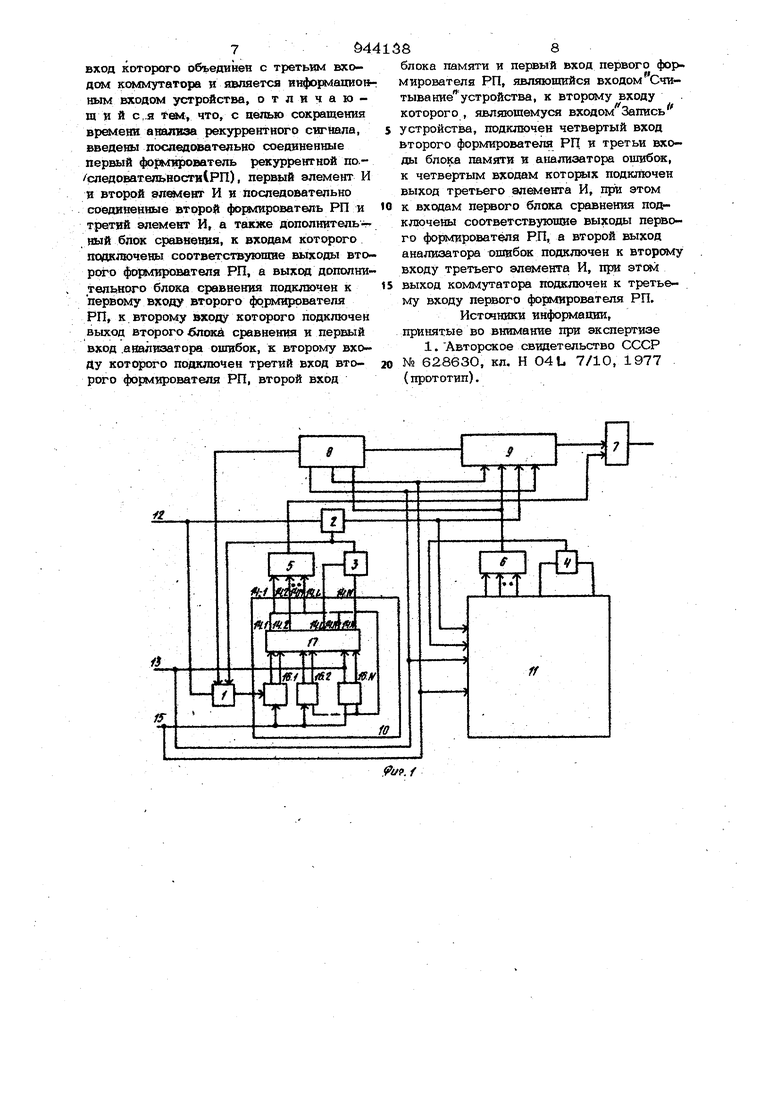

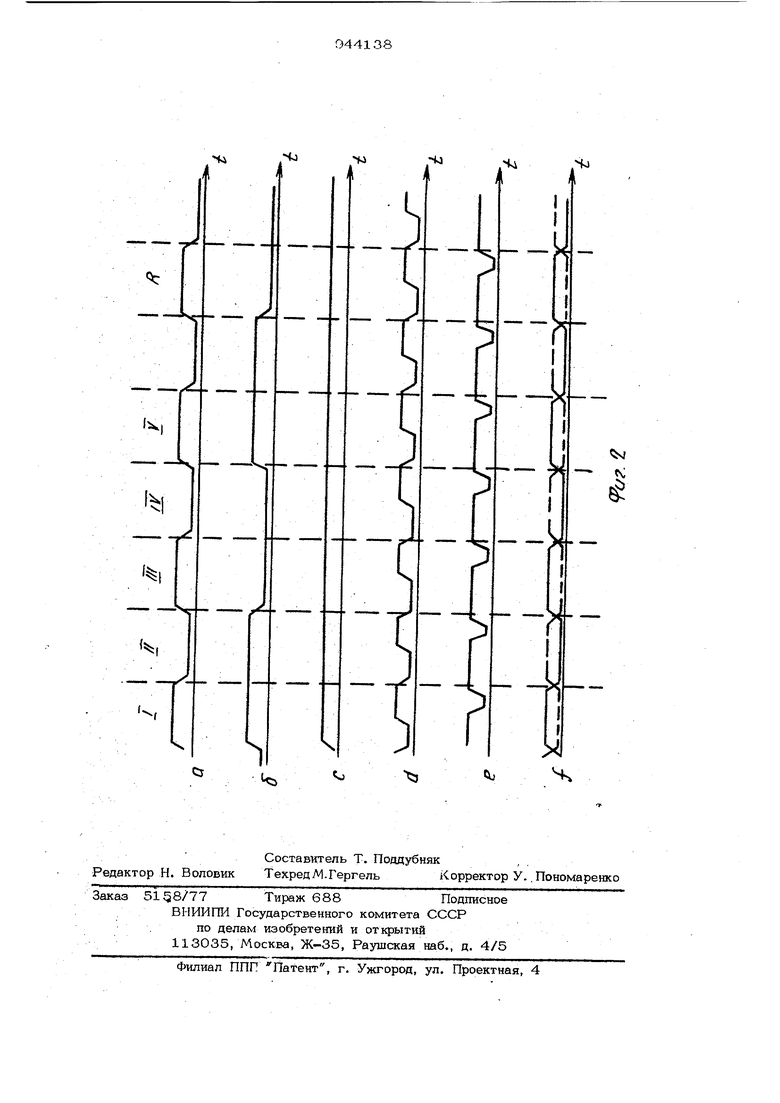

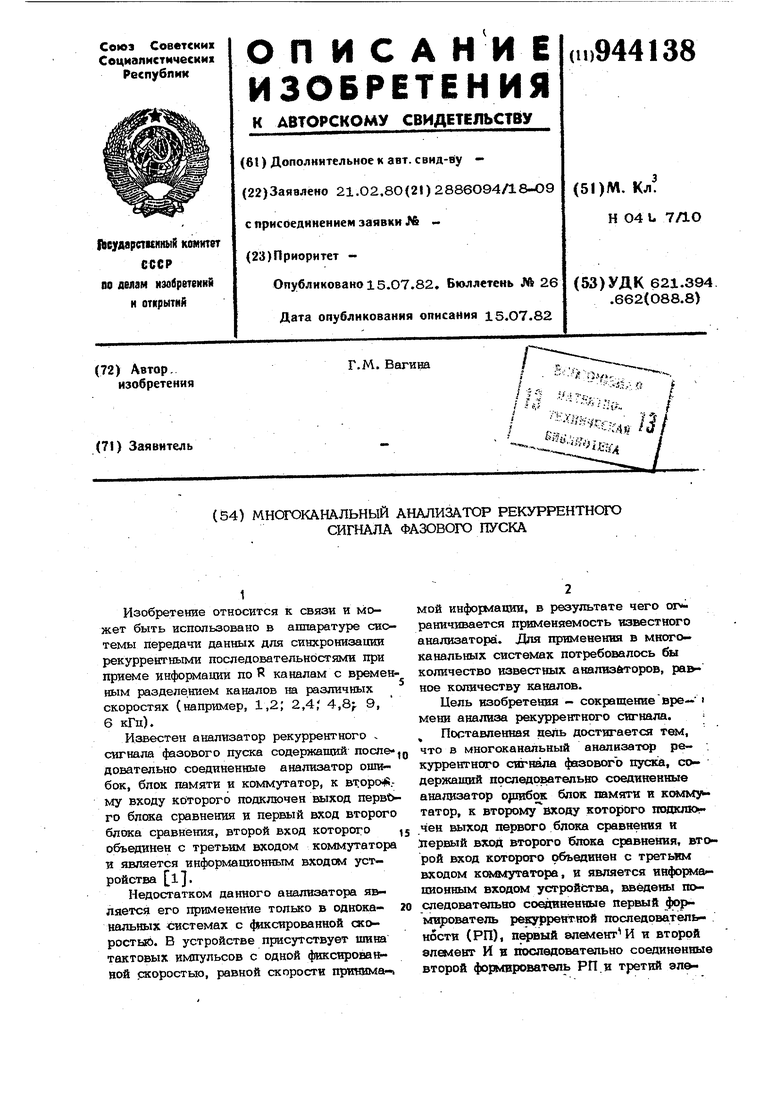

Цель изобретения - сокращение вре- i мени анализа рекуррентного сигнала. Поставленная аель достигается тем, что в многоканальный анализатор рекуррентного сигнала фазового пуска, содержащий последовательно соединенные анализатор ошибок блок памяти и ксилмуьтатор, к второму входу которого подклк чей выход первого блока сравнения и .Первый вход второго блока сравнения, второй вход которого объединен с третьим входом коммутатора, и является информационным входом устройства, введены ш следовательно соединенные первый формирователь рекуррентной последовательности (РП), элементИ и второй элемент И в последовательно соединенные второй фо{Яугарователь РП.и третий эл&мечт И, а также дополнительный блок сравнения, к входам которого подключены соответствующие выходы второго формирователя РП, а выход дополнительного блока сравнения подключен к первому входу второго формирователя РП, к второму входу которого подключен выход второго блока сравнения и первый вхо анализатора ошибок, к второму входу которого подключен третий вход второго формирователя РП, второй вход блока памяти и первый вход первого формировате ля РП, являющийся входом считывания ус ройства, к второму входу которого, являющемуся входом запись устройства, под- ключены четвертый вход второго формиро вателя РП и третьи входы блока памяти и анализатора оищбок, к четвертым входам которых подключен выход третьего элемента И, при этом к входам первого блока сравнения подключены соответствую щие выходы первого формирователя РП, а второй выход анализатора ошибок подключен к второму входу третьего , .элемента И, при этом выход коммутатора подключен к третьему входу первого формирователя РП. На фиг. 1 представлена структурноэлектрическая схема анализатора, на фиг. 2 - поясняющие его работу эпюры. Анализатор содержит коммутатор 1, второй блок 2 сравнения, первый блок 3 сравнения, дополнительный блок 4 сравне ния, первый элемент И 5, третий элемент И б, второй элемент И 7, блок 8 памяти, анализатор 9 ощибок, первый формирователь 10 рекуррентной последовательности (РП), второй формирователь РП 11, информационный вход 12, вход Считывание 13, выход 14,1-14 N формирователя (РП) 10, вход Запись 15 формирователь (РП) состоит из блоков 16.1-16 N памяти и регистра 17. Устройство работает следующим обраВходная информация (фиг. 2) с Я каналов, поступающая через коммутатор с входа 12 записывается сигналом запись (фиг. 2е) в блок 16.1 памяти формирователя 1О по соответствующим адресам (фиг. 2 а, в - с R). В следующем цикле (работа с теми же каналами) информация 3 блока 16,1 памяти .записывается последовательно в регистр 17 сигналом Считывание (фиг. 2 ), а сигналом Запись (фиг. 2е), осуществляется перезапись информации из регистра 17 в последующий блок 16.2 памяти. причем в блок 16.1 памяти тем же сигналом будет записан следующий бит входной информации, по адресам а, в - с R ) и т. д. (фиг. 2) до блока 16 N памяти включительно. То есть предыдущая информация из блока памяти 16.1, 16.2, 16 N с каждым шжлом по адресам а, в, с R (фт1г. 2) записывается последовательно в регистр 17 сигналом Считывание (фиг. 28) по входу 13, а сигналом Запись (фиг. 2е) по входу 12с выходов 14.1, 14,2, 14.Ы-1 регистра 17 производится перезапись в блоки памяти 16.2 16 N соответственно. Таким образом, происходит заполнение формирователя 10 входной информацией по R каналам. Одновременно на блоке 2 сравнения по каждому из адресов а, в - с R (фиг. 2) происходит сравнение побитно входной информации (фиг. 2 ) с входа 12 с информацией, находящейся в формирователе РП 10, и преобрагованной в рекуррентную последовательность через блок 3 сравнения, которая не совпадает с входной информацией. Следовательно, на выходе блока 2 сравнег-шя присутствуют сигналы несовпадения. После заполнения входной информации (фиг. 2i) формирователя РП 1О, с выхода блока 3 сравнения выдается рекуррентная последовательность, аналогичная входной. При совпадении входной информации с информацией блока 3 сравнения на заданном участке, на выходе блока сравне;.ия 2 отсутствуют сигналы несовпадений. Через определеннь1й промежуток времени выход блока 3 сравнения подключается через коммутатор 1 на вход формирователя РП 10, а блок 2 сравнения в этом случае осуществляет побитное сравнение входной информации -(фиг. 2 ) с рекуррентной последовательностью, с блока 3 сравнения. Формирователь РП 11 начинает пер&бор своей рекуррентной последовательности при отсутствии сигналов несовпадения через блок 4 сравнения индивидуально по каждому из адресов а, в с R (фиг. 2). Если входная ин4юрмация по определенным каналам имеет опережение или запаздывание относительно других каналов, то вхождение в синхронизм и начало работы формирователя РП 11 идет с опережением и запаздыванием по соответствующим каналам. Конец рекуррентных последовательностей формирователя РП 11 по каждому 5Q4 из R каналов дешифруется элементом И 6, исходя из заданной длительности неискаженного участка входной рекур рентной последовательности. С выхода элемента И 6 сигналы конца рекуррен ты устанавливают в исходное состояние анализатор 9 ошибок т/ по соответствующим адресам переключают ячейки в блоке 8 памяти. По сигналам с выхода блока 8 памяти через коммутатор 1 рекуррентная последовательность с блока 3 сравнения записывается в блок 16.1 памяти и работа происходит аналогично записи входной информации. Следовательно, формирователь РП 1О совместно с блоком 3 сравнения через коммутатор 1 формирует R рекуррентных последовательностей по R каналам, авто номно по каждому каналу с одним из адресов, а, в-с (1), а, в-с (II) и т. д. (фиг. 2). Блок 2 сравнения при подключении выхода блока 3 сравнения через коммутатор 1 на вход формирователя РП 1О осуществляет побитное сравнение входной информации (фиг. 2 f ) с рекуррентнь1ми последовательностями из формирователя РП 10 и блока 3 сравнения. Конец фазового пуска формирователя РП 10 по каждому из R каналов дешифри руется элементом И 5 и выдается через элемент И 7 на выход соответственно адресам а, в - с R (фиг. 2). В случае вхождения в синхронизм с аналогичной рекуррентной последовв ельКрстью ненужнсч радиостаншга на выходе блока 2 сравнения присутствуют сигналы несовпадения по данному каналу, которые фиксируются анализатором 9 ошибок. При определегпой последовательности сигналов несовпадения анализатор 9 ошибок по данному каналу выдает сигнал на вход блока 8 памяти. Вход формтфователя РП 10 через -коммутатор 1 подклю--чается к информационному входу 12. С выхода анализатора 9 ошибок по данному каналу вьщается сигнал на второй вход элагента И 7 для блокировки выхода фазового пуска. В исходное положение устройство уста навливается по сигналам несовпадени;я с блока 2 сравнения. Поэтому если на выходе 12 рекуррентная последовательност отличается от рекуррентной последовател кости, формируемой на выходе блока 3 сравнения, то на выходе блока 2 сравне- ния присутствуют сигналы несовпадения. 86 причем в анализаторе 9 ошибок происходит анализ количества несовпадения и их последовательности и, если входная рекуррента отлична от формируемой, проиоходит переключение входа 12 устррйства на вход формирователя РП 1О через коммутатор 1. Когда на информационный вход 12 поступает информация по одному или R каналов, блок 2 сравнения выдает, сигналы несовпадения по соответствующим каналам, так как формирователь РП 1О находится в нулевом состоянии (предыдущая информация состояла из нулей). .Сигналы несовпадения устанавливают формирователь РП 11 в исходное состояние, и одновременно они подсчитываются в анализаторе 9 ошибок. Последний фиксирует смену входной рекуррентной последовательности и выдает в блок 8 памяти, который подключает информационный вход 12 через коммутатор 1 к входу формирователя РП 10. На вход 13 устройства подаются сигкалы считывания (фиг. 2d), а к входу 15 подводятся разряды адреса а, в - с и сигналы записи (фиг. 2 е ), которые формируются с частотной, равной прини ма,емой информации. Возможкое количество обрабатываемь1х каналов зависит от выбранной длительности на один какал. В предлагаемом устройстве полностью реализуется функции известных анализаторов, кроме того, с введением многоканальных формирователей появилась возможность увеличить количество рабочих каналов от одного до 64-128, причем рекуррентная поспедователькость формируется индивидуально по каждок каналу и зависит только от входной информации. Каждый канал имеет фиксированное время работы, которое определяется адресом на данный канал. Также имеется возможность работы на разных скоростях (1,2 кГи-9,6 кГп), это достигается при определенно сформированном сигнале запись, соответствующем частоте принимаемой информации. Формула изобретения Многоканальный анализатор рекурренттзго сигнала фазового пуска, содержащий посл адовательно соединенные анализатор ощибсж, блсяс памяти и KoivtMyrarop, к второму входу которого подключен вы- ход первого блока сравнения и первый вход второго бл(жа сравнения, второй - ;

вход которого объединен с третьим входом коммутатора и является инфа{ аш1онным входом устройства, отличаюш и и с,.я тал, что, с пелью сокращения времени анализа рекуррентного сигнала, введены последовательно соединенные первый 4ю|ямпнрователь рекуррентной по./следоватедьносги(РП), первый элемент И В второй вп&лввт И и последова ельно соединенные второй формирователь РП и третий элемент И, а также дополнитель ный блок сравне1шя, к входам которого подключены соответствующие выходь вто ррго фор шрстателя РП, а выход дополнительного блока сравнения подключен к первому входу второго фррмиррвателя

РП, к второму входу которого подключен выход второго блоки сравнения и первый вход .анализатора ощибок, к второму входу которого подключен третий вход второго формирователя РП, второй вход

блока памяти и первый вход первого формирователя РП, являющийся входом Считывание устройства, к второму входу которого, являющемуся входомЗапись устройства, подключен четвертый вход второго формирователя РП и третьи входы блока памяти и а1шлизатора ощибок, к четвертым входам которых подключен выход третьего элемента И, при этом к входам первого блока сравнения подключены соответствующие выходы первого формирователя РП, а второй выход анализатора ощвбок подключен к второму входу третьего элемента И, при этом выход коммутатора подключен к третьему входу первого формирователя РП.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР Ма 62863О, кл, Н 041. 7/10, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Анализатор рекуррентного сигнала фазового пуска | 1981 |

|

SU995361A2 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для выделения рекуррентныхСигНАлОВ фАзОВОгО пуСКА B МНОгОКАНАльНыХ СиСТЕМАХ СВязи | 1979 |

|

SU849519A2 |

| Устройство для приема и передачииНфОРМАции C пОдВижНыХ Об'ЕКТОВ | 1977 |

|

SU842910A1 |

| Устройство фазового пуска | 1986 |

|

SU1415447A2 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Обнаружитель комбинаций двоичных сигналов | 1986 |

|

SU1325724A1 |

9

Г

U.

fc/

ЙЙЙЯЙА

JttA

I

4 у У Ъ

«

«d3

Ш

т ff

/J

&г

1S.1

4Z

Ж

ff

HJ

4

- XI

l

X

1

So

So

L

t

(1

I

-Д

isf

j «Л

I

д.

- L-l

a

Ч,

tb

Авторы

Даты

1982-07-15—Публикация

1980-02-21—Подача