(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ

1

Изобретение относится к запоминающим устройствам.

известно устройство для контроля блоков памяти, содержащее блок управления, блок сравнения, блок формирования адресов, блок анализа, блок регистрации, блоки памяти 1 .

Недостатками устройства являются больщие аппаратурное затраты.

Наиболее близким по техническому решению к предложенному является устройство для контроля постоянных запоминающих устройств (ПЗУ), содержащее последовательно соединенные дешифратор адреса и коммутатор, подключенный к блоку анализа ошибок, адресному счетчику, к входу и выходу проверяемого устройства, к входу и выходу эталонного устройства, генератору синхроимйульсов, вход которого подключен к блоку управления, подключенного к блоку анализа ошибок и адресному счетчику, позволяющее проверять ПЗУ тремя методами: методом контрольного суммирования, методом сравнения с контрольной перфокартой и методом сравнения с эталонным устройством 2.

Недостатками этого устройства являются низкие достоверность контроля и быстродействие, так как быстродействие устройства ограничено скоростью ввода перфокарты

5 и скоростью контрольного суммирования, что не позволяет проверять ПЗУ на их рабочей частоте.

Цель изобретения - повышение достоверности контроля путем обеспечения контроля ПЗУ методами суммирования по модулю три, сравнения с контрольной перфолентой и с эталонной информацией на рабочей частоте.

Поставленная цель достигается тем, что в устройство для контроля блоков постоян,5 ной памяти, содержащее счетчик адреса, дешифратор адреса, блок управления, коммутатор, блок ввода информации, блок анализа ошибок и генератор синхросигналов, выход которого подключен к первому входу коммутатора, второй вход которого соединен

20 с выходом счетчика адреса и входом дешифратора адреса, выход которого подключен к третьему входу коммутатора, одни из выходов которого соединены с информационными входами блока анализа ошибок.

управляющие входы и выходы которого подключены соответственно к первым выходу и входу блока управления, вторые вход и выход которого соединены соответственно с первым выходом и входом блока ввода информации, второй выход которого подключен к четвертому входу коммутатора, Третий и четвертый выходы блока управления соединены соответственно с входом счетчика адреса и входом генератора синхросигналов, введены формирователь сигналов цикла, блок свертки по модулю три и регистр контрольной информации, вход которого соединен с другим выходом коммутатора, а выход - с эталонным входом блока анализа ошибок и первым входом блока свертки по модулю три, второй вход которого подключен к второму выходу счетчика адреса, а третий вход и выход подключены соответственно к пятому выходу блока управления и контрольным входам блока анализу ошибок, первый вход формирователя сигналов цикла соединен с первым выходом счетчика адреса, а второй вход и выход подключены соответственно .к шестому выходу и третьему входу блока управления.

Формирователь сигналов цикла содержит первую схему сравнения, элементы И, элементы задержки и регистр адреса, выходы которого подключены к одним из входов первой схемы сравнения, выход которой соединен с первыми входами элементов И, выход первого элемента И подключен к входам первого и второго элементов задержки, выходы которых, выход первой схемы сравнения и выход второго элемента И являются выходами формирователя, входами которого являются другие входы первой схемы сравнения и вторые входы элементов И.

Блок анализа ошибок содержит сумматор по модулю два, вторую, третью и четвертую схемы сравнения, регистр неисправностей, элементы И с третьего по девятый, элемент НЕ, элементы, индикации и элементы ИЛИ, причем входы первого и второго элементов индикации подключены соответственно к одним из входов второй и третьей схем сравнения, выход первого элемента ИЛИ соединен с входами третьего элемента индикации и одними из входов четвертой схемы сравнения, первые входы третьего и четвертого элементов И подключены соответственно к выходам третьей и четвертой схем сравнения, первые входы пятого и шестого элементов И соединены с выходом второй схемы сравнения, другие входы которой подключены к входам четвертого элемента индикации и выходу второго элемента ИЛИ, первый вход которого соединен с выходом седьмого элемента И, входы пятого и шестого элементов индикации подключены соответственно к другим входам третьей и четвертой -схем сравнения, вход седьмого элемента индикации соединен с выходом сумматора по модулю два и первым входом седьмого элемента И, второй вход которого подключен к второму входу пятого элемента И и входу элемента НЕ, выход которого

соединен с вторым входом шестого элемента И, выходы элементов И, с третьего по шестой подключены к одним из входов регистра неисправностей, одни из выходов которого соединены соответственно с входом восьмого элемента индикации и первым входом восьмого элемента И, выход девятого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого, одни из входов второй и третьей схем сравнения, входы сумматора по модулю два, другие входы регистра неисправностей и вторые входы седьмого и восьмого элементов И являются информационными входами блока, эталонным входом которого является второй вход второго элемента ИЛИ, вторые входы третьего и четвертого элементов И, третьи

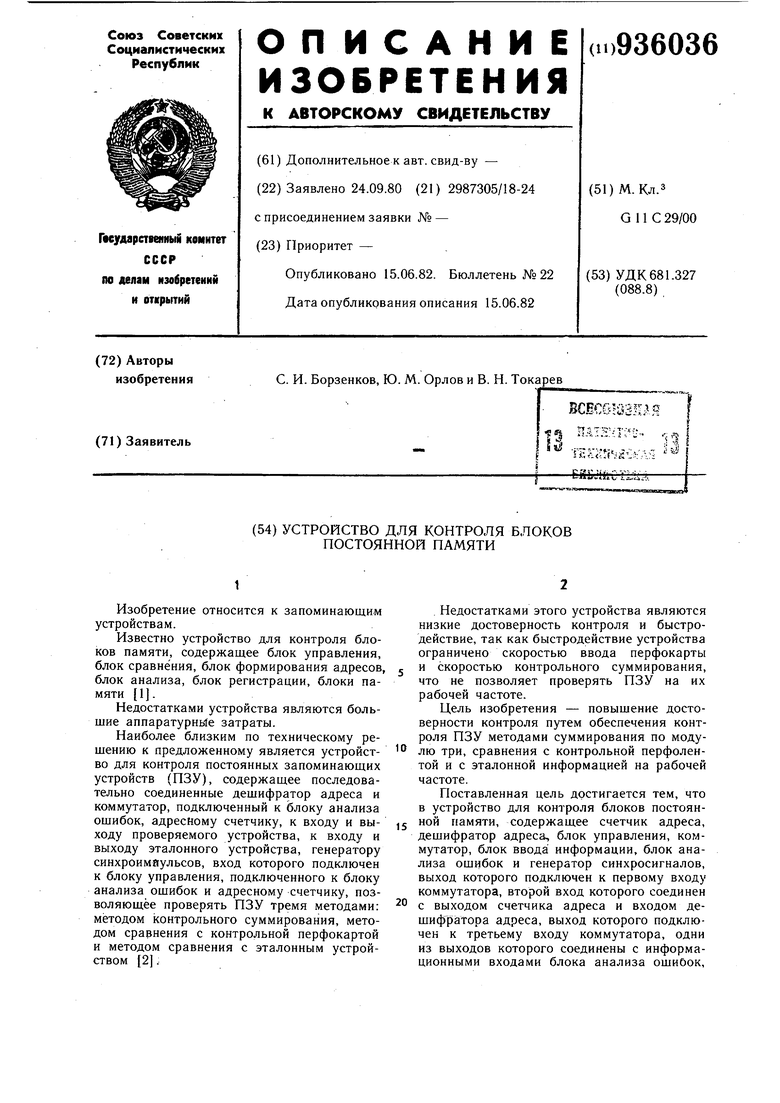

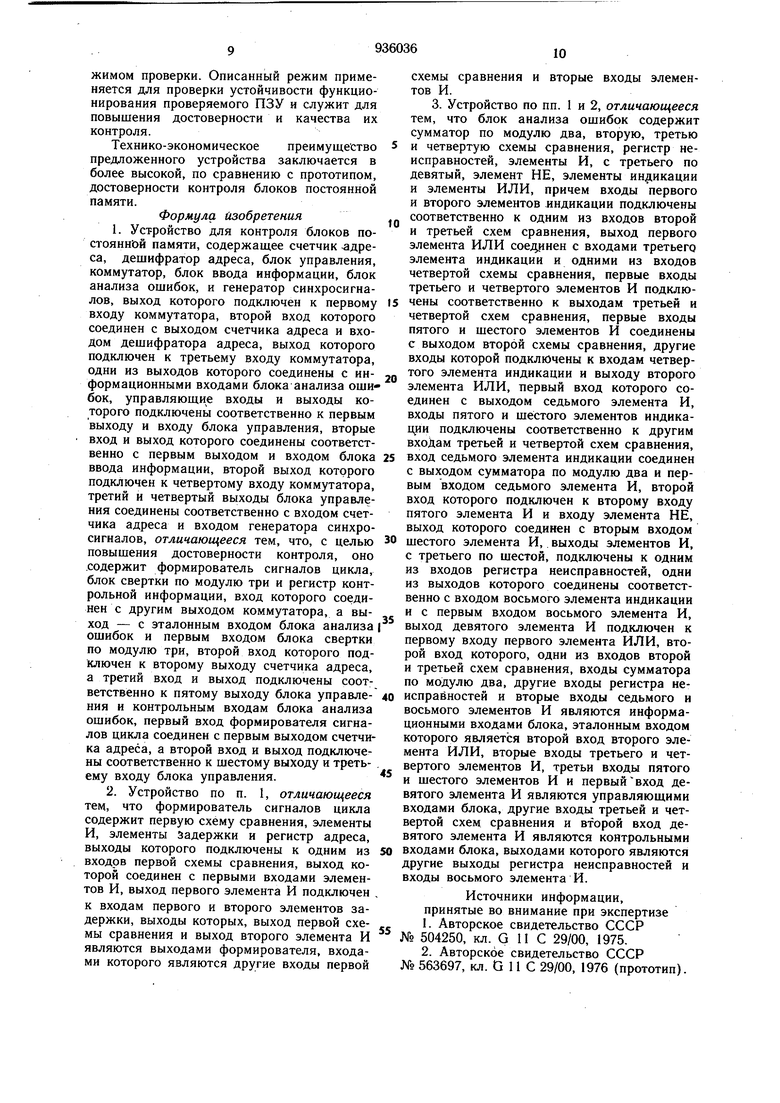

входы пятого и шестого элементов И и первый вход девятого элемента И являются управляюшими входами блока, другие входы третьей и четвертой схем сравнения и второй вход девятого элемента И являются контрольными входами блока, выходами которого являются другие выходы регистра неисправностей и выход восьмого элемента И. На фиг. 1 представлена функциональная схема предложенного устройства; на фиг. 2 функциональная схема формирователя сигналов цикла; на фиг. 3 - функциональная схема блока анализа ошибок; на фиг. 4 - функциональная схема блока управления. Предложенное устройство содержит (см. фиг. 1) счетчик 1 адреса, дешифратор 2 адреса, формирователь 3 сигналов цикла,

5 блок. 4 свертки по модулю три, предназначенный для выработки контрольных кодов, блок 5 управления, коммутатор 6, блок 7 ввода информации, регистр 8 контрольной информации, блок 9 анализа ошибок и генед ратор 10 синхросигналов.

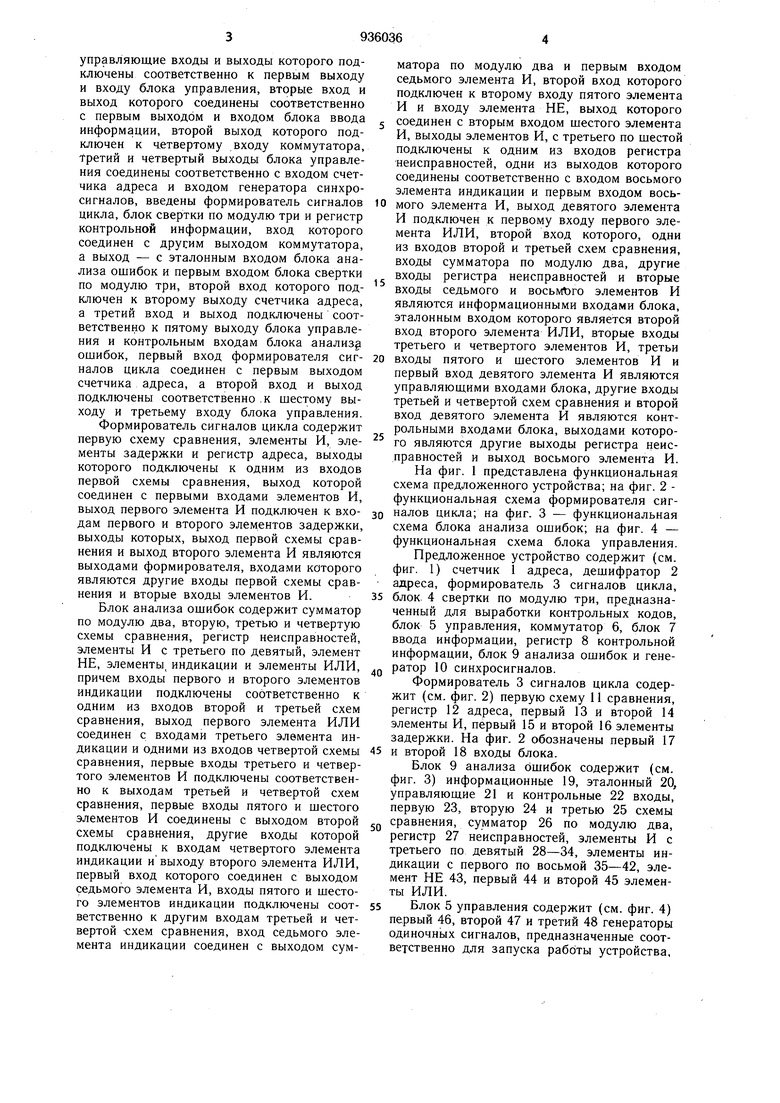

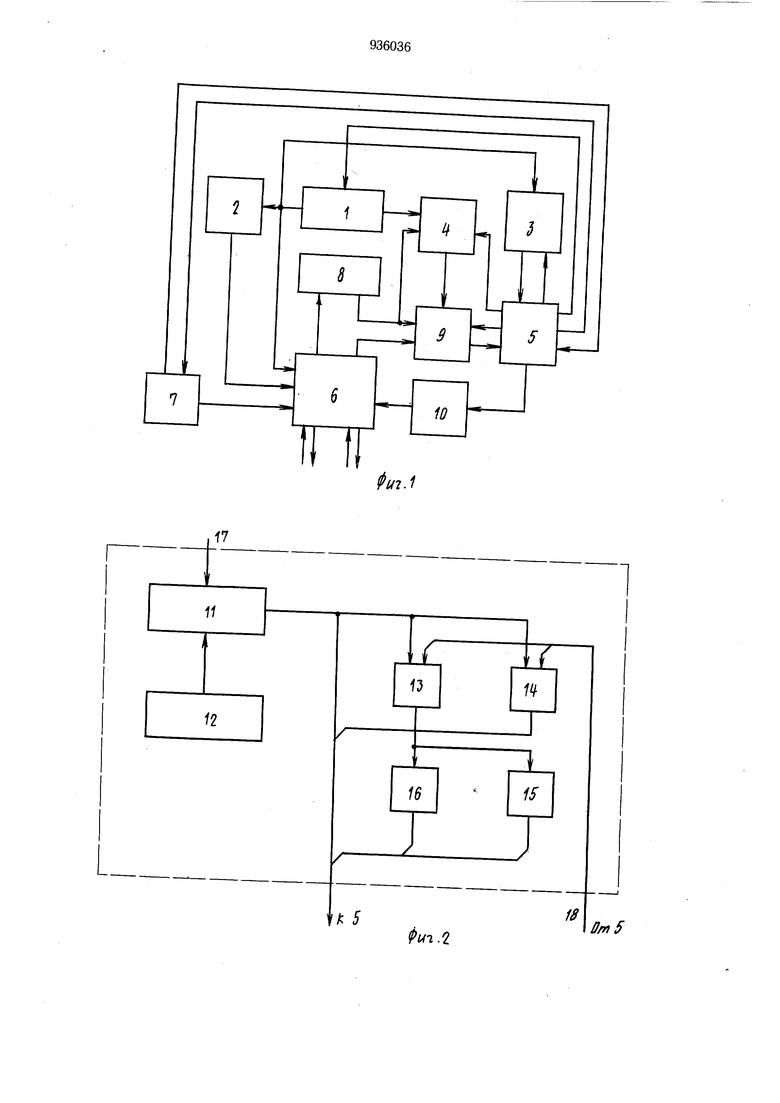

Формирователь 3 сигналов цикла содержит (см. фиг. 2) первую схему 11 сравнения, регистр 12 адреса, первый 13 и второй 14 элементы И, первый 15 и второй 16 элементы задержки. На фиг. 2 обозначены первый 17

5 и второй 18 входы блока.

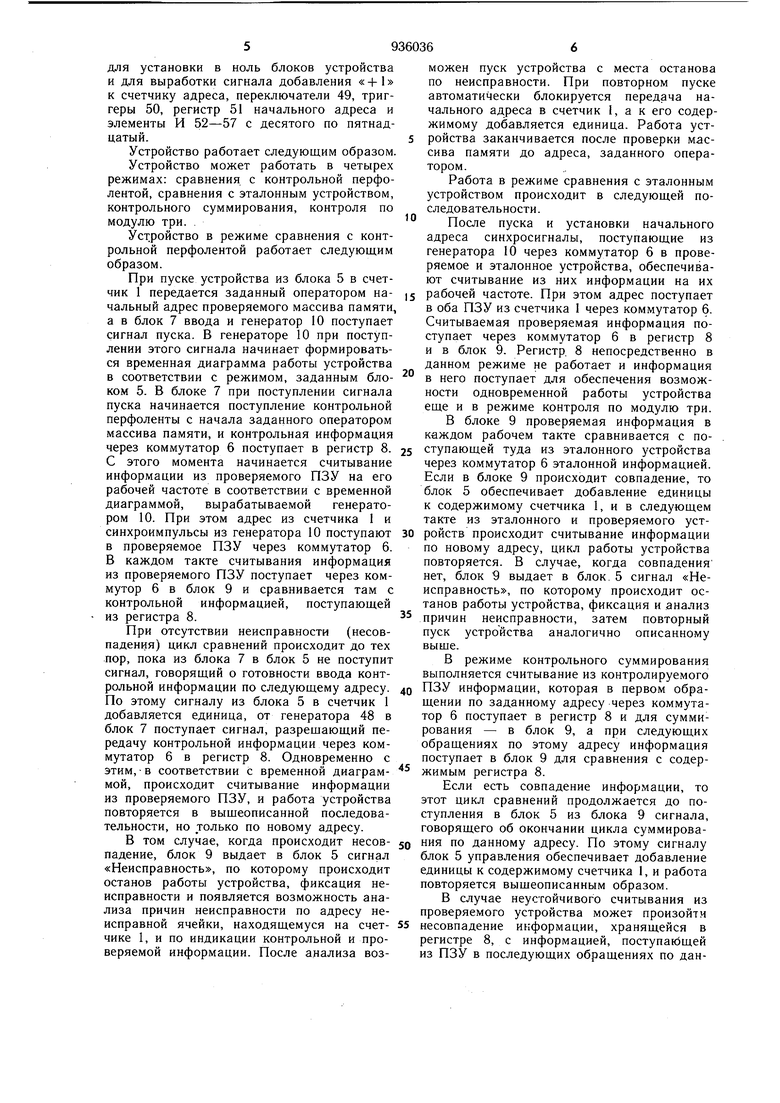

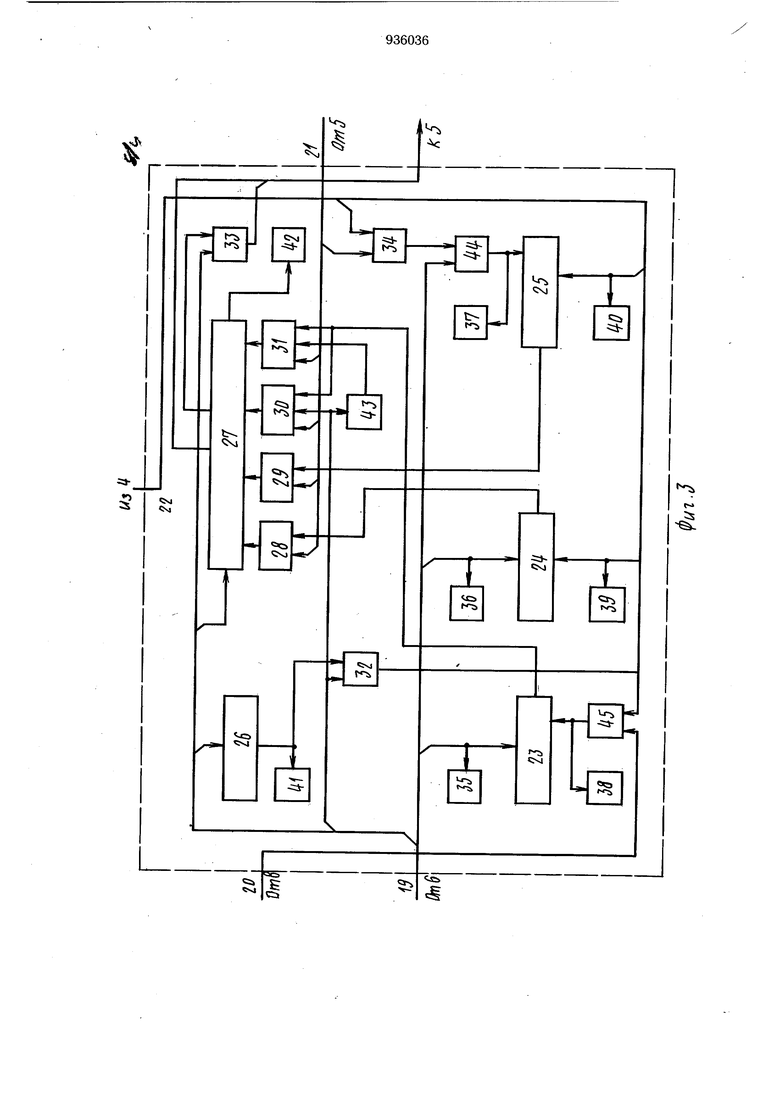

Блок 9 анализа ошибок содержит (см. фиг. 3) информационные 19, эталонный 20, управляющие 21 и контрольные 22 входы, первую 23, вторую 24 и третью 25 схемы

сравнения, сумматор 26 по модулю два, регистр 27 неисправностей, элементы И с третьего по девятый 28-34, элементы индикации с первого по восьмой 35-42, элемент НЕ 43, первый 44 и второй 45 элементы ИЛИ.

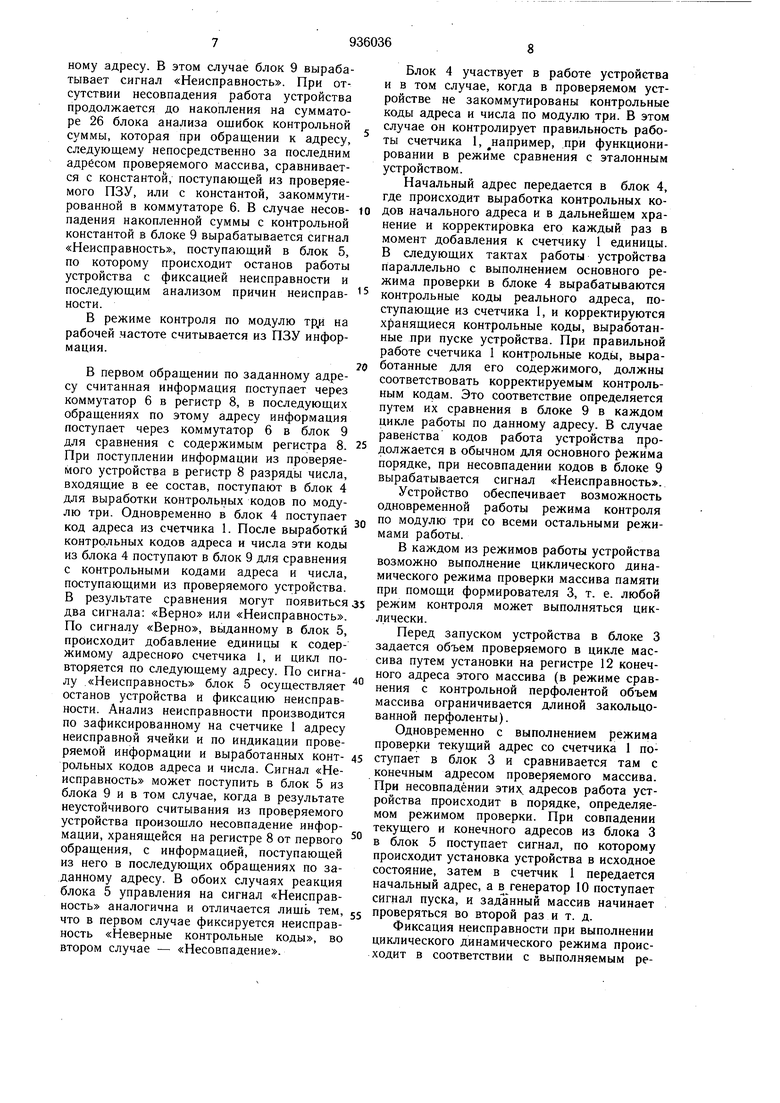

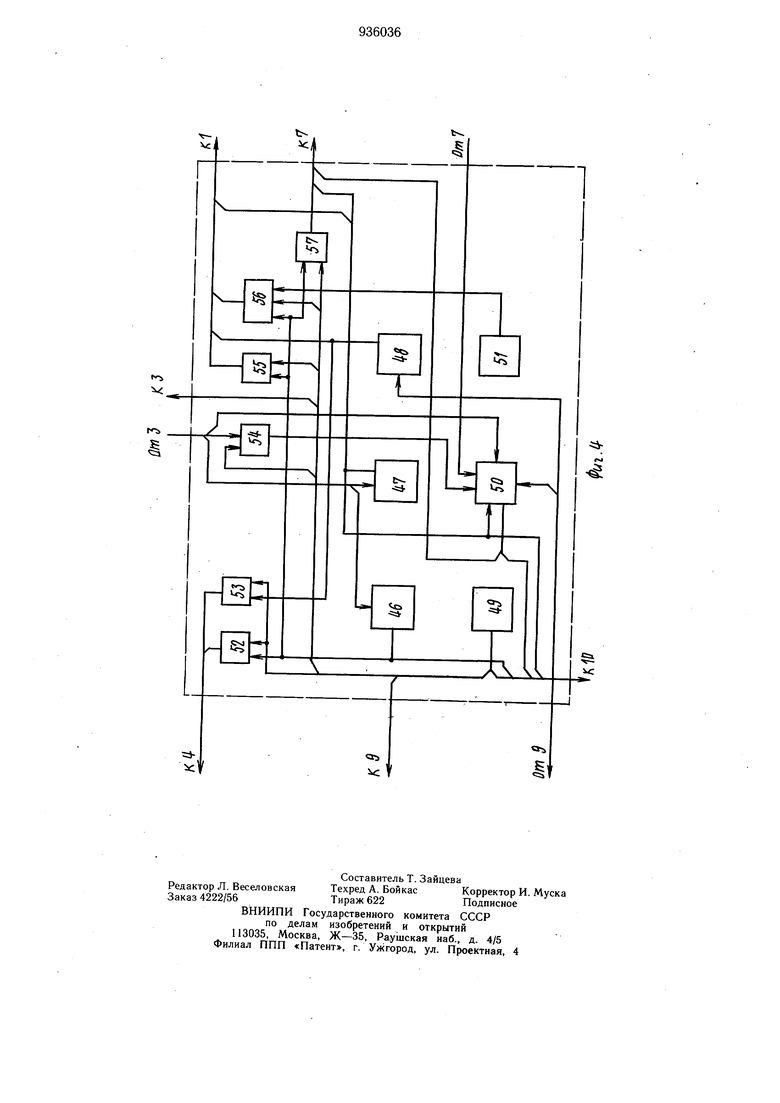

5 Блок 5 управления содержит (см. фиг. 4) первый 46, второй 47 и третий 48 генераторы одиночных сигналов, предназначенные соответственно для запуска работы устройства. ДЛЯ установки в ноль блоков устройства и для выработки сигнала добавления «+1 к счетчику адреса, переключатели 49, триггеры 50, регистр 51 начального адреса и элементы И 52-57 с десятого по пятнадцатый. Устройство работает следующим образом. Устройство может работать в четырех режимах: сравнения с контрольной перфолентой, сравнения с эталонным устройством, контрольного суммирования, контроля по модулю три. . Устройство в режиме сравнения с контрольной перфолентой работает следующим образом. При пуске устройства из блока 5 в счетчик 1 передается заданный оператором начальный адрес проверяемого массива памяти, а в блок 7 ввода и генератор 10 поступает сигнал пуска. В генераторе 10 при поступлении этого сигнала начинает формироваться временная диаграмма работы устройства в соответствии с режимом, заданным блоком 5. В блоке 7 при поступлении сигнала пуска начинается поступление контрольной перфоленты с начала заданного оператором массива памяти, и контрольная информация через коммутатор 6 поступает в регистр 8. С этого момента начинается считывание информации из проверяемого ПЗУ на его рабочей частоте в соответствии с временной диаграммой, вырабатываемой генератором 10. При этом адрес из счетчика 1 и синхроимпульсы из генератора 10 поступают в проверяемое ПЗУ через коммутатор 6. В каждом такте считывания информация из проверяемого ПЗУ поступает через коммутор 6 в блок 9 и сравнивается там с контрольной информацией, поступающей из регистра 8. При отсутствии неисправности (несовпадения) цикл сравнений происходит до тех пор, пока из блока 7 в блок 5 не поступит сигнал, говорящий о готовности ввода контрольной информации по следующему адресу. По этому сигналу из блока 5 в счетчик 1 добавляется единица, от генератора 48 в блок 7 поступает сигнал, разрешающий передачу контрольной информации через коммутатор 6 в регистр 8. Одновременно с этим, в соответствии с временной диаграммой, происходит считывание информации из проверяемого ПЗУ, и работа устройства повторяется в вышеописанной последовательности, но только по новому адресу. В том случае, когда происходит несовпадение, блок 9 выдает в блок 5 сигнал «Неисправность, по которому происходит останов работы устройства, фиксация неисправности и появляется возможность анализа причин неисправности по адресу неисправной ячейки, находящемуся на счетчике 1, и по индикации контрольной и проверяемой информации. После анализа возможен пуск устройства с места останова по неисправности. При повторном пуске автоматически блокируется передача начального адреса в счетчик 1, а к его содержимому добавляется единица. Работа устройства заканчивается после проверки массива памяти до адреса, заданного оператором. Работа в режиме сравнения с эталонным устройством происходит в следующей последовательности. После пуска и установки начального адреса синхросигналы, поступающие из генератора 10 через коммутатор 6 в проверяемое и эталонное устройства, обеспечивают считывание из них информации на их рабочей частоте. При этом адрес поступает в оба ПЗУ из счетчика 1 через коммутатор 6. Считываемая проверяемая информация поступает через коммутатор 6 в регистр 8 и в блок 9. Регистр. 8 непосредственно в данном режиме не работает и информация в него поступает для обеспечения возможности одновременной работы устройства еще и в режиме контроля по модулю три. В блоке 9 проверяемая информация в каждом рабочем такте сравнивается с поступающей туда из эталонного устройства через коммутатор 6 эталонной информацией. Если в блоке 9 происходит совпадение, то блок 5 обеспечивает добавление единицы к содержимому счетчика 1, и в следующем такте из эталонного и проверяемого устройств происходит считывание информации по новому адресу, цикл работы устройства повторяется. В случае, когда совпадения нет, блок 9 выдает в блок. 5 сигнал «Неисправность, по которому происходит останов работы устройства, фиксация и анализ причин неисправности, затем повторный пуск устройства аналогично описанному выше. В режиме контрольного суммирования выполняется считывание из контролируемого ПЗУ информации, которая в первом обращении по заданному адресу через коммутатор 6 поступает в регистр 8 и для суммирования - в блок 9, а при следующих обращениях по этому адресу информация поступает в блок 9 для сравнения с содержимым регистра 8. Если есть совпадение информации, то этот цикл сравнений продолжается до поступления в блок 5 из блока 9 сигнала, говорящего об окончании цикла суммирования по данному адресу. По этому сигналу блок 5 управления обеспечивает добавление единицы к содержимому счетчика 1, и работа повторяется вышеописанным образом. В случае неустойчивого считывания из проверяемого устройства может произойти несовпадение информации, хранящейся в регистре 8, с информацией, поступак5щей из ПЗУ в последующих обращениях по данному адресу. В этом случае блок 9 вырабатывает сигнал «Неисправность. При отсутствии несовпадения работа устройства продолжается до накопления на сумматоре 26 блока анализа ошибок контрольной суммы, которая при обращении к адресу, следующему непосредственно за последним адресом проверяемого массива, сравнивается с константой, поступающей из проверяемого ПЗУ, или с константой, закоммутированной в коммутаторе 6. В случае несовпадения накопленной суммы с контрольной константой в блоке 9 вырабатывается сигнал «Неисправность, поступающий в блок 5, по которому происходит останов работы устройства с фиксацией неисправности и последующим анализом причин неисправности. В режиме контроля по модулю тр,и на рабочей частоте считывается из ПЗУ информация. В первом обращении по заданному адресу считанная информация поступает через коммутатор 6 в регистр 8, в последующих обращениях по этому адресу информация поступает через коммутатор 6 в блок 9 для сравнения с содержимым регистра 8. При поступлении информации из проверяемого устройства в регистр 8 разряды числа, входящие в ее состав, поступают в блок 4 для выработки контрольных кодов по модулю три. Одновременно в блок 4 поступает код адреса из счетчика 1. После выработки контрольных кодов адреса и числа эти коды из блока 4 поступают в блок 9 для сравнения с контрольными кодами адреса и числа, поступающими из проверяемого устройства. В результате сравнения могут появиться два сигнала: «Верно или «Неисправность. По сигналу «Верно, выданному в блок 5, происходит добавление единицы к содержимому адресного счетчика 1, и цикл повторяется по следующему адресу. По сигналу «Неисправность блок 5 осуществляет останов устройства и фиксацию неисправности. Анализ неисправности производится по зафиксированному на счетчике 1 адресу неисправной ячейки и по индикации проверяемой информации и выработанных контрольных кодов адреса и числа. Сигнал «Неисправность может поступить в блок 5 из блока 9 и в том случае, когда в результате неустойчивого считывания из проверяемого устройства произошло несовпадение информации, хранящейся на регистре 8 от первого обращения, с информацией, поступающей из него в последующих обращениях по заданному адресу. В обоих случаях реакция блока 5 управления на сигнал «Неисправность аналогична и отличается лишь тем, что в первом случае фиксируется неисправность «Неверные контрольные коды, во втором случае - «Несовпадение. Блок 4 участвует в работе устройства и в том случае, когда в проверяемом устройстве не закоммутированы контрольные коды адреса и числа по модулю три. В этом случае он контролирует правильность работы счетчика 1, например, при функционировании в режиме сравнения с эталонным устройством. Начальный адрес передается в блок 4, где происходит выработка контрольных кодов начального адреса и в дальнейшем хранение и корректировка его каждый раз в момент добавления к счетчику 1 единицы. В следующих тактах работы устройства параллельно с выполнением основного режима проверки в блоке 4 вырабатываются контрольные коды реального адреса, поступающие из счетчика I, и корректируются хранящиеся контрольные коды, выработанные при пуске устройства. При правильной работе счетчика 1 контрольные кодь1, выработанные для его содержимого, должны соответствовать корректируемым контрольным кодам. Это соответствие определяется путем их сравнения в блоке 9 в каждом цикле работы по данному адресу. В случае равенства кодов работа устройства продолжается в обычном для основного режима порядке, при несовпадении кодов в блоке 9 вырабатывается сигнал «Неисправность. Устройство обеспечивает возможность одновременной работы режима контроля по модулю три со всеми остальными режимами работы. В каждом из режимов работы устройства возможно выполнение циклического динамического режима проверки массива памяти при помощи формирователя 3, т. е. любой режим контроля может выполняться циклически. Перед запуском устройства в блоке 3 задается объем проверяемого в цикле массива путем установки на регистре 12 конечного адреса этого массива (в режиме сравнения с контрольной перфолентой объем массива ограничивается длиной закольцованной перфоленты). Одновременно с выполнением режима проверки текущий адрес со счетчика 1 поступает в блок 3 и сравнивается там с конечным адресом проверяемого массива. При несовпадении этих, адресов работа устройства происходит в порядке, определяемом режимом проверки. При совпадении текущего и конечного адресов из блока 3 в блок 5 поступает сигнал, по которому происходит установка устройства в исходное состояние, затем в счетчик 1 передается начальный адрес, а в генератор 10 поступает сигнал пуска, и заданный массив начинает проверяться во второй раз и т. д. Фиксация неисправности при выполнении циклического динамического режима происходит в соответствии с выполняемым режимом проверки. Описанный режим применяется для проверки устойчивости функционирования проверяемого ПЗУ и служит для повышения достоверности и качества их контроля. Технико-экономическое преимущество предложенного устройства заключается в более высокой, по сравнению с прототипом, достоверности контроля блоков постоянной памяти. Формула изобретения 1.Устройство для контроля блоков постоянной памяти, содержащее счетчик адреса, дешифратор адреса, блок управления, коммутатор, блок ввода информации, блок анализа ошибок, и генератор синхросигналов, выход которого подключен к первому входу коммутатора, второй вход которого соединен с выходом счетчика адреса и входом дешифратора адреса, выход которого подключен к третьему входу коммутатора, одни из выходов которого соединены с информационными входами блока анализа ошибок, управляющие входы и выходы которого подключены соответственно к первым выходу и входу блока управления, вторые вход и выход которого соединены соответственно с первым выходом и входом блока ввода информации, второй выход которого подключен к четвертому входу коммутатора, третий и четвертый выходы блока управления соединены соответственно с входом счетчика адреса и входом генератора синхросигналов, отличающееся тем, что, с целью повышения достоверности контроля, оно .содержит формирователь сигналов цикла, блок свертки по модулю три и регистр контрольной информации, вход которого соединен с другим выходом коммутатора, а выход - с эталонным входом блока анализа ошибок и первым входом блока свертки по модулю три, второй вход которого подключен к второму выходу счетчика адреса, а третий вход и выход подключены соответственно к пятому выходу блока управления и контрольным входам блока анализа ошибок, первый вход формирователя сигналов цикла соединен с первым выходом счетчика адреса, а второй вход и выход подключены соответственно к шестому выходу и третьему входу блока управления. 2.Устройство по п. 1, отличающееся тем, что формирователь сигналов цикла содержит первую схему сравнения, элементы И, элементы задержки и регистр адреса, выходы которого подключены к одним из входов первой схемы сравнения, выход которой соединен с первыми входами элементов И, выход первого элемента И подключен к входам первого и второго элементов задержки, выходы которых, выход первой схемы сравнения и выход второго элемента И являются выходами формирователя, входами которого являются другие входы первой схемы сравнения и вторые входы элементов И. 3. Устройство по пп. 1 и 2, отличающееся тем, что блок анализа ошибок содержит сумматор по модулю два, вторую, третью и четвертую схемы сравнения, регистр неисправностей, элементы И, с третьего по девятый, элемент НЕ, элементы индикации и элементы ИЛИ, причем входы первого и второго элементов лндикации подключены соответственно к одним из входов второй и третьей схем сравнения, выход первого элемента ИЛИ соединен с входами третьего элемента индикации и одними из входов четвертой схемы сравнения, первые входы третьего и четвертого элементов И подключены соответственно к выходам третьей и четвертой схем сравнения, первые входы пятого и шестого элементов И соединены с выходом второй схемы сравнения, другие входы которой подключены к входам четвертого элемента индикации и выходу второго элемента ИЛИ, первый вход которого соединен с выходом седьмого элемента И, входы пятого и шестого элементов индикац,ии подключены соответственно к другим входам третьей и четвертой схем сравнения, вход седьмого элемента индикации соединен с выходом сумматора по модулю два и первым входом седьмого элемента И, второй вход которого подключен к второму входу пятого элемента И и входу элемента НЕ, выход которого соединен с вторым входом шестого элемента И, выходы элементов И, с третьего по шестой, подключены к одним из входов регистра неисправностей, одни из выходов которого соединены соответственно с входом восьмого элемента индикации и с первым входом восьмого элемента И, выход девятого элемента И подключен к первому входу первого элемента ИЛИ, второй вход которого, одни из входов второй и третьей схем сравнения, входы сумматора по модулю два, другие входы регистра неисправностей и вторые входы седьмого и восьмого элементов И являются информационными входами блока, эталонным входом которого является второй вход второго элемента ИЛИ, вторые входы третьего и четвертого элементов И, третьи входы пятого и шестого элементов И и первыйвход девятого элемента И являются управляющими входами блока, другие входы третьей и четвертой схем сравнения и второй вход девятого элемента И являются контрольными входами блока, выходами которого являются другие выходы регистра неисправностей и входы восьмого элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 504250, кл. G 11 С 29/00, 1975. 2.Авторское свидетельство СССР № 563697, кл. G 11 С 29/00, 1976 (прототип).

(

hTi

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Многоканальное устройство для контроля памяти | 1984 |

|

SU1238164A1 |

| Устройство для контроля памяти | 1984 |

|

SU1236558A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1173449A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1336020A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

Авторы

Даты

1982-06-15—Публикация

1980-09-24—Подача