(54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1157545A1 |

| Устройство для управления ленточным перфоратором | 1981 |

|

SU970402A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для вывода информации | 1984 |

|

SU1238090A1 |

| Устройство для приема и обработки информации в многорегистровых кодах | 1982 |

|

SU1049951A1 |

| Устройство для управления ленточным перфоратором | 1982 |

|

SU1049934A1 |

| Устройство для управления ленточным перфоратором | 1979 |

|

SU860099A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

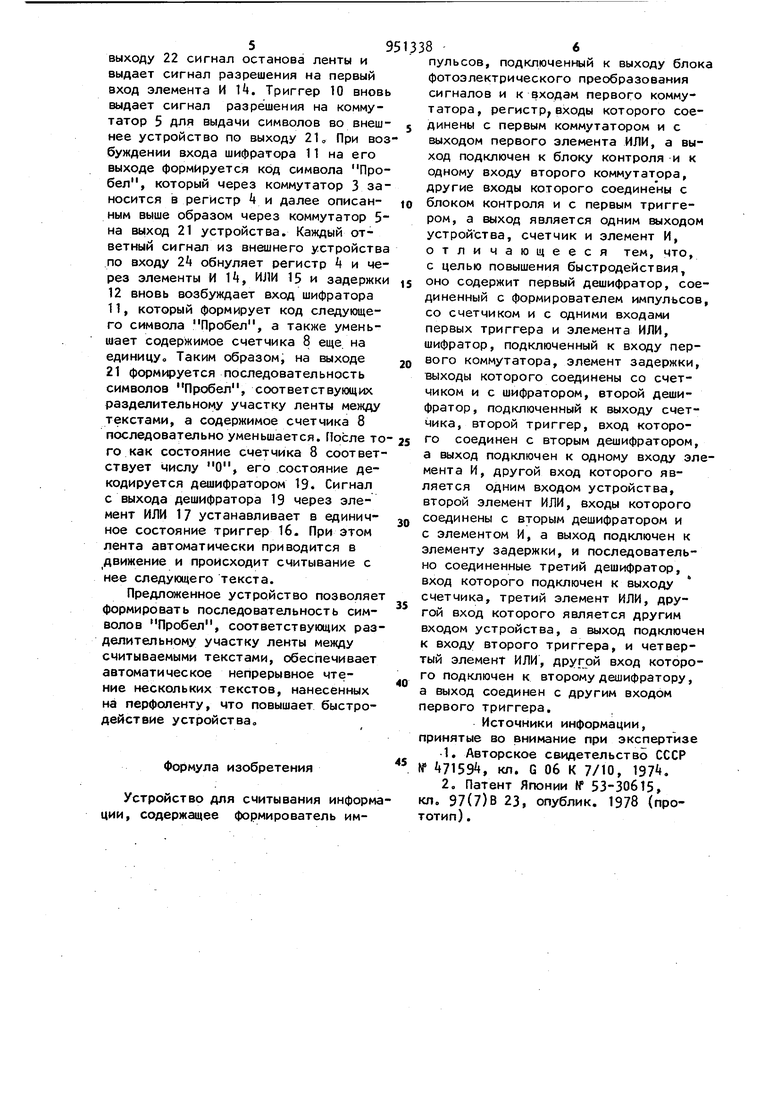

Изобретение относится к автоматике и вычислительной технике, в ча стности к устройствам для считывания информации и может быть исполь зовано при построении устройств вво да информации с перфоленты Известны устройства для считывания информации, содержащие фотоэлек рический блок, формирователь импуль сов, регистр и блок контроля ГП. Недостаток данных устройств состоит в их невысоком быстродействии. Известно устройство для считывания информации, содержащее блок фотоэлектрического преобразования, выход которого подключен к формирователю импульсов, соединенного с первыми коммутатором и дешифратором регистр, -второй коммутатор, блок контроля, счетчик и элемент И 2. Недостаток данного устройства заключается в его невысоком быстродействии. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее формирователь импульсов, подключенный к выходу блока фотоэлектрического преобразования сигналов и к входам первого коммутатора, регистр, входы которого соединены с первым коммутатором и с выходом первого элемента ИЛИ, а выход подключен к блоку контроля и к одному входу второго коммутатора, другие входы которого соединены с блоком контроля и с первым триггером, а выход является одним выходом устройства, счетчик и элемент И, введены первый дешифратор, соединенный с формирователем импульсов, со счетчиком и с одними входами первых триггера и элемента ИЛИ, шифратор, подключенный к входу первого коммутатора, элемент задержки, выходы которого соединены со счет чиком и с шифратором, второй дешифра39тор, подключенный к выходу счетчика второй триггер, вход которого соединен с вторым дешифратором, а выход подключен к одному входу элемента И другой вход которого является одним входом устройства, второй-элемент ИЛИ входы которого соединены с вторым дешифратором и с элементом И, а выход подключен к элементу задержки, последовательно соединенные третий дешифратор, вход которого подключен к выходу счетчика, третий элемент ИЛИ, другой вход которого является , другим входом устройства, а выход подключен к входу второго триггера. четвертый элемент ИЛИ,-другой вход коtoporo подключен к второму дешифрат ру, а выход соединен с другим входо первого триггера. На фиг. 1 представлена блок-схема устройства; на фиг, 2 - вариант конструктивного выполнения блока ко троля , Устройство содержит блок 1 фотоэлектрического преобразования сигналов, формирователь 2 импульсов, первый коммутатор 3, регистр k, вто рой коммутатор 5, блок 6 контроля, первый дешифратор 7, счетчик 8, вто рой дешифратор 9, первый триггер 10 шифратор 11, элемент 12 задержки, . первый элемент ИЛИ 13 элемент И Н второй элемент ИЛИ 15, второй триггер 16, третий элемент ИЛИ 17, чет-г вертый элемент ИЛИ 18, третий дешифратор 19, первый вход 20 устройства, первый выход 21 устройства, второй выход 22 устройства, третий выход 23 устройства, второй вход 2 устройства. Блок 6 представляет собой комбинационную пирамидальную схему и содержит элемент задержки 25, элемент И 26, ИЛИ-НЕ 27, ИЛИ 28, И 29, И 30, С помощью элементов И 26, ИЛИ-НЕ 27 производится попарное и каскадное суммирование входных сигналов по модулю 2, а с помощью элементов ИЛИ 28 и блока 25 задержки формирование стробирующего сигнала, учитывакяцего переходные процессы в схеме и считывающего с элементов И 29 и 30 результат контроля. Блок 6 обеспечивает контроль входного ко да по модулю 2 и обнаруживает в нем ошибку по четности. Устройство работает следующим об ра зом„ Пуск ленты производится по команде оператора, поступающей по входу 20 на элемент ИЛИ 17. С выхода элемента ИЛИ 17 эта команда устанавливает в единичное состояние триггер 16 и через элемент ИЛИ 18 - три|- гер 10о Триггер 10 выдает сигнал разрешения на коммутатор 5, С единичного выхода триггера 16 по выходу 23 выдается сигнал на пуск ленты в схему привода перфоленты. Лента приходит в движение, при этом блок 1 считывает информацию с ленты символ за символом. Каждый считанный символ через формирователь 2 импульсов и коммутатор 3 заносится в регистр j, С выходов регистра k код символа подается на вход коммутатора 5 и в блок 6 контроля В блоке 6 контроля считанный код символа проверяется по четности, и при правильной четности, с выхода блока 6 на управляющий вход коммутатора 5 выдается сигнал разрешения о При этом код символа через коммутатор 5 поступает на выход 21 устройства, В ответ на каждый принятый символ внешнее устройство выдает сигнал о приеме, который поступает по входу 2k через элемент ИЛИ 13 на обнуляющий вход регистра 4. Регистр 1 обнуляется и подготавливается к приему следующего символа. После считывания первого символа, относящегося к разделительному участку ленты между текстами и содержащего только синхроотверстие, код этого символа декодируется дешифратором 7, Сигнал с выхода дешифратора 7 обнуляет через элемент ИЛИ 13 регистр k, устанавливает в нулевое состояние триггер 10 и поступает в счетчик 8, При этом символы разделительного участка ленты, не являющиеся информативными, на выход 21 не поступают, Счетчик 8 подсчитывает число символов, считанных с разделительного участка ленты. После накопления счетчиком 8 заданного числа его состояние декодируется дешифратором 9 сигнал с выхода которого устанавливает в нулевое состояние триггер 16 и через элемент ИЛИ 18 устанавливает в единичное состояние триггер 10 и через элемент ИЛИ 15 и элемент 12 задержки возбуждает вход шифратора 11 и вычитает единицу из счетчика 8, При этом триггер 16 снимает с выхода 23 сигнал пуска ленты, выдает по ВЫХОДУ 22 сигнал останова ленты и выдает сигнал разрешения на первый вход элемента И I. Триггер 10 внов выдает сигнал разрешения на коммутатор 5 для выдачи символов во внеш нее устройство по выходу 21, При во буждении входа шифратора 11 на его выходе формируется код символа Про бел, который через коммутатор 3 за носится в регистр k и далее описанным выше образом через коммутатор 5 на выход 21 устройства. Каждый ответный сигнал из внешнего устройств по входу 2 обнуляет регистр и че рез элементы И 1, ИЛИ 15 и задержк 12 вновь возбуждает вход шифратора 11, который формирует код следующего символа Пробел, а также уменьшает содержимое счетчика 8 еще на единицу. Таким образом, на выходе 21 формируется последовательность символов Пробел, соответствующих разделительному участку ленты между текстами, а содержимое счетчика 8 последовательно уменьшается. После то го как состояние счетчика 8 соответ ствует числу О, его состояние декодируется дешифратором 19 Сигнал с выхода дешифратора 19 через элемент ИЛИ 17 устанавливает в единичное состояние триггер 16. При этом лента автоматически приводится в движение и происходит считывание с нее следующего текста. Предложенное устройство позволяе формировать последовательность символов Пробел, соответствующих раз делительному участку ленты между считываемыми текстами, обеспечивает автоматическое непрерывное чтение нескольких текстов, нанесенных на перфоленту, что повышает быстродействие устройства. Формула изобретения Устройство для считывания информ ции, содержащее формирователь им86пульсов, подключенный к выходу блока фотоэлектрического преобразования сигналов и к входам первого коммутатора, регистр,входы которого соединены с первым коммутатором и с выходом первого элемента ИЛИ, а выход подключен к блоку контроля и к одному входу второго коммутатора, другие входы которого соединены с блоком контроля и с первым триггером, а выход является одним выходом устройства, счетчик и элемент И, отличающееся тем, что, с целью повышения быстродействия, оно содержит первый дешифратор, соединенный с формирователем импульсов, со счетчиком и с одними входами первых триггера и элемента ИЛИ, шифратор, подключенный к входу первого коммутатора, элемент задержки, выходы которого соединены со счетчиком и с шифратором, второй дешифратор , подключенный к выходу счетчика, второй триггер, вход которого соединен с вторым дешифратором, а выход подключен к одному входу элемента И, другой вход которого является одним входом устройства, второй элемент ИЛИ, входы которого соединены с вторым дешифратором и с элементом И, а выход подключен к элементу задержки, и последовательно соединенные третий дешифратор, вход которого подключен к выходу счетчика, третий элемент ИЛИ, другой вход которого является другим входом устройства, а выход подключен к входу второго триггера, и четвертый элемент ИЛИ, другой вход которого подключен к второму дешифратору, а выход соединен с другим входом первого триггера. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № А7159, кл. G 06 К 7/10, 197, 2, Патент Японии № 53-30615, кло 97(7)В 23, опублик. 1978 (прототип) .

Авторы

Даты

1982-08-15—Публикация

1981-01-14—Подача