(Б ) УСТРОЙСТВО ДЛЯ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для приема информации | 1983 |

|

SU1088051A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Устройство для управления доменной памятью | 1985 |

|

SU1304076A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

1

Изобретение относится к вычислительной технике, в частности, к уст ройствам программирования запоминающего устройства.

Известно устройство, реализующее способ использования накопителя с дефектными запоминающими элементами, каждый из которых постоянно находится в состоянии - логический ноль или логическая единица. Устройство записывает И-разрядное информационное слово в накопитель, затем осуществляется его контрольное считывание. При отсутствии ошибок цикл записи заканчивается. При обнаружении единичной ошибки производится запись инвертированного слова, при этом факт инверсии иденти- фицируется записью единицы в дополнительный (п+1)-ый индикаторный разряд. В режиме считывания, при наличии единицы в индикаторном разряде, считанное слово инвертируется JОднако это устройство не может быть использовано при записи в программируемый накопитель с одноразовой возможностью записи информации.

Наиболее близким по технической сущности к изобретению является устройство для контроля блоков памяти, содержащее формирователь кодов адреса и формирователь эталонных сигJO налов f 2 }

Однако это устройство не позволяет обходить ячейки памяти в накопителе. При использовании звестного устройства и обнаружении дефектной ячейки вся микросхема, в накопитель которой осуществляется запись, считается непригодной для использования. Также, поскольку дефектная ячейка может появиться в конце цикла записи, общее время записи информации достаточно велико.

Цель изобретения - повышение надежности и быстродействия устройства.

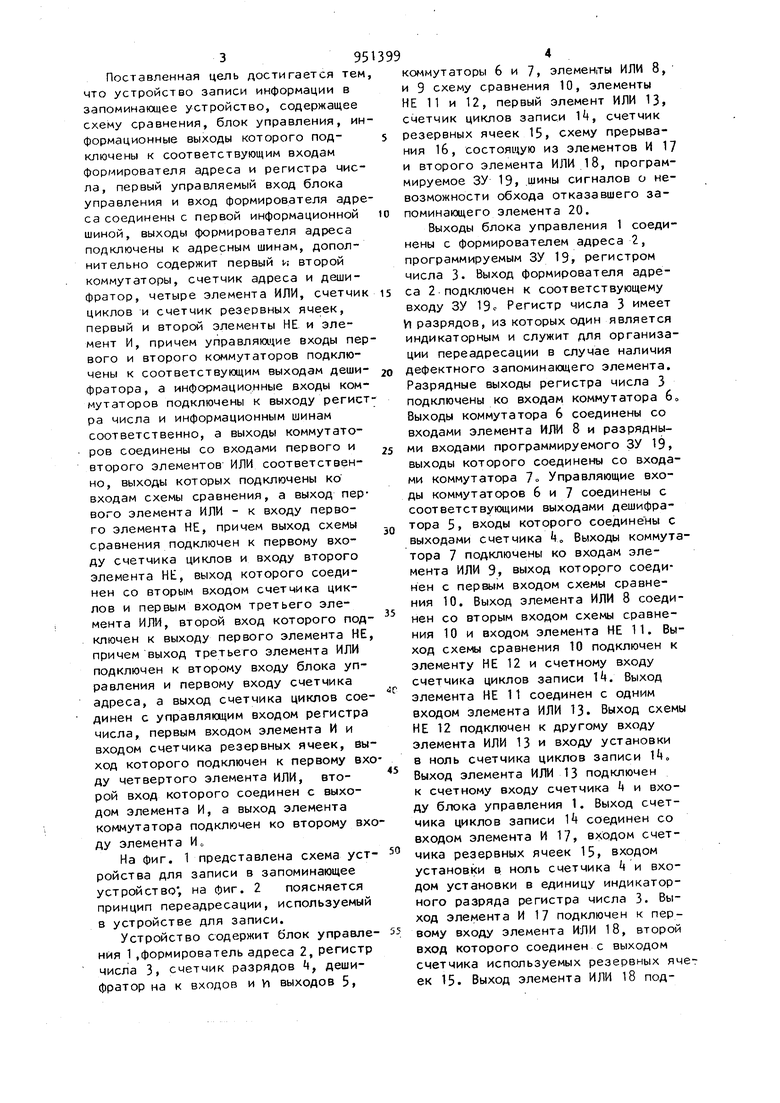

Поставленная цель достигается тем что устройство записи информации в запоминающее устройство, содержащее схему сравнения, блок управления, информационные выходы которого подключены к соответствующим входам формирователя адреса и регистра числа, первый управляемый вход блока управления и вход формирователя адреса соединены с первой информационной шиной, выходы формирователя адреса подключены к адресным шинам, дополнительно содержит первый и второй коммутаторы, счетчик адреса и дешифратор, четыре элемента ИЛИ, счетчик циклов и счетчик резервных ячеек, первый и второй элементы НЕ и элемент И, причем управляюсцие входы первого и второго коммутаторов подключены к соответствующим выходам дешифратора, а информационные входы коммутаторов подключены к выходу регистра числа и информационным шинам соответственно, а выходы коммутаторов соединены со входами первого и второго элементов ИЛИ соответственно, выходы которых подключены ко входам схемы сравнения, а выход пер вого элемента ИЛИ - к входу первого элемента НЕ, причем выход схемы сравнения подключен к первому входу счетчика циклов и входу второго элемента Ht, выход которого соединен со вторым входом счетчика циклов и первым входом третьего элемента ИЛИ, второй вход которого под ключен к выходу первого элемента НЕ причем выход третьего элемента ИЛИ подключен к второму входу блока управления и первому входу счетчика адреса, а выход счетчика циклов сое динен с управляющим входом регистра числа, первым входом элемента И и входом счетчика резервных ячеек, вы ход которого подключен к первому вх ду четвертого элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход элемента коммутатора подключен ко второму вх ду элемента Ио На фиг. 1 представлена схема уст ройства для записи в запоминающее устройство , на фиг. 2 поясняется принцип переадресации, используемый в устройстве для записи. Устройство содержит блок управле ния 1 .формирователь адреса 2, регистр числа 3, счетчик разрядов 4, дешифратор на к входов и у выходов 5

коммутаторы 6 и 7, элементы ИЛИ 8, и 9 схему сравнения 10, элементы НЕ 11 и 12, первый элемент ИЛИ 13, счетчик циклов записи 1, счетчик резервных ячеек 15, схему прерывания 16, состоящую из элементов И 17 и второго элемента ИЛИ 18, программируемое ЗУ 19, .шины сигналов о невозможности обхода отказавшего запоминающего элемента 20.

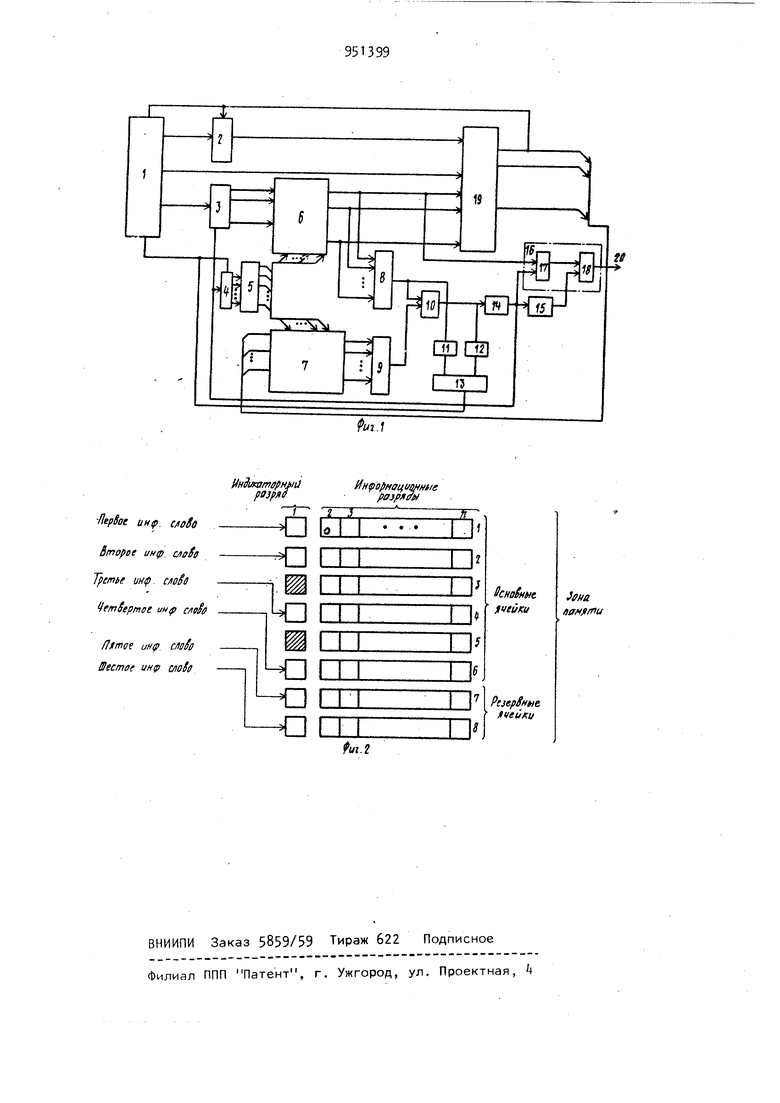

Выходы блока управления 1 соединены с формирователем адреса 2, программируемым ЗУ 19, регистром числа 3. Выход формирователя адреса 2 подключен к соответствующему входу ЗУ 19с Регистр числа 3 имеет И разрядов, из которых один является индикаторным и служит для организации переадресации в случае наличия дефектного запоминающего элемента. Разрядные выходы регистра числа 3 подключены ко входам коммутатора 6 Выходы коммутатора 6 соединены со входами элемента ИЛИ 8 и разрядными входами программируемого ЗУ 19, выходы которого соединены со входами коммутатора 7 Управляющие входы коммутаторов 6 и 7 соединены с соответствующими выходами дешифратора 5, входы которого соединены с выходами счетчика 4, Выходы коммутатора 7 подключены ко входам элемента ИЛИ 9, выход которого соединен с первым входом схемы сравнения 10. Выход элемента ИЛИ 8 соединен со вторым входом схемы сравнения 10 и входом элемента НЕ 11. Выход схемы сравнения 10 подключен к элементу НЕ 12 и счетному входу счетчика циклов записи k. Выход элемента НЕ 11 соединен с одним входом элемента ИЛИ 13. Выход схемы НЕ 12 подключен к другому входу элемента ИЛИ 13 и входу установки 8 ноль счетчика циклов записи И Выход элемента ИЛИ 13 подключен к счетному входу счетчика 4 и входу блока управления 1. Выход счетчика циклов записи Т соединен со входом элемента И 17, входом счетчика резервных ячеек 15, входом установки в ноль счетчика 4 и входом установки в единицу индикаторного разряда регистра числа 3. Выход элемента И 17 подключен к первому входу элемента ИЛИ 18, второй вход которого соединен с выходом сметчика используемых резервных ячеек 15. Выход элемента ИЛИ 18 подключей к шине 20. Выход индикаторного разряда соединен с соответствующими входами формирователя адреса 2 и блока управления 1. Работает устройство следующим об разом. Формирователь адреса 2 формирует код адреса первой ячейки зоны памяти, в которую производится запись. В регистр числа 3 записывается (п-1 разрядное слово, при этом в индикаторный разряд записывается ноль. Перед началом записи счетчики 4, Ни 15 сбрасываются в ноль. Далее, значение первого разряда регистра числа 3 поступает через коммутатор 6 на вход программируемого ЗУ 19 и элемент ИЛИ 8. На выходе элемента НЕ 11 формируется единица, которая через элемент ИЛИ 13 поступает на счетный вход счетчика k и соответствующий вход блока управления 1. В блоке управления осуществляется подсчет единиц. Затем на вход ЗУ 19 и вход элемента ИЛИ 8 поступает значение второго разряда регистра числа 3. Если значение это го разряда равно нулю, то описанный процесс повторяется. Иначе производится запись этого разряда в ЗУ 19. Затем контрольное считывание, Если запись произошла, то на выходе схемы сравнения формируется ноль При записи слова блок управления выдает команду формирователю адреса 2 перейти к следующему адресу. Цикл записи, считывание и сравнение могут быть повторены разрешенное число раз - содержимое счетчика циклов записи И, Если при прохождении разрешенного числа циклов записи, з пись данного разряда не происходит, то с выхода счетчика циклов записи поступает сигнал на вход индикаторного разряда регистра числа 3 и устанавливает этот разряд в единицу. Этот же сигнал сбрасывает Ц в ноль. Процесс переадресации ячеек может повторяться столько раз, скол ко ячеек выделено для одной зоны па мяти. Подсчет использованных резервных ячеек памяти ведется счетчиком 15. При его переполнении выдается сигнал на вход элемента ИЛИ 18, На шине 20 появляется сигнал, свидетел ствующий о невозможности обхода отказавших запоминающих элементов. Изобретение позволяет использова 90 микросхем KPSSGRJii вместо tO при использовании прототипа. Также 9 это устройство позволяет сократить время записи в среднем в два раза. Формула изобретения . Устройство для записи информации в запоминающее устройство, содержащее схему сравнения, блок управления, информационные выходы которого подключены к соответствующим входам формирователя адреса и регистра числа, первый управляемый вход блока управления и вход формирователя адреса соединены с первой информационной шиной , причем выходы формирователя адреса подключены к адресным шинам, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены первый и второй коммутаторы, счетчик адреса и дешифратор, четыре элемента ИЛИ, счетчик циклов и счетчик резервных ячеек, первый и второй элементы НЕ и элемент И, причем управляющие входы первого и второго коммутаторов подключены к соответствующим выходам дешифратора, а информационные входы коммутаторов подключены к выходу регистра числа и информационным шинам соответственно, а выходы коммутаторов соединены с входами первого и второго элементов ИЛИ соответственно, выходы которых подключены к входам схемы сравнения, а выход первого элемента ИЛИ - к входу первого элемента НЕ, причем выход схемы сравнения подключен к первому входу счетчика циклов и входу второго элемента НЕ, выход которого соединен с вторым входом счетчика циклов и первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу первого элемента НЕ, причем выход третьего элемента ИЛИ подключен к второму входу блока управления и первому входу счетчика адреса, а выход счетчика циклов соединен с управляющим входом регистра числа, первым входом элемента И и входом счетчика резервных ячеек, выход которого подключен к первому входу яетвертого элемента ИЛИ, второй вход которого соединен с выходом элемента И, а выход первого коммутатора подключен к второму входу элемента И. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3768071, кл. ,, опублик, 1972. 2. Авторское свидетельство СССР № б252+9, кл, G 11 С 29/00, 1978 (прототип).

IHbll

pajp

-HepSae цн(р. cjioSo Rmoixte ин(р, c/iofo Tjiein f инф. c/ioSa emSepmoe W( c/oSff

Пито uHtf. M/ff Шестск uHip aofff.

ffHpofffai vMM/e разряаы

Авторы

Даты

1982-08-15—Публикация

1980-12-31—Подача