Изобретение относится к запоминающим устройствам и может быть использовано при создании блоков памяти, позволяющих применять матрицы запоминающих элементов (МЗЭ) и микросхемы памяти, в ячейках которых имеются неисправные запоминающие элементы (ЗЭ).

Известно запоминающее устройство с блокировкой неисправных ячеек, которое содержит накопитель, выполненный на матрицах запоминакхдих элементов fl . .

Недостатком этого устройства является низкая надежность.

Наиболее близким техническим решением к изобретению является запоминающее устройство с блокировкой неисправных ячеек, содержащее основные одноразрядные блоки памяти, логические схелы, блок и борки адресов, шины, управляющие переключением, причем в случае выхода из строя в одном из основных одноразрядных блоков памяти одной или группы одноразрядных ячеек памяти в момент обращения подаются с некоторого внешнего управляющего устройства соответствующие сигналы, по которым входвыход основного одноразрядного блока отключается от соответствующих входа и выхода устройства и к ним подключаются вход-выход резервного одноразрядного блока памяти С2.

Недостатком известного устройства является низкая надежность, поскольку общее допустимое число неисправных одноразрядных ячеек памяти (ЯП) в резервном и всех основных однораз10рядных блоках памяти мало и равно информационной емкости резервного одноразрядного блока памяти, при этом отсутствуют средства управления подключением исправных ЯП ре15зервного блока памяти вместо неисправных ЯП.

Целью изобретения является повышение надежности устройства.

Поставленная цель достигается тем,

20 что в запоминающее устройство с блокирЬвкой неисправных ячеек, содержащее первый резервный и основные одноразрядные накопители, входы записи, входы считывания и одноименные

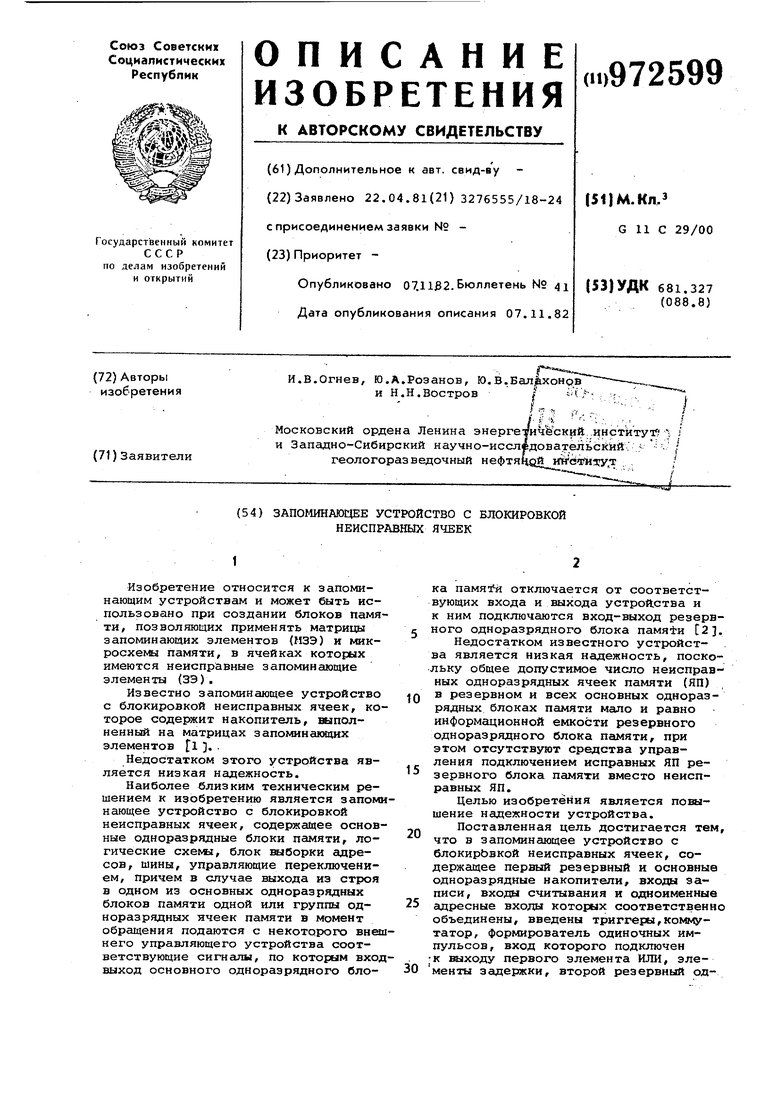

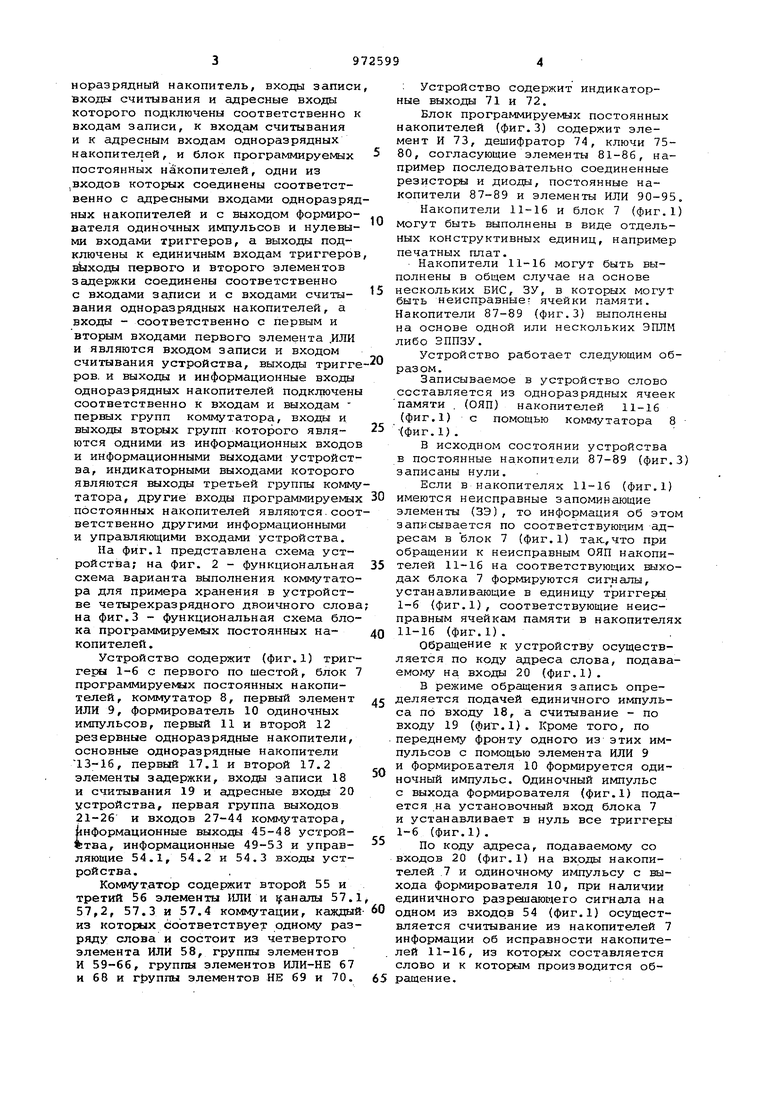

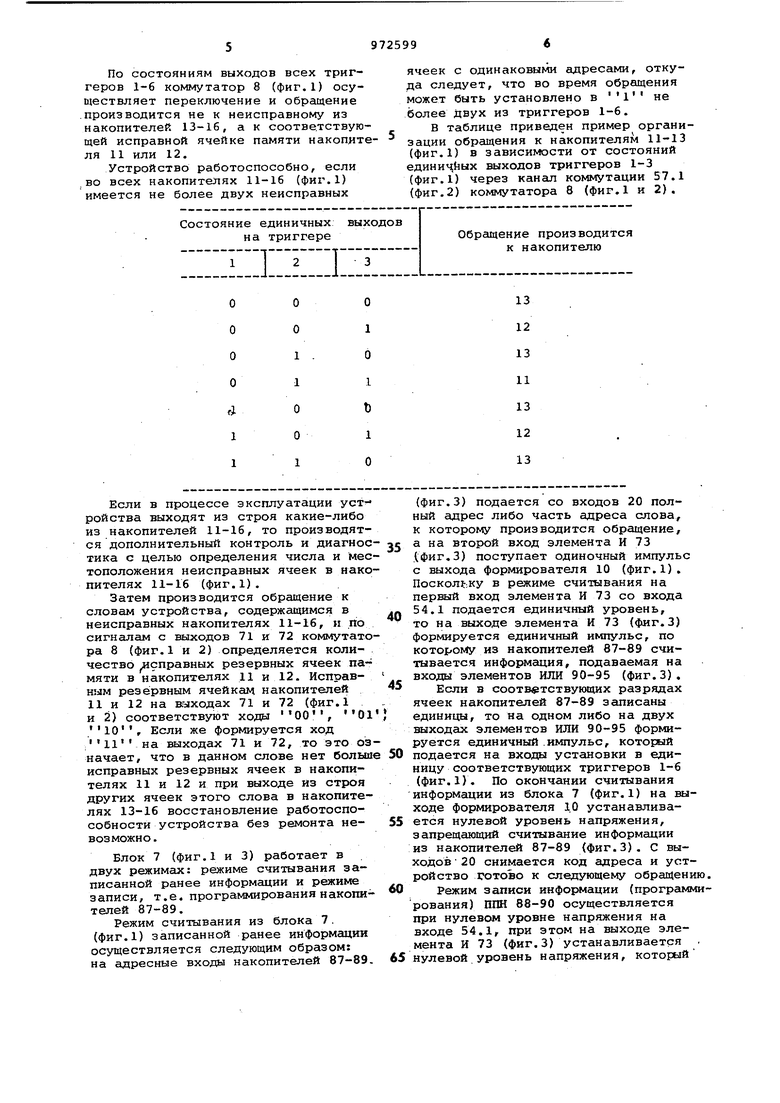

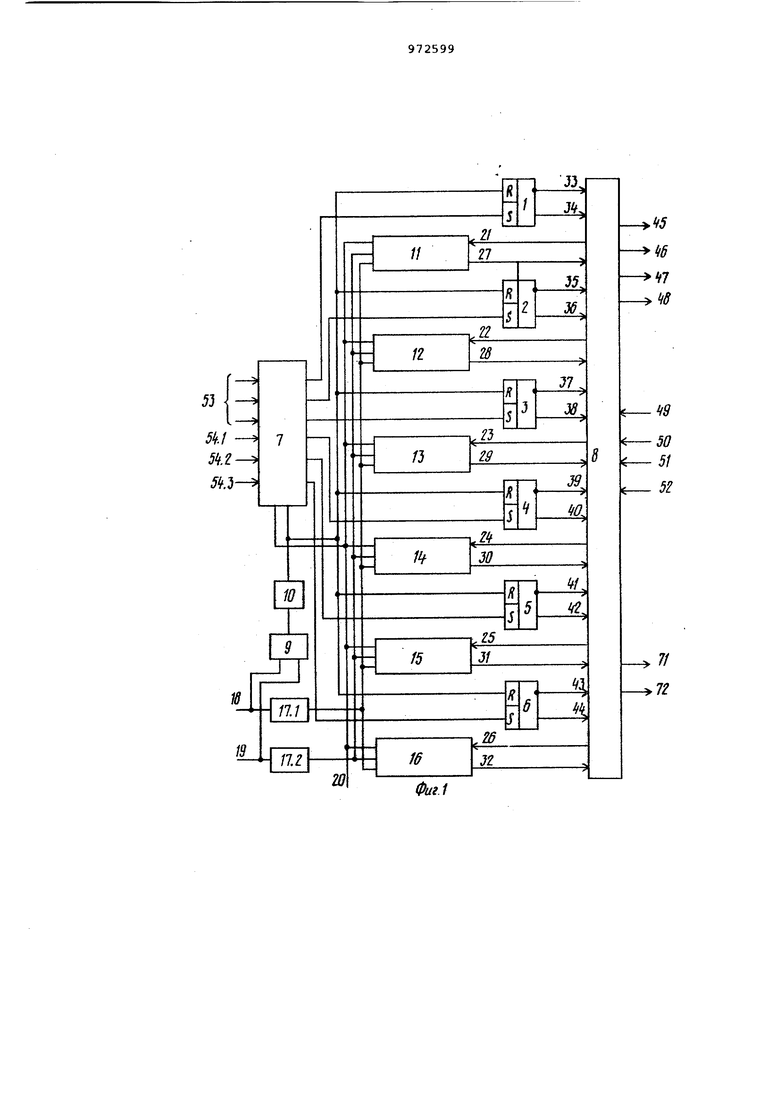

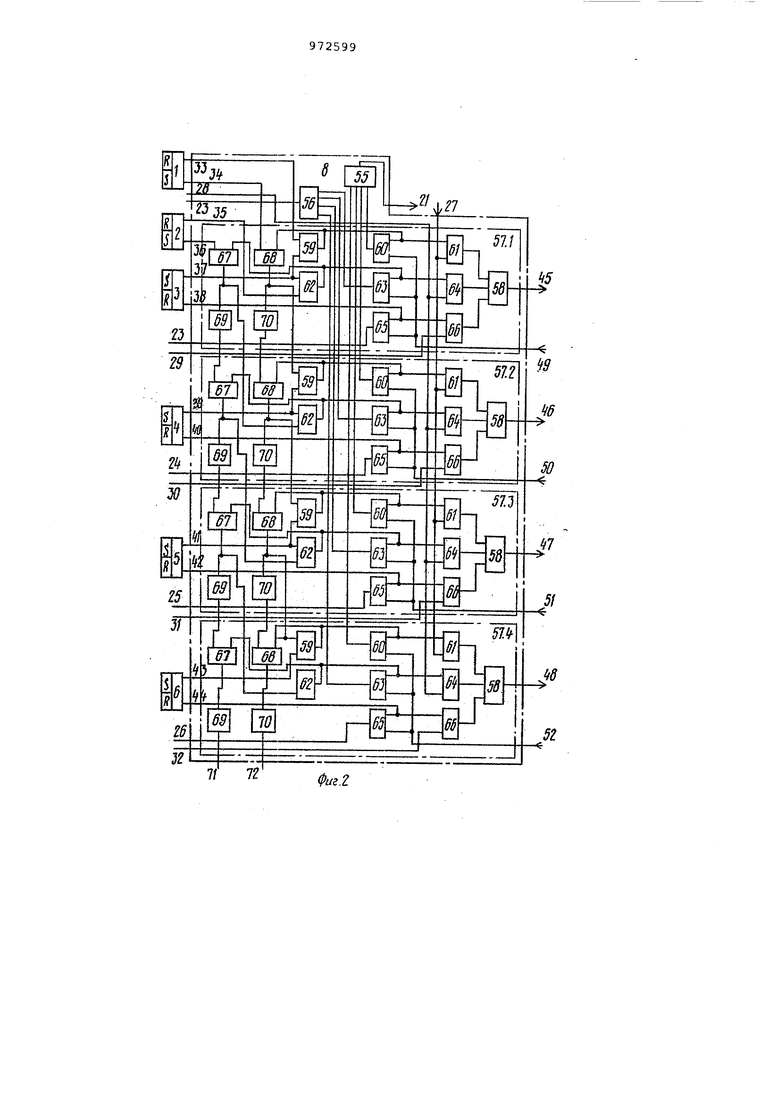

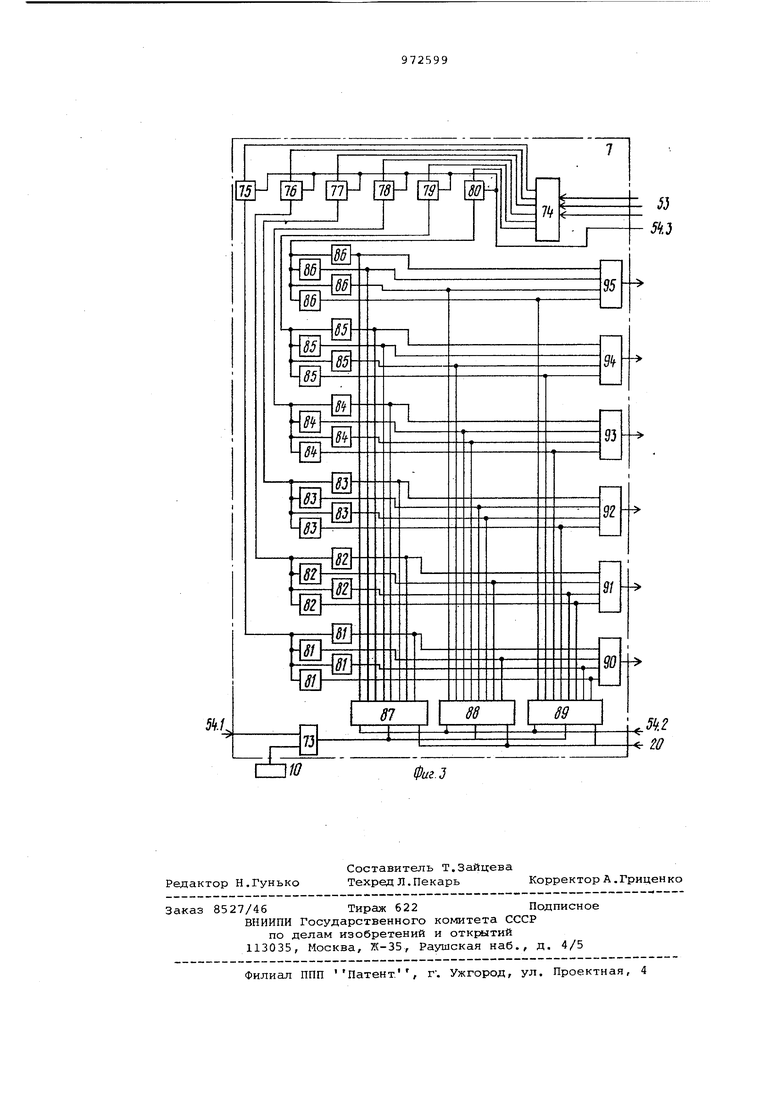

25 адресные входы которых соответственно объединены, введены триггеры,коммутатор, формирователь одиночных импульсов, вход которого подключен к шлходу первого элемента ИЛИ, элементы задержки, второй резервный од30поразрядный накопитель, входы записи входы считывания и адресные входы которого подключены соответственно к входам записи, к входам считывания и к адресным входам одноразрядных накопителей, и блок программируемых постоянных накопителей, одни из ,входов которых соединены соответственно с адресными входами одноразряд ных накопителей и с выходом формирователя одиночных импульсов и нулевыми входами триггеров, а выходы подключены к единичным входам триггеров выходы первого и второго элементов задержки соединены соответственно с входами записи и с входами считы вания одноразрядных накопителей, а входы - соответственно с первым и вторым входами первого элемента .ИЛИ и являются входом записи и входом считывания устройства, выходы тригге ров, и выходы и информационные входы одноразрядных накопителей подключены соответственно к входам и выходам первых групп коммутатора, входы и выходы вторых групп которого являютея одними из информационных входов и информационными выходами устройства, индикаторными выходами которого являются выходы третьей группы комму татора, другие входы программируемых постоянных накопителей являются.соот ветственно другими информационными и управляющими входами устройства. На фиг,1 представлена схема устройства; на фиг. 2 - функциональная схема варианта выполнения коммутатора для примера хранения в устройстве четырехразрядного двоичного слов на фиг.З - функциональная схема блока программируемых постоянных накопителей. Устройство содержит (фиг,1) триг геры 1-6 с первого по шестой, блок программируемых постоянных накопителей, коммутатор 8, первый элемент ИЛИ 9, формирователь 10 одиночных импульсов, первый 11 и второй 12 резервные одноразрядные накопители, основные одноразрядные накопители 13-16, первый 17.1 и второй 17.2 элементы задержки, входы записи 18 и считывания 19 и адресные входы 20 устройства, первая группа выходов 21-26 и входов 27-44 коммутатора, |1Нформационные выходы 45-48 устройства, информационные 49-53 и управляшщие 54.1, 54.2 и 54.3 входы устройства. Коммутатор содержит второй 55 и третий 56 элементы ИЛИ и 1 :аналы 57. 57,2, 57.3 и 57.4 коммутации, кажды из котоЕЯЛХ соответствует одному раз ряду слова и состоит из четвертого элемента ИЛИ 58, группы элементов И 59-66, группы элементов ИЛИ-НЕ 67 и 68 и rljynmi элементов НЕ 69 и 70. : Устройство содержит индикаторные выходы 71 и 72. Блок программируемых постоянных накопителей (фиг.З) содержит элемент И 73, дешифратор 74, ключи 7580, согласующие элементы 81-86, например последовательно соединенные резисторы и диоды, постоянные накопители 87-89 и элементы ИЛИ 90-95. Накопители 11-16 и блок 7 (фиг.1) могут быть выполнены в виде отдельных конструктивных единиц, например печатных плат. Накопители 11-16 могут быть выполнены в общем случае на основе нескольких БИС, ЗУ, в которых могут быть неисправныег ячейки памяти. Накопители 87-89 (фиг.З) выполнены на основе одной или нескольких ЭПЛМ либо ЭППЗУ. Устройство работает следующим образом. Записываемое в устройство слово составляется из одноразрядных ячеек памяти . (ОЯП) накопителей 11-16 (фиг.1) с помощью коммутатора 8 (фиг.1). В исходном состоянии устройства в постоянные накопители 87-89 (фиг.З) записаны нули. Если в накопителях 11-16 (фиг,1) имеются неисправные запоминающие элементы (ЗЭ) , то информация об этом записывается по соответствующим адресам в блок 7 (фиг.1) так,что при обращении к неисправным ОЯП накопителей 11-16 на соответствующих выходах блока 7 формируются сигналы, устанавливающие в единицу триггеры 1-6 (фиг.1), соответствующие неисправным ячейкам памяти в накопителях 11-16 (фиг.1). Обращение к устройству осуществляется по коду адреса слова, подаваемому на входы 20 (фиг.1). В режиме обращения запись определяется подачей единичного импульса по входу 18, а считывание - по входу 19 (фиг.1). Кроме того, по переднему фронту одного из этих импульсов с помощью элемента ИЛИ 9 и формирователя 10 формируется одиночный импульс. Одиночный импульс с выхода формирователя (фиг.1) подается на установочный вход блока 7 и устанавливает в нуль все триггеры 1-6 (фиг.1). По коду адреса, подаваемому со входов 20 (фиг.1) на входы накопителей 7 и одиночному импульсу с выхода формирователя 10, при наличии единичного разрешающего сигнала на одном из входов 54 (фиг.1) осуществляется считывание из накопителей 7 информации об исправности накопителей 11-16, из которых составляется слово и к которым производится обращение.

По состояниям выходов всех триггеров 1-6 коммутатор 8 (фиг.1) осуществляет переключение и обращение

.производится не к неисправному из накопителей 13-16, а к соответствующей исправной ячейке памяти накопятеля 11 или 12.

Устройство работоспособно, если

,во всех накопителях 11-16 (фиг.1) имеется не более двух неисправных

ячеек с одинаковыми адресами, откуда следует, что во время обращения может быть установлено в не более двух из триггеров 1-6.

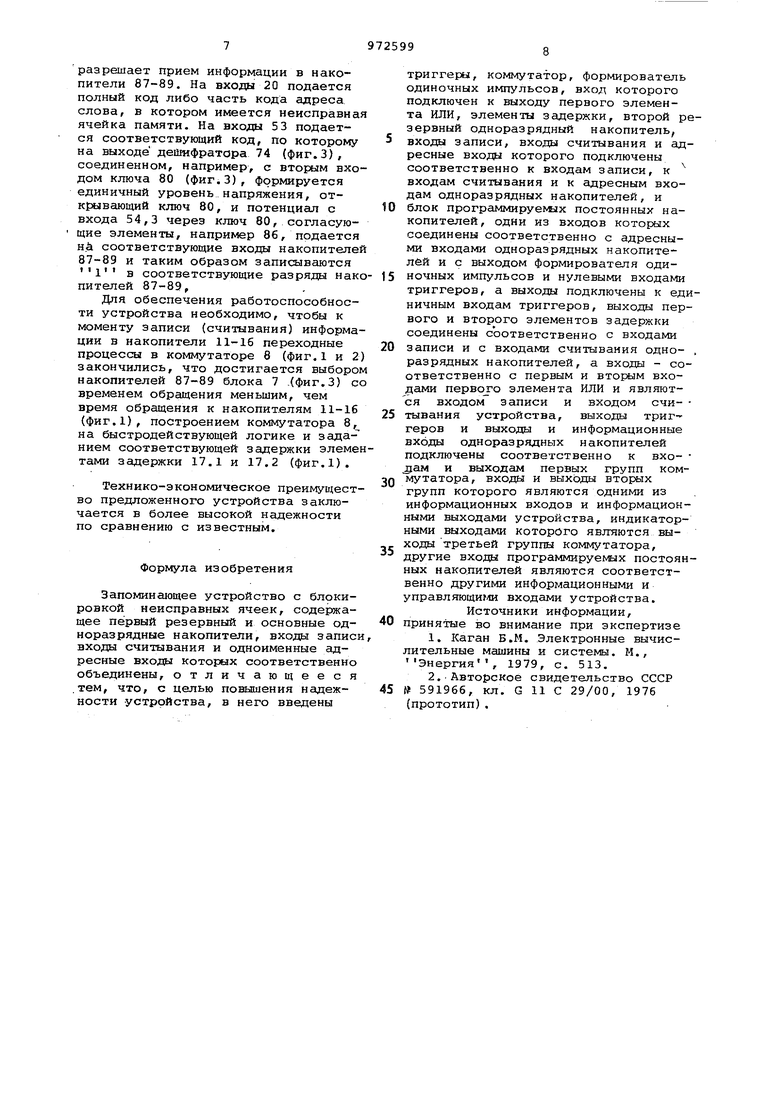

в таблице приведен пример организации обращения к накопителям 11-13 (фиг.1) в зависимости от состояний единицйых выходов триггеров 1-3 (фиг.1) через канал коммутации 57.1 (фиг.2) коммутатора 8 (фиг.1 и 2).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Запоминающее устройство | 1980 |

|

SU928408A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

О О

1 1

о о 1 Если в процессе эксплуатации уст ройства выходят из строя какие-либо из накопителей 11-16, то производятся дополнительный контроль и диагнос тика с целью определения числа и мес тоположения неисправных ячеек в нако пителях 11-16 (фиг.1). Затем производится обращение к словам устройства, содержащимся в неисправных накопителях 11-16, н по сигналам с выходов 71 к 72 коммутато ра 8 (фиг.1 и 2) определяется количество справных резервных ячеек памяти в накопителях 11 и 12. Исправным резервным ячейкам накопителей 11 и 12 на вг:лходах 71 и 72 (фиг.1 и 2) соответствуют ходы 00, Ol 10, Если же формируется ход :11 на выходах 71 и 72, то это оз начает, что в данном слове нет больш исправных резервных ячеек в накопителях 11 и 12 и при выходе из строя других ячеек этого слова в накопителях 13-16 восстановление работоспособности устройства без ремонта невозможно. Блок 7 (фиг.1 и 3) работает в двух режимах: режиме считывания записанной ранее информации и режиме записи, т.е. программирования накопителей 87-89. Режим считывания из блока 7. (фиг.1) записанной ранее информации осуществляется следующим образом: на адресные входы накопителей 87-89.

13 12 13 11 13 12 13

о 1

1 о (фиг.З) подается со входов 20 полный адрес либо часть адреса слова, к которому производится обращение, а на второй вход элемента И 73 1фиг,3) поступает одиночный импульс с выхода формирователя 10 (фиг.1). Поскольку в режиме считывания на первый вход элемента И 73 со входа 54.1 подается единичный уровень, то на выходе элемента И 73 (фиг.З) формируется единичный импульс, по которому из накопителей 87-89 считывается информация, подаваемая на входы элементов ИЛИ 90-95 (фиг.З), Если в соответствующих разрядах ячеек накопителей 87-89 записаны единицы, то на одном либо на двух выходах элементов ИЛИ 90-95 формируется единичный.импульс, который подается на входы установки в единицу соответствующих триггеров 1-6 (фиг.1). По окончании считывания информации из блока 7 (фиг.1) на выходе формирователя 10 устанавливается нулевой уровень напряжения, запрещающий считывание информации из накопителей 87-89 (фиг.З). С выходов 20 снимается код адреса и устройство 1Х)Тово к следующему обращению. Режим записи информации (прогргилмирования) ППН 88-90 осуществляется при нулевом уровне напряжения на входе 54.1, при этом на выходе элемента И 73 (фиг.З) устанавливается , нулевой уровень напряжения, который

разрешает прием информации в накопители 87-89. На входы 20 подается полный код либо часть кода адреса слова, в котором имеется неисправная ячейка памяти. На входы 53 подается соответствующий код, по которому на выходе дешифратора 74 (фиг.З), соединенном, например, с вторым входом ключа 80 (фиг.З), формируется единичный уровень напряжения, отк аваю1ций ключ 80, и потенциал с входа 54,3 через ключ 80, согласующие элементы, например 86, подается н.й соответствующие входы накопителей 87-89 и таким образом записываются в соответствующие разряды накопителей 87-89,

Для обеспечения работоспособности устройства необходимо, чтобы к моменту записи (считывания) информации в накопители 11-16 переходные процессы в коммутаторе 8 (фиг.1 и 2) закончились, что достигается выбором накопителей 87-89 блока 7 (Фиг.З) со временем обращения меньшим, чем время обращения к накопителям 11-16 (фиг.1), построением коммутатора 8, на быстродействующей логике и зада- нием соответствующей задержки элементами задержки 17.1 и 17.2 (фиг.1).

Технико-экономическое преимущество предложенного устройства заключается в более высокой надежности по сравнению с известным.

Формула изобретения

Запоминающее устройство с блокировкой неисправных ячеек, содержащее первый резервный и основные одноразрядные накопители, входы запис входы считывания и одноименные адресные входы которых соответственно объединены, отличающееся .тем, что, с целью повышения надежности устррйства, в него введены

триггеры, коммутатор, формирователь одиночных импульсов, вход которого подключен к выходу первого элемента ИЛИ, элементы задержки, второй резервный одноразрядный накопитель,

входы записи, входы считывания и адресные входы которого подключены соответственно к входам записи, к входам считывания и к адресным входам одноразрядных накопителей, и

блок программируемых постоянных накопителей , одни из входов которых соединены соответственно с адресными входами одноразрядных накопителей и с выходом формирователя одиночных импульсов и нулевыми входами триггеров, а выходы подключены к единичным входам триггеров, выходы первого и второго элементов задержки соединены соответственно с входами

записи и с входами считывания одно- . разрядных накопителей, а входы - соответственно с первым и вторым входами nepBojTo элемента ИЛИ и являются входом записи и входом счи-

тывания устройства, выходы триггеров и выходы и информационные входы одноразрядных накопителей подключены соответственно к вхо- ам и выходам первых групп коммутатора, входы и выходы вторых групп которого являются одними из информационных входов и информационными выхода1чи устройства, индикаторными выходами которого являются выходы третьей группы коммутатора, другие входы nporpaMMHpyeivttJX постоянных накопителей являются соответственно другими информационными и управляющими входами устройства. Источники информации,

принятые во внимание при экспертизе 1. Каган Б.М. Электронные вычислительные машины и системы. М., Энергия, 1979, с. 513.

№ 591966, кл. G 11 С 29/00, 1976 (прототип).

зг

фиг.г

ifS

10

Фиг.З

Авторы

Даты

1982-11-07—Публикация

1981-04-22—Подача