(54) УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ МЕЖСИМВОЛЬНЫХ ИСКАЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой адаптивный корректор межсимвольной интерференции | 1982 |

|

SU1083374A1 |

| Устройство для адаптивной коррекции межсимвольной интерференции | 1981 |

|

SU951724A1 |

| Цифровой адаптивный корректорСигНАлА | 1978 |

|

SU832733A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах данных | 1979 |

|

SU921099A2 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Цифровой адаптивный корректор межсимвольных искажений в сигналах передачи данных | 1978 |

|

SU780209A1 |

| Цифровой корректор сигналов | 1979 |

|

SU862366A1 |

| Корректор межсимвольных искажений | 1984 |

|

SU1220130A1 |

| Цифровой адаптивный корректор меж-СиМВОльНыХ иСКАжЕНий B СигНАлАХ дАН-НыХ | 1978 |

|

SU801269A1 |

| Адаптивный корректор сигнала | 1978 |

|

SU794735A1 |

1

Изобретение относится к технике связи и может использоваться для коррекции межснмвольных искажений в модулированных сигналах, принимаемых посредством двух демодуляторов.

Известно устройство для адаптивной коррекции межсимвольных искажений, соi держащее последовательно соединенные аналого-цифровой преобразователь, блок памяти и арифметический блок, выход ь полярностей и знаков отклонения амплитуды модулированного сигнала от номинала которого подключен к другому входу блока памяти, вход синхронизации которого соединен с выходом программного блока, управляющий вход которого соединен с другим Выходом аналого-цифрового феобразователя, входами синхронизации арифметического блока и блока памяти коэффициентов передачи, выход которого подключен к другому входу арифметического блока, другой выход блока памяти через блок корреляции подключен к другому входу блока памяти коэффициентов

передачи, а другой выход арифметического блока 1Шляется выходом устройства, входами которого являются вход аналогоцифрового преобразователя и другой вход программного блока JflJОднако известное устройство имеет низкую точность адаптивной коррекции.

Цель изобретения - повьЕыение точности адаптивной коррекции путем исключения ложных регулировок коэффициентов

10 передачи.

Поставленная цель достигается тем, что в устройство для адаптивной коррекции межсимвольных искаясений, содержа щее последовательно соединенные аналого15цифровой преобразователь, блок памяти и арифметический блок, выход полярнос тей и знаков отклонения амплитуды модулированного сигнала от номинала которого подключен к другому входу блока

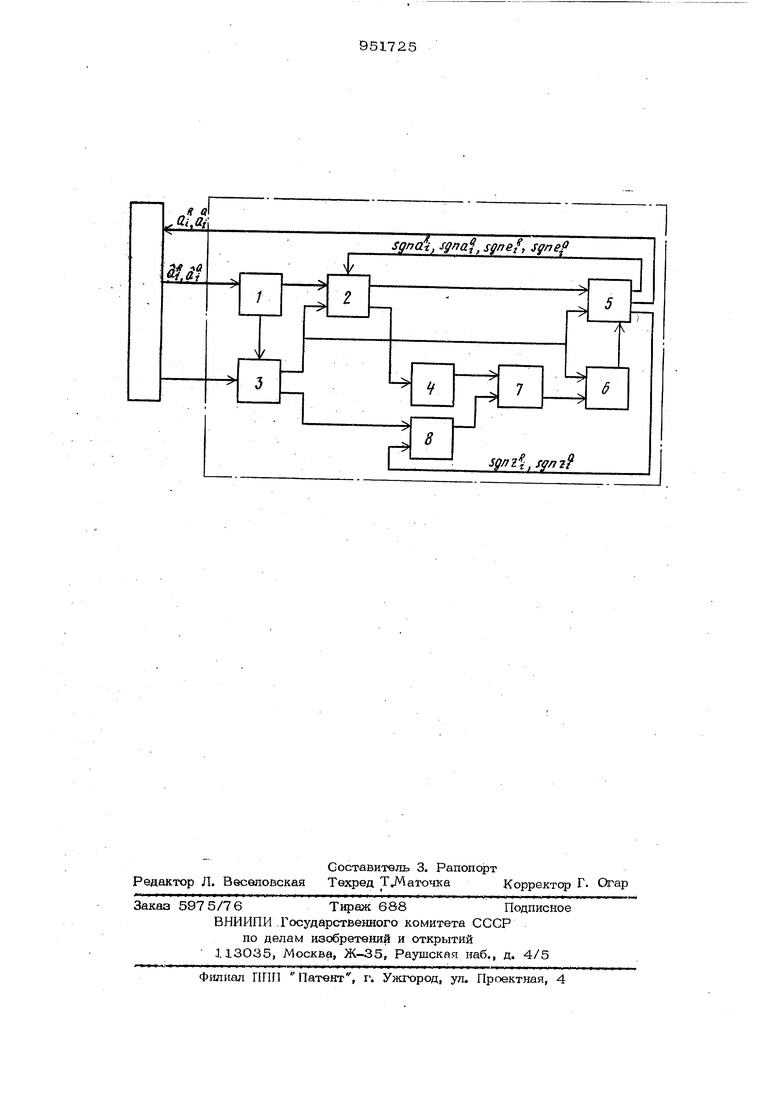

20 памяти, вход синхронизации которого соединен с выходом программного блока, управляющий вход которого соединен с другим выходом аналого-цифрового преобразоватепя, входами синхронизации арифметического блока и блока памяти коэффициентов передачи, выход которого подключен к другчэму входу арифметического блока, другой выход блока памяти подключен к входу блока корреляции, а другой выход арифметического блока является выходом устройства, входами кото рого являются входом аналого-цифрового преобразователя и другой вход программного блока, введены дополнительный бло памяти иСблок управления, при этом выход блока корреляции через блок управле ния подключен к другому входу блока памяти коэффициентов передачи, другой выход программного блока подключен через дополнительный блок памяти, вход которо го соединен с дополнительным выходом арифметического блока, к другому входу блока управления. На чертеже представлена структурная схема предлагаемого устройства. Устройство для адаптивной коррекции межсимвольных искажений содержит аналого-цифровой преобразователь 1, блок 2 памяти, программный блок 3, блок 4 корреляции, арифметический блок 5, блок 6памяти коэффициентов передачи, блок 7управления, дополнительный блок 8 памяти. Устройство работает следующим обра, зом. ДЯ „ Q Аналоговые сигналы с(- и . ходов демодуляторов приемника (не показаны) поступают на аналого-цифровой г реобразователь 1, где производится стробирование этих сигналов в отсчетные моменты времени, запо.минание и хранение амплитуд полученных напряжений выборок и преобразование выборок в И разрядные кодовые числа. Процесс преоб разованИя осуществляется тшс, что сначала преобразуется сигнал а В с выхода первого (синфазного) демодулятора, а затем - сигнал Q5 с выхода второго (квадратурного) демодулятора приемника;: В.той же очередности производится запись в блок 2 памяти двух К -разрядных чисел выборок, полученных в результате преобразования. В блок 2 памяти с выхода арифметического блока 5 также записываются данные о полярности модулированных сигналов а и а на вьисодах устройства (SgHO и ) и сигналы SQUe , отображающие знак отклонения ампл1студы откорректированных модулированных сигналов al и а от номинала. Сигналы управления для изменения коэф94. тов передачи регуляторов отводов тора вьфабатываются в соответствии дующим алгоритмом: фи компенсации синфазного мешаювлиянияRf J - 6 MaJ®s aJ®s§ e| С.1) i е-.5 ag ©s§ ао © eg (i; При. компенсации квадратурного меего влияния i s§rHa| s c|0©sg.MeS Сз) С4; Oi а и дгу а - знак проекции сигналов, подвер.женных мещающе му влиянию, на -когерентные лебания R и Q. соответственно; . gHCI M -знак проекции сигналов, создающих мещающие влияния, на когерентные колебания R и Q соот ветственно; беие иееие -знак проекции отклонения амплитуд сигналов а от номинала относительно когерентных колебаний R и Q соответственно. По командам программного блока 3 и в соответствии с выбранным алгоритмом работы устройства в блоке 4 корреляции вырабатываются сигналы о нахфавлении изменения коэффициента передачи соответствующего отвода устройства, которые в виде У НР зряднь1х ЧИсел хранятся в блоке 6 памяти коэффициентов передачи. В каждом такте работы программного блока 3 из блоков 2 и 6 в блок умножения (не показан) арифметического блока 5 поступают два И-разрядных кодовых числа, соответствующие модулям и полярно г- стям кодов выборки и коэффициента передачи для регулятора соответствующего отвода устройства. Прячем сначала в арифметический блок 5 поступает код

сигнала dt , а затем - код выборки сигнала с 1(ля умножения на один и тот же код коэффициента передачи регулятора соответствующего отвода устройства. Полученные произведения5

двух пар чисел записываются по командам, поступающим из {программного блока 3 в один из двух сумматоров (не показаны) арифметического блока 5, с целью суммирования произведений раздельно О для выборок сигнала d и а .

В следующем такте работы программного блока 3 из блоков 2 и 6 памяти на входы арифметического блока 5 поступают кодовые числа, соответствующие опе-15 рации .умножения сигналов для следующего отвода устройства. Полученные произведения алгебраически суммируются в соответствующих сумматорах .арифметического блока 5 с числами, полученными в 20 предьщущем такте работы программного блока 3 для предществующего отвода устройства. Этот процесс продолжается до тех пор, пока в сумматорах арифметического блока 5 не будут записаны суммы, 25 полученные в результате суммирования произведений кодов выборки и коэффициенггов передачи для всех отводов устройства.

В предлагаемом устройстве сигналы 30 0| и а9 могут совпадать с одним из когерентных колебаний. При этом, если проекция сигнала, например, а9 на когерентное колебание Q , равна нулю, то сигналSgKi О будет ложен, и, следова- 35 тельно, результат вычисления по выражению (2)5QH 1l - также ложен. Аналогично неверный результат определения сигнала tl - имеет место для этого случая и по выражению (З).40

Таким образам, для исключения формирования ложных сигналов SQIrh и sOMh об изменении коэффициентов передачи ре1 уляторов соответствующих отводов устройства необходимо использовать сигналы запрета регулировки по прямым или перекрестным связям в соответствующих отводах, т.е. исключить возможность ложной регулировки для случаев, когда проекции сигналов а и Ct равны нулю. Эти сигналы управления (SgnZ.. И9Оц2. ) формируются в арифметическом блоке 5 и поступают в дополнительный, блок 8 памяти, служащий для совмещения во времени этих сигналов с сигналами Sgna , Sgnaf, , 607) В требуемые мом-:нт:ы времени сигна хы управления Zf и SQfHZ

с выхода дополнительного блока 8 памяти поступают в блок 7 управления и запрещают подачу с выхода блока 4 корреляции сигналов или Sg nlllJ о направлении изменения коэффициентов передачи регуляторов отводов устройства на вход блока 6 памяти коэффициентов передачи.

В процессе настройки устройства в блоке 6 памяти коэффициентов передачи записываются такие кодовые числа коэффициентов передачи для регуляторов отводов, при которых величина межсим вольных искажений минимальна.

Таким образом, предлагаемое устройство повыщает точность адаптивной коррекции путем исключения ложных регулировок коэфф{щиентов передачи. Формула изобретения

Устройство для адаптивной коррекции

межсимвольнь1х искажений, содержащее последовательно соединенные аналогоцифровой преобразователь, блок памяти и арифметический блок, выход полярностей и знаков отклонения амплитуды модуЛ1фова шого сигнала от номинала которого подключен к другому входу блока па-

мяти, вход синхронизации которого соединен с Выходом программного блока, управляющий вход которого соединен с фугим выходом аналого-цифрового преобразователя. Входами синхронизации арифметического блока и блока памяти

коэффициентов передачи, Выход которого

подключен к другому входу арифметического блока, другой выход блока памяти подключен к входу блока корреляции, а другой Выход арифметического блока является, выходом устройства, входами которого являются вход аналого-цифрового преобразователя и другой вход программного блока, отличающееся тем, что, с целью повь1щения точности адаптивной коррекции путем исключения ложных регулировок коэффициентов передачи, введены дополнительный блок памяти

и блок управления, при этом выход блока ; корреляции через блок управления подключен к другому входу блока памяти коэффициентов передачи, другой выход програм много блока подключен через дополнительный блок памяти, вход которо- . го соединен с дополнительным выходом арифметического блока, к другому вхо- , ду блока управления.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-08-15—Публикация

1981-01-04—Подача