(5) ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU928632A1 |

| Устройство контроля цифро-аналоговых преобразователей | 1981 |

|

SU1008902A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU947956A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

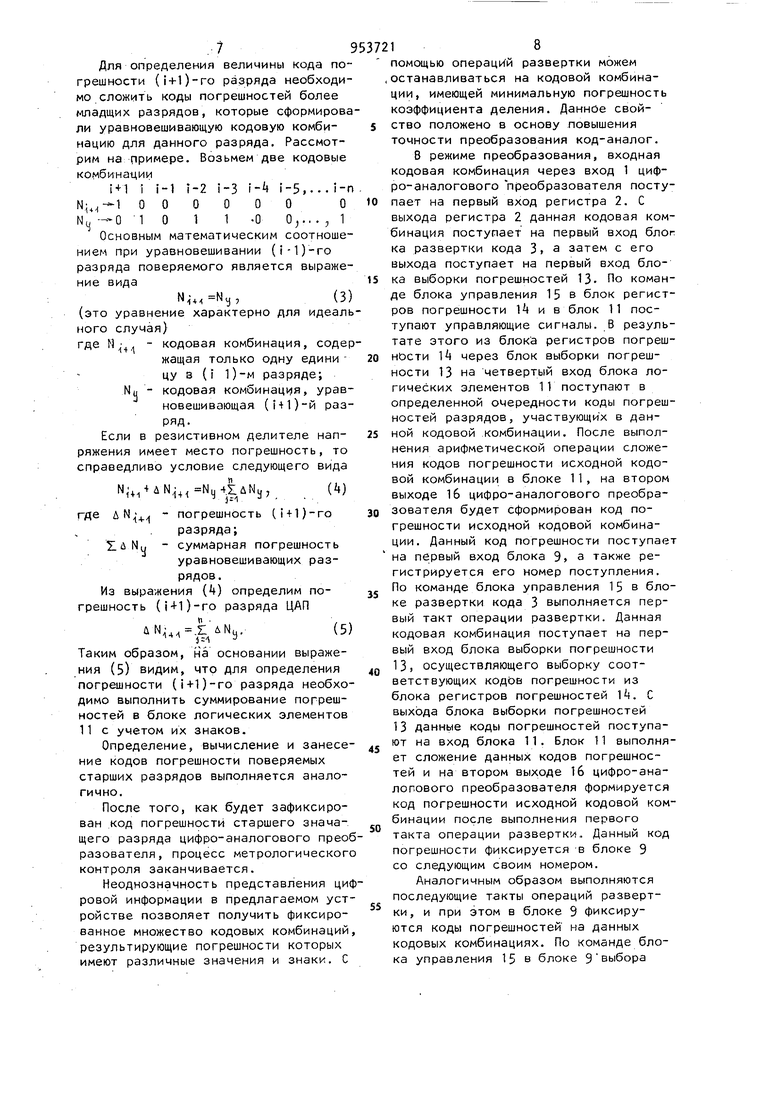

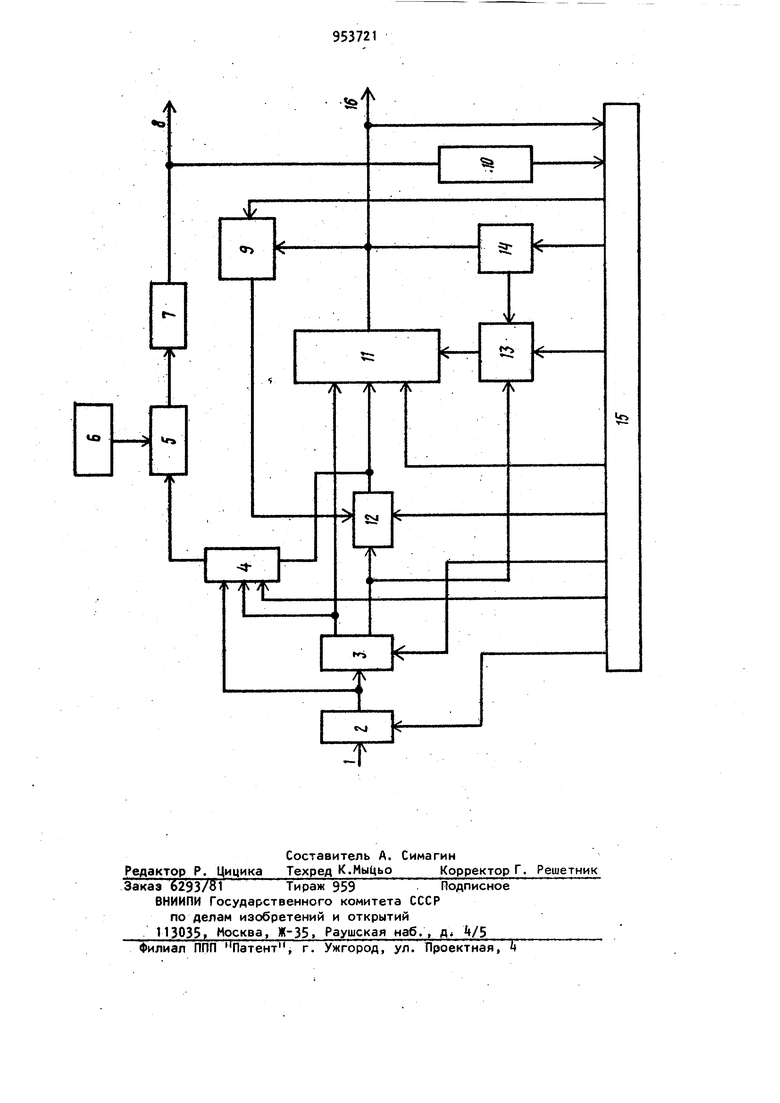

Изобретение относится к цифровой измерительной и вычислительной технике и может быть использовано в информационно-измерительных системах для преобразователя цифровых кодов с иррациональными основаниями в аналоговые величины. По основному авт. св. If известен цифро-аналоговый преобразователь (ЦАП), содержащий регистр, блок эталонных величин, блок ключевых элементов, блок выделения разности, устройство для суммирования эталонов, блок управления, блок развертки кода, блок свертки кода, блок логических элементов и цифровой комг мутатор, причем вход ЦАП соединен с первым входом регистра, выход которого подключен к первому входу блока развертки кода и первому входу цифрового коммутатора, выход которого соединен с первым входом блока ключевых элементов, второй вход которого подключен к выходу блока этаЛОННЫХ величин, а выход с входом устройства для суммирования эталонов, выход которого соединен с первой выходной шиной ЦАП и с входом блока выделения разности, первый выход блока развертки кода подключен к второму входу цифрового коммутатора и первому входу блока логических элементов, второй выход к первому входу блока свертки кода, выход которого соединен с вторым входом блока логических элементов, выход которого подключен к второй выходной шине ЦАП, выход блока выделения разности соединен с входом блока управления, пять выходов которого подключены соответственно к вторым входам регистра, блоков развертки и свертки,кодов, а также к третьим входам цифрового коммутатора и блока логических элементов PJ . Недостатком известного устройства является ограниченная точность преобразования код-аналог вследствие температурной и временной нестабиль ности, возникающей в резистивном де лителе напряжения, который использу ется в блоке эталонных величин. Информация о величине кода погреш ности в известном устройстве не позволяет повысить точность преобразования. Цель изобретения - повышение точности преобразования. Поставленная цель достигается тем что в цифро-аналоговый преобразователь введены блок выбора минимального кода погрешности, блок регистров погрешности и блок выборки поГрешности, первый вход которого соединен с вторым выходом блока разверт ки кода, второй вход - с выходом бло регистров погрешности, выход - с че вертым входом блока логических элем тов, а третий вход с шестым выходом блока управления, второй вход которого соединен с выходом блока логических элементов и первыми входами блока регистров погрешности и блока выбора минимального кода погрешности вторые входы которых подключены соответственно к седьмому и восьмому выходам блока управления, причем выход блока выбора минимального кода погрешности соединен с третьим входом блока свертки кода. На чертеже представлена функциональная схема ЦАП.. Она содержит вход 1 преобразователя, регистр 2, блок развертки кода 3 цифровой коммутатор 4, блок ключевых элементов 5 блок эталонных величин 6, устройство суммирования эталонных величин 7 первый выход 8 цифро-аналогового преобразователя, блок выбора минимального код погрешности 9 блок выделения разности 10, блок логических элементов 11, блок свертки кода 12, блок выбор ки погрешности 13, блок регистров погрешности 14, блок управления 15 второй выход 16 цифро-аналогового преобразователя. Вход 1 цифро-аналогового преобразователя информационным, через который на первый вход регистра 2 поступает цифровой код. Выход регистра 2 соединен одновременно с первыми входами цифрового коммутатора k, блоком развертки кода 3. Выход цифрового коммутатора t соединен с управляющим входом блока ключевых элементов 5, информационные входы блока 5 соединены с выходом блока эталонных величин 6. Вход устройства суммирования эталонных величин 7 соединен с выходом блока ключевых элементов 5- Выход блока 7 является первым выходом 8 цифро-аналогового преобразователя , на котором формируется результирующий аналоговый сигнал процесса преобразователя код-аналог. Выход блока выделения разности 10 соединен с выходом устройства суммирования эталонных величин 7- В режиме метрологического контроля блок выделения разности 1, производят сравнение предыдущего и последующего аналоговых сигналов, формирующихся на первом выходе В цифро-аналогового преобразователя. Выход блока 10 является управляющим и соединен с первым входом блока управления 15- Первый выход блока развертки кода 3 соединен одновременно с вторым входом цифрового коммутатора k и первым входом блока логических элементов 11. Второй выход блока развертки кода 3 соединен с первым входом блока свертки кода 12 и первым входом блока выборки погрешности 13- Блоки свертки 12 и развертки кода 3 выполняют логическую операцию развертки и свертки кодовых комбинаций. Выход блока 12 соединен с вторым входом блока, логических элементов 11 и четвертым входом цифрового коммутатора. Выход блока логических элементов 11 является вторым выходом 16 ЦАП, который одновременно соединен с первыми входами блока выбора минимального кода погрешности 9, блоком регистров погрешности и вторым входом блока управления 15- Третий вход блока свертки кода 12 соединен с выходом блока выбора минимального кода погрешности 9. Блок выбора минимального кода погрешности 9 производит логическую операцию сравнения и из определенного количества кодовых комбинаций производит выбор самой минимальной кодовой комбинации, фиксируя при этом номер ее поступления. Выход блока регистров погрешности I соединен с вторым входом блока выборки погрешности 13. Блок регистров погрешности 14 служит для хранения и передачи кодов погрешностей разрядов ЦАП. Выход блока 13 соединен с четвертым входом блоком логических элементов 11, осуществляющего операции сложения и вычитания кодовых комбинаций. Устройство выборки погрешностей 13 служит для выборки из блока Т в соответствии с номера ми позиций разрядов кодов погрешнос тей данных разрядов. Первый, второ третий, четвертый, пятый, шестой, седьмой и восьмой выходы блока управления 15 соединены соответственно со вторым входом .регистра 2, с третьим входом цифрового коммутатора k, с вторым входом блока развертки кода 3, с вторым входом блок свертки кода 12, с третьим входом блока логических элементов 11, с третьим входом блока выборки погреш ности 13, с вторым входом блока регистров погрешности 1, с вторым входом блока выбора минимального ко да погрешности 9. Блок управления 13 обеспечивает функционирование устройства. ЦАП работает в двух режимах: реж ме метрологического контроля линейности выходной характеристики и режиме непосредственного преобразования входного цифрового кода в ана логовую величину. .В режиме метрологического контро линейности выходной характеристики участвуют все блоки предлагаемого устройства за исключением блока 9 а а режиме непосредственного преобразования не участвует в формировании сигнала на выходе 8 блок выделе ния разности 10. В процессе метрологического конт роля линейности выходной характерис тики производится определение велич отклонений весов разрядов от требуемых величин и их регистрация. К кодам с иррациональными основа ниями относятся р-коды Фибоначчи и коды золотой Р-пропорции. в коде золотой р-пропорции любое действительное число Z может быть представлено в виде i где Эа - двоичная цифра; Ыр - вес 1-го разряда; р - параметр кода (0, 1,2, 3. ...V . Чтобы определить вес 1-го разряда для различных параметров кода необходимо решить уравнение xP -xP-I O,(2) которое является характеристическим уравнением полинома (1). Отношение соседних р-чисел Фибиначчи для больших номеров также приближается кобр-. Характерной особенностью данных кодов является неоднозначность представления цифровой информации, т.е. одному результирующему числу может ставиться в соответствии определенное количество разных кодовых комбинаций. Для р-кодов существует единственная минимальная форма представления цифровой величины, т.е. после каждой значащей единицы в кодовой комбинации следует не менее р-нулей. Переход от минимальной формы к номинальной осуществляется с помощью операции развертки кода, которая заключается в замене единицы в 1-м разряде на единицы в (1-1)-м и (1-р-1)-м разрядах. Операция свертки является обратной операции развертки. Данные операции не изменяют резулструющего значения эквивалента, представляемого кодовой комбинацией, а изменяют лишь форму представления самой кодовой комбинации. В этом и заключается неоднозначность представления цифровой информации в данных кодах. 3 режиме не-; рологического контроля путем уравиове1:;иеания i-ro поверяемого разряда группой более младших разрядов при условии, что () младших разрядов удовлетворяет своим техническим требованиям, наг1Олняется формирование кода погре(5)ности 1-го поверяемого разряда. Данный код погрешности фиксируется на втором выходе 16 ЦАП. Затем по команде блока управления 15 происходит запись кода погрешности i-ro поверяемого разряда в блок регистров погрешности 1, номер которого соответствует позиции данного разряда в ЦАП. Формирование кода погрешности (i+1)-ro разряде: выполняется аналогично путемуравновешивания данного разряда группой более младших разрядов. Полученный код погрешности формируется на втором выходе 16 ЦАП. Если в полученной кодовой комбинации уравновешивающей есть разряды уже имеющие коды погрешности, храняющиеся в блоке регистров погрешности 15, то в блоке 13 выполняется поочередная выборка данных кодов погрешностей, начиная со старших номеров. Данные коды погрешностей через блок 13 поступают на четвертый вход блока логических элементов 11.

Для определения величины кода погрешности (i+l)-ro разряда необходимо сложить коды погрешностей более младщих разрядов, которые сформировали уравновешивающую кодовую комбинацию для данного разряда. Рассмотрим на примере. Возьмем две кодовые комбинации

i + 1 i i-1 1-2 i-3 f- i-5,...i-n N;,- 000000 0 N(j - 0 1 0 1 1 -0 0/.. . ,, 1

Основным математическим соотношением при уравновешивании (i-l)-ro разряда поверяемого является выражение вида

Ni.,Ny,(3)

(это уравнение характерно для идеального случая)

где - кодовая комбинация, содержащая только одну едини цу 3 (i 1)-м разряде; NU кодовая комбинац1 я, уравновешивающая (И1)-й разряд.

Если в резистивном делителе напряжения имеет место погрешность, то справедливо условие следующего вида

Nj,, (k)

где AN - погрешность (i + 1)-ro

разряда;

LuNu - суммарная погрешность уравновешивающих разрядов.

Из выражения (k) определим погрешность (t-(-l)-ro разряда ЦАП

uN,,iiN4. (5)

j;- J

Таким образом, на основании выражения (5) видим, что для определения погрешности (i+1)-го разряда необходимо выполнить суммирование погрешностей в блоке логических элементов 11 с учетом их знаков.

Определение, вычисление и занесение кодов погрешности поверяемых старших разрядов выполняется аналогично.

После того, как будет зафиксирован код погрешности старшего значащего разряда цифро-аналогового преобразователя, процесс метрологического контроля заканчивается.

Неоднозначность представления цифровой информации в предлагаемом устройстве позволяет получить фиксированное множество кодовых комбинаций, результирующие погрешности которых имеют различные значения и знаки. С

помощью операц1/{й развертки можем .останавливаться на кодовой комбинации, имеющей минимальную погрешность коэффициента деления. Данное свойство положено в основу повышения точности преобразования код-аналог. 8 режиме преобразования, входная кодовая комбинация через вход 1 цифро-аналогового преобразователя поступает на первый вход регистра 2. С выхода регистра 2 данная кодовая комбинация поступает на первый вход блог ка развертки кода 3, з затем с его выхода поступает на первый вход блока выборки погрешностей 13. По команде блока управления 15 в блок регистров погрешности 1 и в блок 11 поступают управляющие сигналы. В результате этого из блока регистров погрешнОсти 1 через блок выборки погрешности 13 на четвертый вход блока логических элементов 11 поступают в определенной очередности коды погрешностей разрядов, участвующих в данной кодовой комбинации. После выполнения арифметической операции сложения кодов погрешности исходной кодовой комбинации в блоке 11, на втором выходе 16 цифро-аналогового преобразователя будет сформирован код погрешности исходной кодовой комбинации. Данный код погрешности поступает на первый вход блока 9 а также регистрируется его номер поступления. По команде блока управления 15 в блоке развертки кода 3 выполняется первый такт операции развертки. Данная кодовая комбинация поступает на первый вход блока выборки погрешности

13, осуществляющего выборку соответствующих кодов погрешности из блока регистров погрешностей . С выхода блока выборки погрешностей 13 данные коды погрешностей поступают на вход блока 11. Блок 11 выполняет сложение данных кодов погрешностей и на втором выходе 16 цифро-аналопового преобразователя формируется код погрешности исходной кодовой комбинации после выполнения первого такта операции развертки Данный код погрешности фиксируется -в блоке 9 со следующим своим номером.

Аналогичным образом выполняются последующие такты операций развертки, и при этом в блоке 9 фиксируются коды погрешностей на данных кодовых комбинациях. По команде блока управления 15 в блоке 9выбора

минимального кода погрешности осуществляется определение минимального кода погрешности, при этом также определяется номер такта развертки исходной кодовой комбинации. По управляющему сигналу блока управления 15 в блок 12 свертки кода выполняется операция свертки кода до кодовой комбинации, имеющей минимальную погрешность. Количество тактов свертки развернутой кодовой комбинации исходной определяется управляющим сигналом от блока 9 выбора минимального кода погрешности по фиксированному номеру минимального кода погрешности. С выхода блока 12 сформированная кодовая комбинация с минимальной погрешностью через цифровой коммутатор k поступает на управляющие входы блока ключевых элементов 5, которые осуществляют подключение от блока эталонных величин 6 через информационные входы блока ключевых элементов 3 к входу устройства 7 суммирования эталонных величин аналоговые величины. В результате этого на первом выходе 8 ЦАП будет сформирован результирующий аналоговый сигнал с минимальной погрешностью.

Формула изобретения Цифро-аналоговый преобразователь по авт. св. ff , отличающийся тем, что, с целью

повышения точности преобразования, в него введены блок выбора минимального кода погрешности, блок регистров погрешности и блок выборки погрешности, первый вход которого соединен с вторым выходом блока развертки кода, второй вход - с выходом блока регистров погрешности, выход - с четвертым входом блока логических элементов, а третий вход - с шестым

выходом блока управления, второй

вход которого соединен с выходом блока логических элементов и первыми входами блока регистров погрешности и блока выбора минимального кода

погрешности, вторые входы которых подподключены соответственно к седьмому и восьмому выходам блока управления, причем выход блока выбора минимального кода погрешности соединен с третьим входом блока свертки кода.

Источники информации, принятые во внимание при экспертизе

/ VV /

ю

/V

Авторы

Даты

1982-08-23—Публикация

1981-01-08—Подача