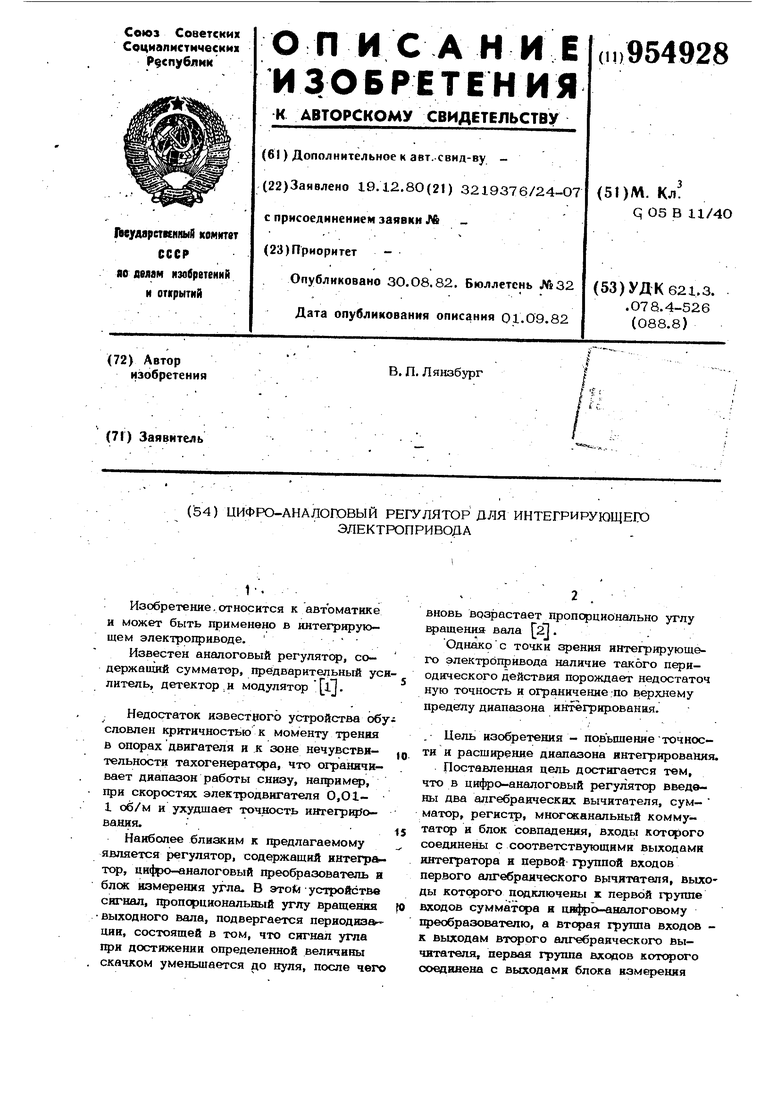

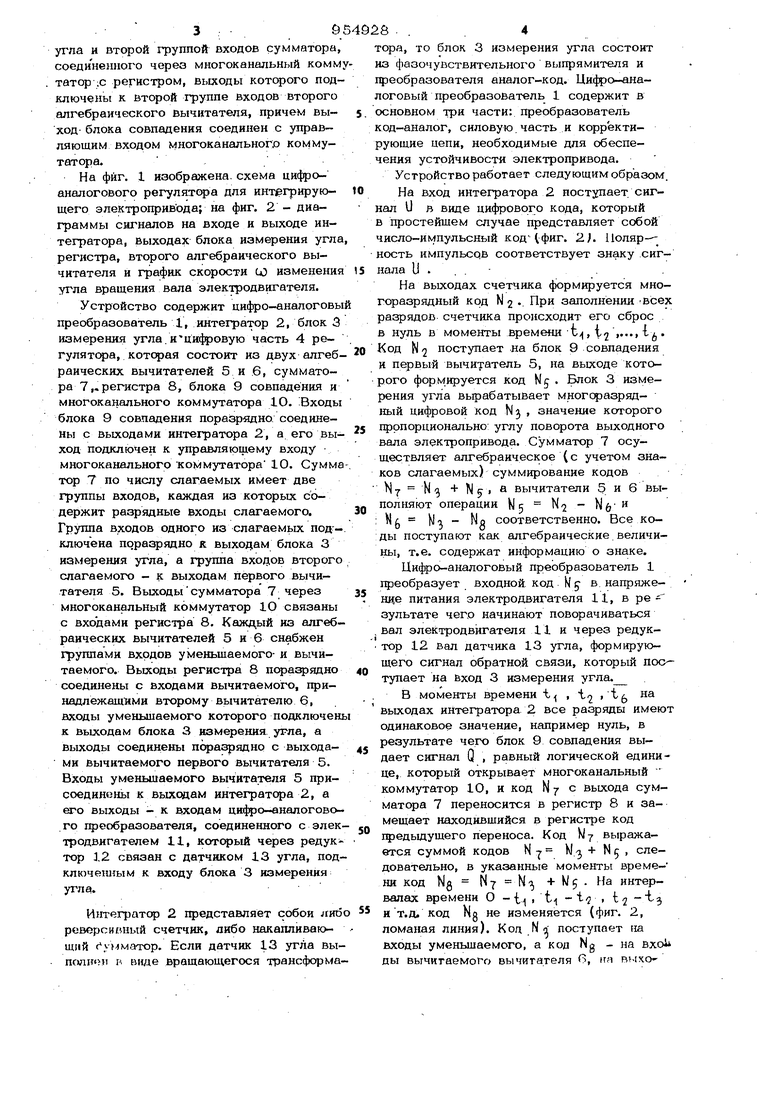

. . 1- - Изобретение.относится к автоматике и может быть применено в интегрирующем электроприводе. Известен аналоговый регулятср, содержащий сумматор, предварительный ус литель, детектор , и модулятор . Недостаток известного устройства об словлен критичностью к моменту трения в опорах двигателя и к зоне нечувствительности тахогенератора, что ограничивает диапазон работы снизу, на1фим э, при скоростное электродвигателя О,О11 об/м и ухудшает точность ингегрщ ования.. Наиболее близким к Щ)едлагаемому является регулятор, содержащий интегратор, цифро-аналоговый преобразователь и блок намерения угла, В этой устройстве сигнал, пропорциональный углу вращения выходного вала, подвергается периодиза дии, состоящей в том, что сигнал угла при достижении определенной величины скачком уменьшается iio нуля, после чег вновь возрастает пропорционально углу вращения вала 2.. Однакос точки зрения интегрирующего электропривода наличие такого периодического действия порождает недостаточ ную точность и ограничение ;по верхнему пределу диапазона игггегрирования. Цель изобретения - повьш1ение точности и расширение диапазона интегрирования. Поставленная цель достигается тем, что в цифро-аналоговый регулятор введены два алгебраических вычитателя, сумматор, регистр, многоканальный коммутатор и блок совпадения, входы которого соединены с соответствующими выходами интегратора и первой группой входов первого алгебраического вычятателя, выходы которого подключены ж. первой группе входов сумматора в цн| ро-аналоговому преобразователю, а вторая группа входов к выходам второго алгебраического вычитателя, первая группа входов котсфого соединена с выходами блока измерения 3 D угла и второй группой входов сумматора, соединенного через многоканальный комм татор ;С регистром, выходы которого подключены к второй группе входов второго алгебраического вычнтателя, причем выход блока совпадения соединен с управляющим входом многоканального коммутатора. На фиг. 1 изображена, схема цифроаналогового регулятора для интегрирующего электропривода; на фиг. 2 - диаграммы сигналов на входе и выходе интегратора, выходах блока измерения угла регистра, второго алгебраического вычитателя и график скорости со изменения угла вращения вала электродвигателя. Устройство содержит цифро-аналоговы преобразователь 1, интегратор 2, блок 3 измерения угла, ицифровую часть 4 регулятора, которая состоит из двух алгебраических вычитателей 5 и .6, сумматора 7,.регистра 8, блока 9 совпадения и многоканального коммутатора 1О. Входы блока 9 совпадения поразрядно: соединены с выходами интегратора 2, а его выход подключен к управляющему входу многоканального коммутатора 10. Сумма тор 7 по числу слагаемых имеет две группы входов, каждая из которых содержит разрядные входы слагаемого. Группа входов одного из слагаемьгх подгключена поразрядно к выходам блока 3 измерения угла, а группа входов второго слагаемого - к выходам первого вычитателя 5. Выходысумматора 7 через многоканальный коммутатор 1О связаны с входами регистра 8. Каждый из алгебраических вычитателей 5 и б снабжен группами входов уменьшаемого- и вычитаемого. Выходы регистра 8 поразрядно соединены с входами вычитаемого, принадлежащими Второму вычитателю 6, входы уменьшаемого которого подключены к выходам блока 3 измерения угла, а выходы соединены поразрядно с выходами вычитаемого первого вычитателя 5. Входы уменьшаемого вычитателя 5 присоединены к выходам интегратфа 2, а его выходы - к входам UH(j o-аналоговоГО преобразователя, соединенного с электродвигателем 11, который через редуктор 12 связан с датчиком 13 угла, подключенным к входу блока 3 измерения угла. Интегратор 2 представляет собой либо реверсивный счетчик, либо накапливающий (Сумматор. Если датчик 13 угла выпс ли п Р В1ще вращающегося трансформа- 8. то блок 3 измерения угла состоит тора из фазочувствительного выпрямителя и преобразователя аналог-код. Цн4ро-аналоговый преобразователь 1 содержит в основном три части: преобразователь код-аналог, силовую.часть и корректирующие цепи, необходимые для обеспечения устойчивости электропривода. Устройство работает следующим образом. На вход интегратора 2 поступает/сигнал U в виде цифрового кода, который в простейшем случае представляет собой число-импульсный к одЧ фиг. 2 К Иолярность импульсов соответствует знаку сигнала U . . . -. На выходах счетчика формируется многоразрядный код N j .. При заполнении .всех разрядов счетчика происходит его сброс в нуль в моменты времени-t, 12,..., i . Код N5 поступает «а блок 9 совпадения « вычиуатель 5 на выходе которого формируется код Nj Блок 3 измерения угла вырабатывает многсразрядный цифровой код N . значение которого пропорционально: углу поворота выходного электропривода. Сумматор 7 осуществляет алгебраическое (с учетом знаков слагаемых) суммирование кодов +Neia вычитатели 5 и 6 выполняют операции Uc N2-N6 На- No соответственно. Все коды поступают как алгебраические величины, т.е. содержат информацию о знаке. Цифро-аналоговый преобразователь 1 преобразует входной код W § в напряжение питания электродвигателя 11, в результате чего начинают поворачиваться вал электродвигателя 11 и через редуктор 12 вал датчика 13 утла, формирующего сигнал обратной связи, который поступает на Вход 3 измерения угла. В моменты времени t , t выходах интегратора 2 все разряды имеют одинаковое значение, например нуль, в результате чего блок 9 совпадения выдает сигнал Q , равный логической единице, который открывает многоканальный коммутатор 1О, и код N 7 с выхода сумматора 7 переносится в регистр 8 и замешает находившийся в регистре код находившийся в регистре J.UM хфедьщушего переноса. Код N7 ыража« ся суммой кодов N N.3 + N5 , следовательно, в указанные моменты време- ни код Ng N7 + К/5 . На интервалах времени О - i , t - t , t и т.д. код Ng не изменяется (фиг. 2, ломаная линия). Код N i поступает fia входы уменьшаемого, а код Ng - на Bxoi ды вычитаемого вычигателя в, ия выхо де которого формируется код N g (изображен ступенчатой кривой). В моменты времени ii , tj т.д. код N N3 - ( N3 N5) -.N5. Вычитатель 5 выполняет функции сравнивающего устройства замкнутой системы регулирования, на Входы уменьшаемого кото рого подается код задающего воздействи на входы вычитаемого - код сигн ла обратной связи N. На выходе вычитателя формируется код сигнала ощибки Н5 N,2-N6 В моменты времени t; , t и т.д. коды и Мб вьфакаются: О и N -N5 Подставив эти значения и предьщущее равенство, получим NC Nj, что означает запоминание величины сигнала ошибки на время обнуления кода Мо. Это запоминание происи,1 f,ff ходит, в регистре 8 и формируется путем подачи кода Nj на одну из двух групп входов сумматора 7. Подача кода сигнас ла ошибки fi 5 вход сумматора 7 обес печивает непрерывность этого сигнала на входе цифро-аналогового преобразователя 1, а следовательно, и непрерывность выходного напряжения преобразователя 1 и момента двигателя несмотря на периодич ность сигналов N 2 и N , . Непрерывность момента на валу двигателя приводит к непрерывному изменению угла поворота вала и кода N3 в соответствии с кривой 14 (фиг. 2), при. этом на интервалах времени О - i , i -ii .i-i -i- я т.д угол поворота вала и код N з отслеживают изменение, сигнала U , а накопленная постоянная составляющая кода N умень шается кодом Ng . В результате скорость Cjj изменения угла вращения вала электродвигателя изменяется во времени в соответствии с кривой 15 (фиг. 2). Необходимость формирования кода No с последующим периодическим вычитанием его из кода И с помощью вычитателя 6 вытекает из необходимости обеспечения помехоустойчивости регулятора. Критичными к помехам 5шляются узлы памяти (интегратор 2 и регистр 8) Если бы не было операции вычитания кодов N2 - Ng то код интегратора 2должен был бы изменяться не периодически, а непрерывно, так же как код М 3 - по кривой 14. При этом емя интегрирования было бы неограниченным и воздействие помехи привело бы к потере накопленной в интеграторе 2 информации и неправильной работе привода. В предлагаемой интегратор 2 периодически обнуляется и воздействие помехй может отразиться на работе привода лишь кратковременно, между двумя очередными обнулениями. В регистре 8 информация обнуляется .при обнуления интегратора 2, причв М запись кода в регистр 8 пpQИcxoдит от помехоустойчивого блока 3 измерения угла...; . Нижний предел диапазона интегрщзования приншшиально не ограничен, т.е. минимальная скорость интегрирования может быть какой угодно малой величиной. Практически для этого следует уменыиать цену младшего разряда кода N j путем увеличения его разрядности. Верхний гредел ограничивается лишь частотными свойствами микросхем. Таким образом, щэедлагаемое устройство обеспечивает практически неограниченный снизу диапазон изменения входного интегрируемого сигнала и высокую точность интегрирования. Формула изобретение Цифро-аналоговый регулятор для интегрирующего электропривода, содержащий интегратор, цифро-аналоговый преобразователь, блок измерения угла, о тличающийся тем, что, с целью повышения точности и расширения диапазона интегрирования, в него введены два алгебраических вычитателя, сумматор, регистр, многоканальный коммутатор и блок совпадения, входы которого соединены с срответствующими выходами интегратора и первой группой входов первого алгебраического вычитателя, выходы которого подключены к первой груп-пе входов сумматора и ци4ро-аналоговому преобразователю, а вторая группа входов - к выходам второго алгебраического, вычитателя, первая группа входов которого соединена с выходами блока измерения угла и Итерой группой входов сумматора, соединенного через многока нальный коммутатор с регистром, выходы которого подключены к второй группе входов второго алгебраического вычитатег пя, причем выход блока совпадения соеаинен с управляющим входом многоканального коммутатора. Источники :инфс мации, принятые во внимание при экспертизе 1.Фабрикант Е.А., Воскобойников Р.Л. Интвгр1фующий щжвод. Л., Энергия , 198О, с. 29. 2.Авторское свидетельство СССР М 736318, кл. Н О2 Р 5/Ов, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматической проверки преобразователя угол-код | 1987 |

|

SU1441478A1 |

| Многоканальный преобразователь частоты в код | 1980 |

|

SU936422A1 |

| Спектральный анализатор | 1977 |

|

SU789866A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Аналого-цифровое устройство для решения системы дифференциальных уравнений | 1987 |

|

SU1462378A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Регулятор | 1990 |

|

SU1803906A1 |

| Цифровое устройство для одноканального фазового управления вентильным преобразователем | 1978 |

|

SU765976A1 |

Авторы

Даты

1982-08-30—Публикация

1980-12-19—Подача