Изобретение Т)тносится к автоматике и Bbi4HCJEHTe.nbHovi технике и предназначено для лвтомлтического измерения погрешности преобразователей угл поворота вала в код.

Цель изобретения - повышение информативности устройства за счет обепечения возможности определения систематических и случайных погреш-

но стей.

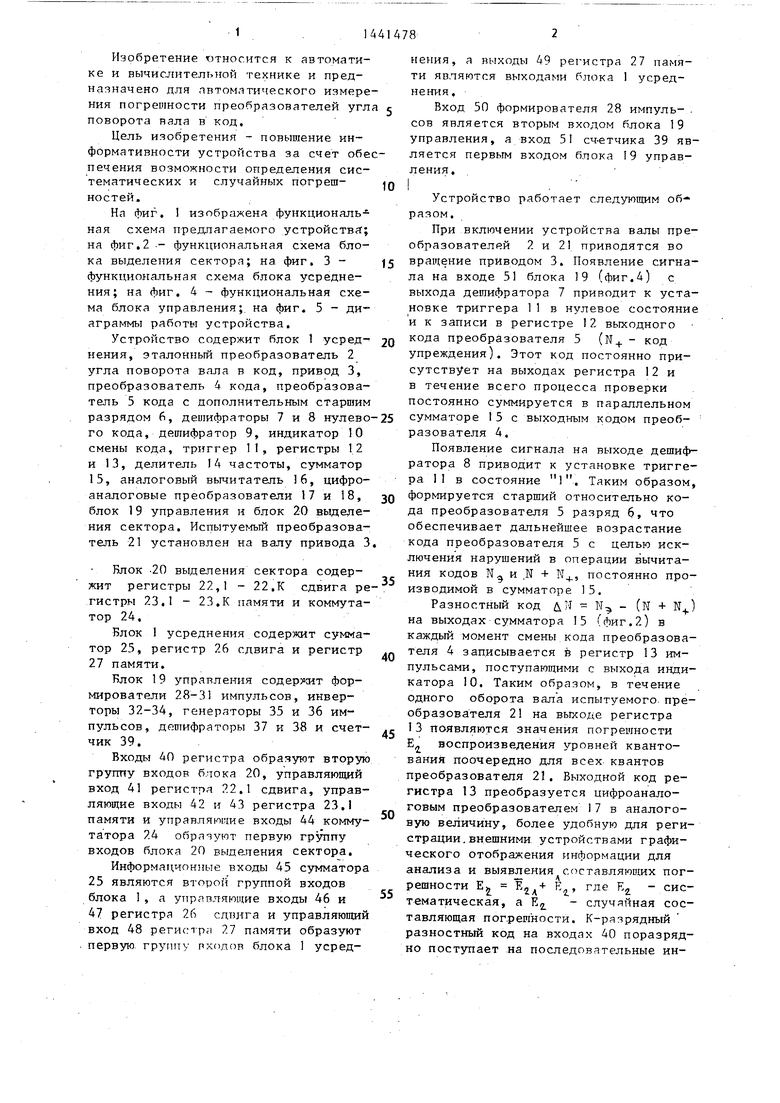

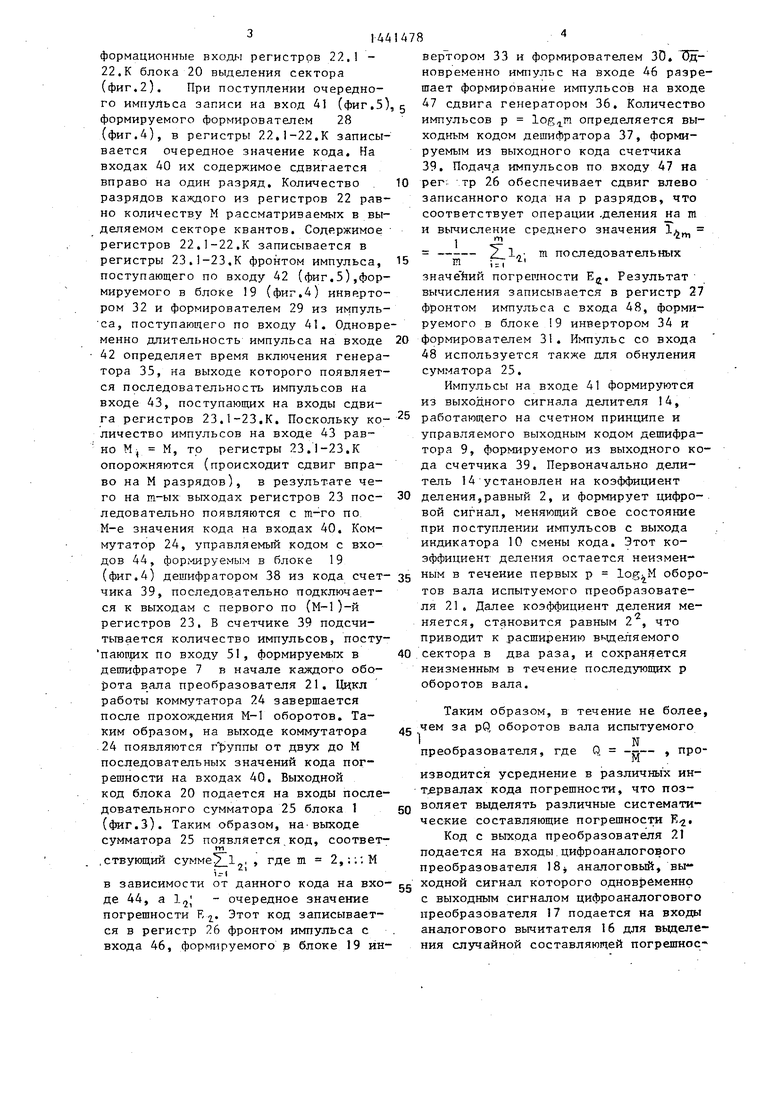

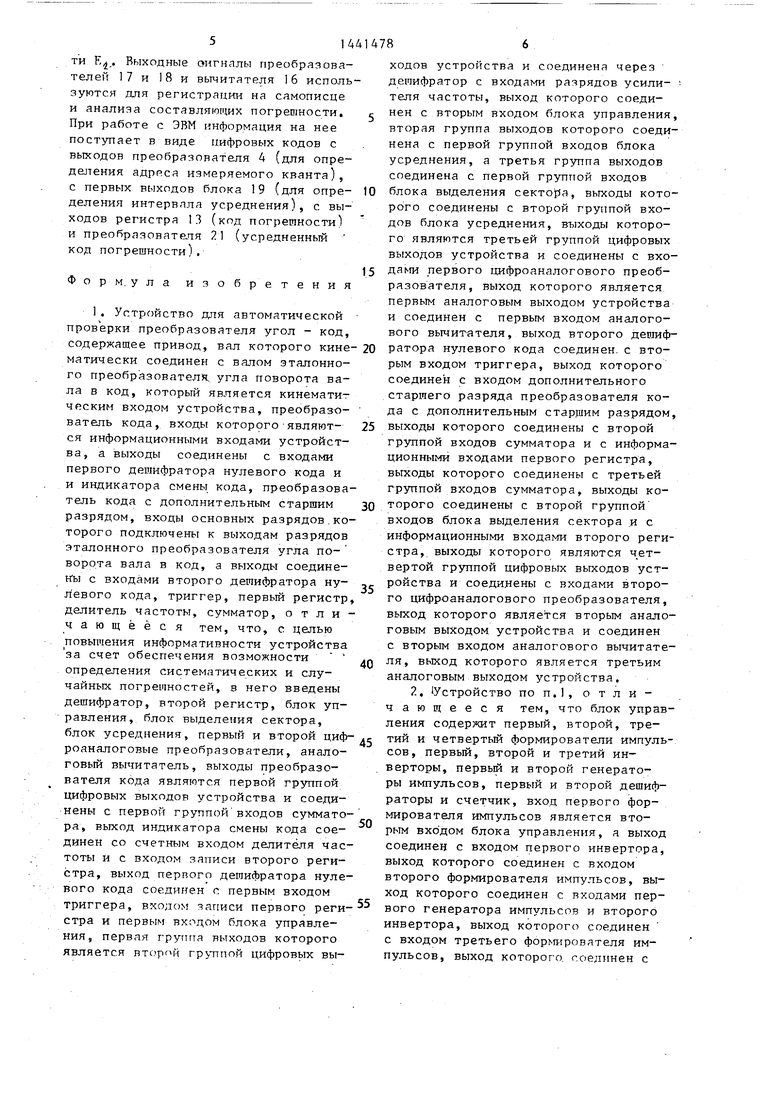

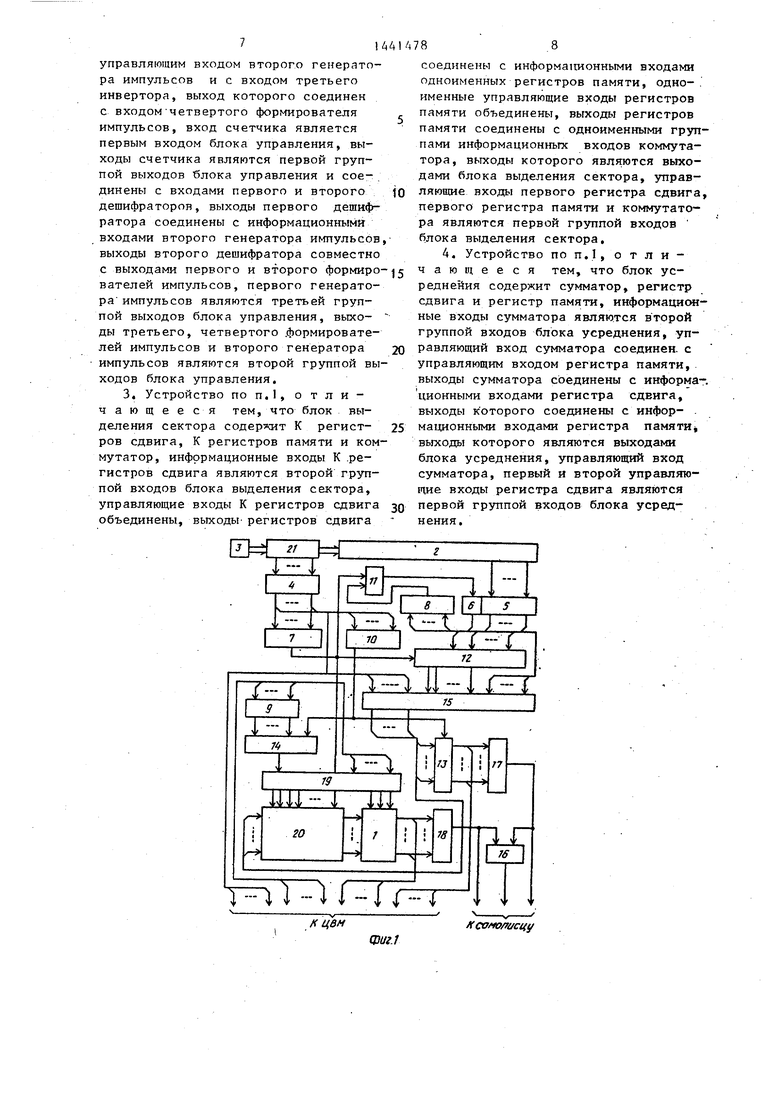

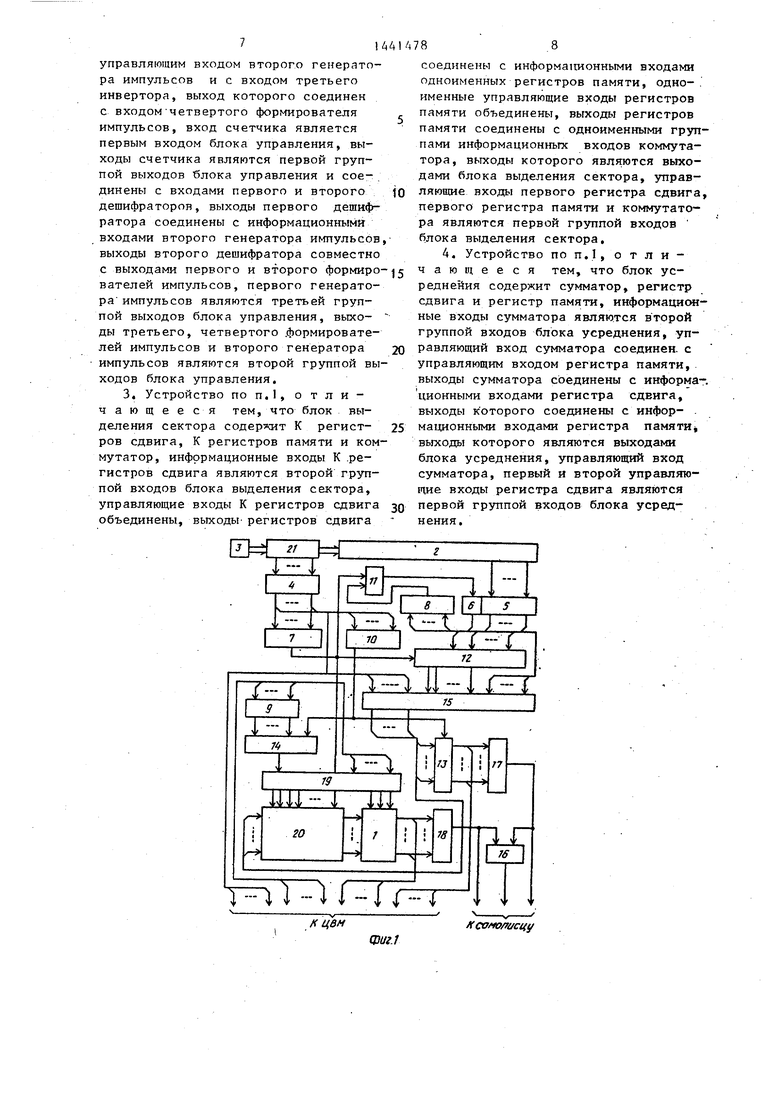

На фиг, I изображена функциональная схема предлагаемого устройств ; на фиг,2 .- функциональная схема блока выделения сектора; на фиг, 3 - функционапьная схема блока усреднения; на фиг, 4 - функциональная схема блока управления;, на фиг. 5 - диаграммы работы устройства.

Устройство содержит блок 1 усред-- нения, эталонный преобразователь 2 угла поворота вала в код, привод 3, преобразователь 4 кода, преобразователь 5 кода с дополнительным старшим разрядом 6, дешифраторы 7 и 8 нулево го кода, дешифратор 9, индикатор 10 смены кода, триггер 11, регистры 12 и 13, делитель 14 частоты, сумматор 15, аналоговый вычитатель 6, цифро- аналоговые преобразователи 17 и 18, блок 19 управления и блок 20 вьщеле- ния сектора. Испытуемый преобразователь 21 установлен на валу привода 3

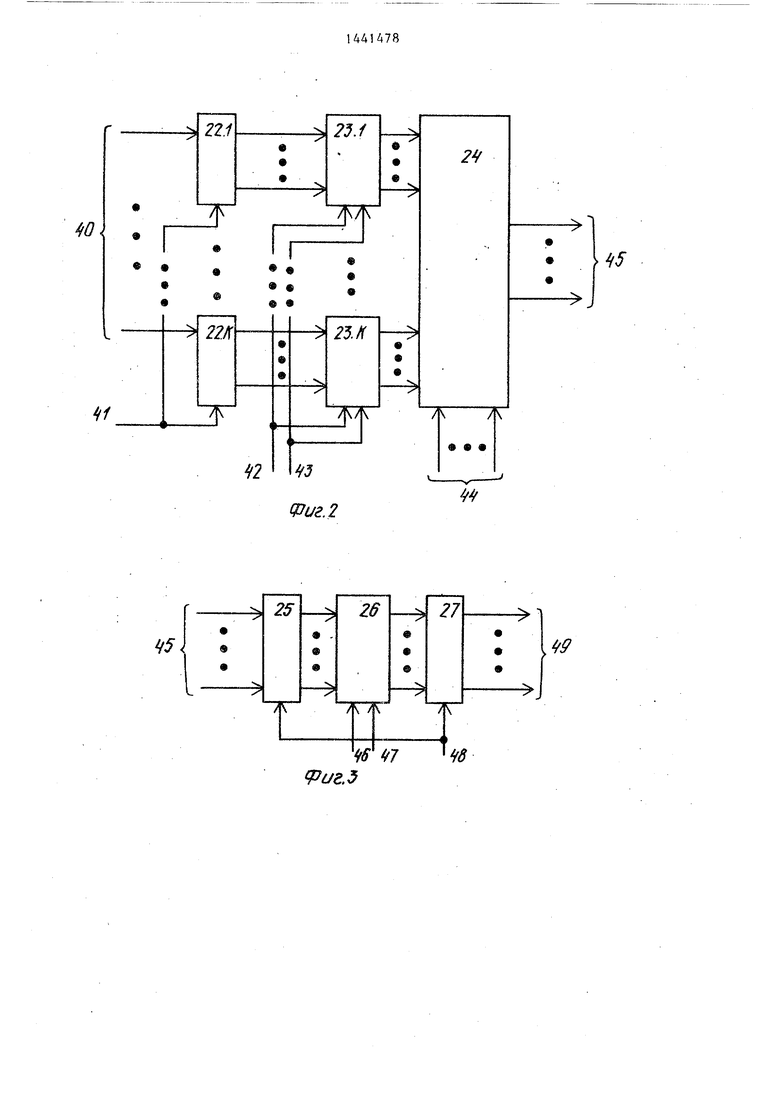

Блок -20 выделения сектора содержит регистры 22,1 - 22,К сдвига ре гистры 23,1 - 23,К памяти и коммутатор 24,

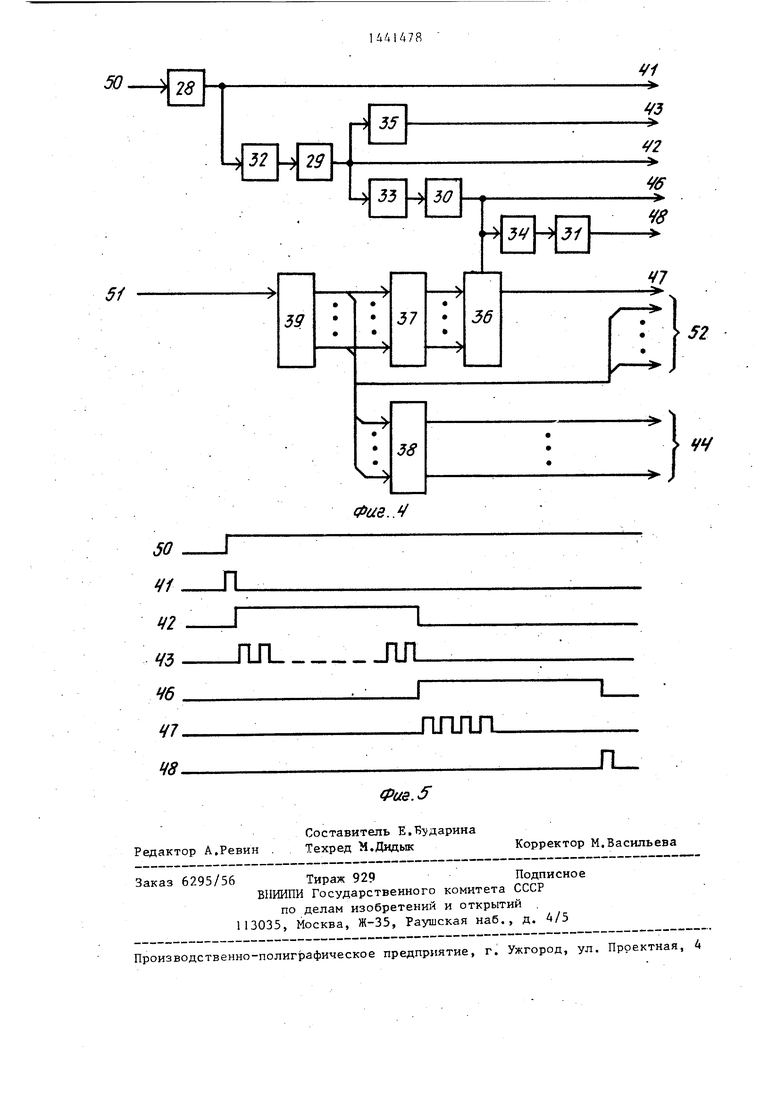

Блок I усреднения содержит сумматор 25, регистр 26 сдвига и регистр 27 памяти.

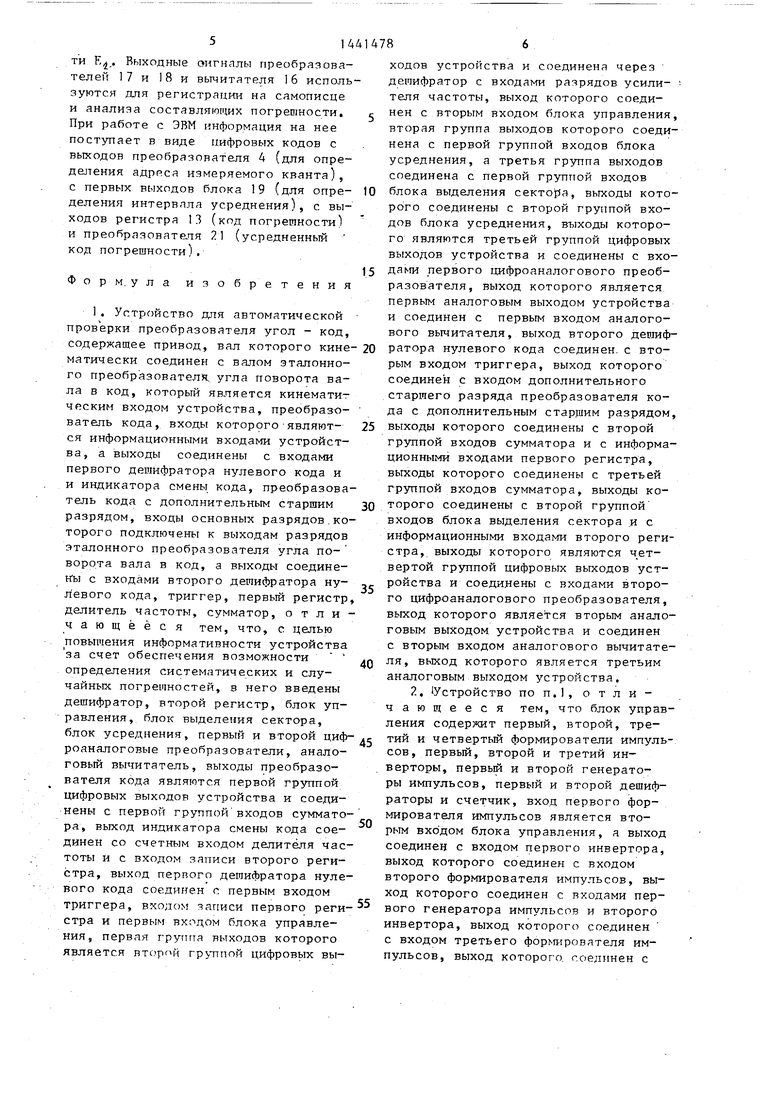

Блок 19 управления содержит формирователи 28-3 импульсов, инверторы 32-34, генераторы 35 и 36 импульсов, дешифраторы 37 и 38 и счет- чик 39,

Входы 40 periicTpa образуют вторую группу входов блока 20, управляющий вход 41 регистра 22,1 сдвига, управляющие входы 42 и 43 регистра 23,1 памяти и управляющие входы 44 коммутатора 24 образуют первую группу входов блока 20 выделения сектора,

Информационные входы 45 сумматора 25 являются второй группой входов блока 1, а управляющие входы 46 и 47 регистра 26 сдвига и управляющий вход 48 регистр; 27 памяти образуют . первую, группу пходов блока 1 усред

0

0

нения, а выходы 49 регистра 27 памяти являются выходами блока 1 усред- нент-1я.

Вход 50 формирователя 28 импуль- . сов является вторым входом блока 19 управления, а вход 51 сч-етчика 39 является первым входом блока 19 управления,

Г .

Устройство работает следующим образом.

При включении устройства валы преобразователей 2 и 21 приводятся во вращение приводом 3, Появление сигнала на входе 51 блока 19 (фиг,4) с выхода дешифратора 7 приводит к установке триггера 11 в нулевое состояние и к записи в регистре 12 выходного кода преобразователя 5 (N+ - код упреждения). Этот код постоянно присутствует на выходах регистра 12 и в течение всего процесса проверки постоянно суьтмируется в параллельном сумматоре 15 с выходным кодом преоб- разователя 4,

Появление сигнала на выходе дешифратора 8 приводит к установке триггера 1 I в состояние 1, Таким образом, формируется старший относительно кода преобразователя 5 разряд 6, что обеспечивает дальнейшее возрастание кода преобразователя 5 с целью исключения нарушений в операции вычитания кодов Ng и ,N + N4., постоянно производимой в сумматоре 15.

Разностный код дИ - W - (N + N) на выходах сумматора 15 (фиг,2) в каждый момент смены кода преобразователя 4 записывается в регистр 13 импульсами, поступающими с выхода индикатора 10, Таким образом, в течение одного оборота вала испытуемого, преобразователя 21 на выходе регистра 13 появляются значения погрешности Е воспроизведения уровней квантования поочередно для всех квантов преобразователя 21, Выходной код регистра 13 преобразуется цифроанало- говым преобразователем 17 в аналоговую величину, более удобную для регистрации, внешними устройствами графического отображения информации для анализа и выявления составляющих погрешности Е, К., где Ej, - систематическая, а Ej - случайная составляющая погрешности. К-разрядный разностный код на входах 40 поразрядно поступает на последовательные ин314

формационные входы регистров 22,1 - 22.К блока 20 выделения сектора (фиг,2). При поступлении очередного импульса записи на вход 41 (фиг.5 формируемого формирователем 28 (фиг.4), в регистры 22.1-22.К записывается очередное значение кода. На входах 40 их содержимое сдвигается вправо на один разряд. Количество разрядов каждого из регистров 22 равно количеству М рассматриваемых в выделяемом секторе квантов. Содержимое регистров 22.1-22.К записывается в регистры 23.1-23,К фронтом импульса, поступающего по входу 42 (фиг,5),формируемого в блоке 19 (фиг.4) инвертором 32 и формирователем 29 из импуль- са, поступающего по входу 41. Одновременно длительность импульса на входе 42 определяет время включения генератора 35, на выходе которого появляется последовательность импульсов на входе 43, поступающих на входы сдвига регистров 23,1-23.К. Поскольку количество импульсов на входе 43 равно Mj М, то регистры 23.1-23.К опорожняются (происходит сдвиг вправо на М разрядов), в результате чего на т-ых выходах регистров 23 последовательно появляются с т-го по М-е значения кода на входах 40. Коммутатор 24, управляемый кодом с входов 44, формируемым в блоке 19 (фиг,4) дешифратором 38 из кода счетчика 39, последовательно подключается к выходам с первого по (М-1)-й регистров 23, В счетчике 39 подсчи- тьгаается количество импульсов, посту- паюп их по входу 51, формируемых в дешифраторе 7 в начале каждого оборота вала преобразователя 21. Цккл работы коммутатора 24 завершается после прохождения М-1 оборотов. Таким образом, на выходе коммутатора 24 появляются от двух до М последовательных значений кода погрешности на входах 40. Выходной код блока 20 подается на входы последовательного сумматора 25 блока 1 (фиг.З), Таким образом, на-выходе сумматора 25 появляется,код, соответtn

,ствующий сумме , , где m 2,::; М

В зависимости от данного кода на входе 44, а - очередное значение погрешности , , Этот код записывается в регистр 26 фронтом импульса с входа 46, формируемого в блоке 19 ин8

вертором 33 и формирователем 30. Од- новременно импульс на входе 46 разрешает формирование импульсов на входе

47 сдвига генератором 36. Количество импульсов р определяется выходным кодом дешифратора 37, формируемым из выходного кода счетчика 39. Подача импульсов по входу 47 на

per; тр 26 обеспечивает сдвиг влево записанного кода на р разрядов, что соответствует операции .деления на m и вычисление среднего значения IA.-.

1

m последовательных

m

значений погрешности Eg, Результат вычисления записывается в регистр 27 фронтом импульса с входа 48, формируемого в блоке 9 инвертором 34 и

формирователем 31. Импульс со входа 48 используется также для обнуления сумматора 25.

Импульсы на входе 41 формируются из выходного сигнала делителя 14,

работающего на счетном принципе и управляемого выходным кодом дешифратора 9, формируемого из выходного кода счетчика 39, Первоначально делитель 14 установлен на коэффициент

деления,равный 2, и формирует цифро-. вой сигнал, меняющий свое состояние при поступлении импульсов с выхода индикатора 10 смены кода. Этот коэффициент деления остается неизменным в течение первых р оборотов вала испытуемого преобразователя 21, Далее коэффициент деления меняется, становится равным 2 , что приводит к расширению в зделяемого

сектора в два раза, и сохраняется неизменным в течение последующих р оборотов вала.

Таким образом, в течение не более, 45 чем за pQ оборотов вала испытуемого

1N

преобразователя, где Q , производится усреднение в различных интервалах кода погрешности, что поз

воляет выделять различные систематические составляющие погрешности Е.

Код с выхода преобразователя 21 подается на входы цифроаналогового преобразователя 18 аналоговый, выг- ходной сигнал которого одновременно с выходным сигналом цифроаналогового преобразователя 17 подается на входы аналогового вычитателя 16 для вьщеле- ния случайной составляющей погрешнос

ти Ej), Выходные оигналы преобразователей 17 и 18 и вьтчитателя 16 используются для регистрации на самописце и анализа составляющих погрешности. При работе с ЭВМ информация на нее поступает в виде цифровых кодов с выходов преобразователя 4 (для определения адреса измеряемого кванта), с первых выходов блока 19 (для определения интервала усреднения), с выходов регистра 13 (кпд погрешности) и преобразователя 21 (усредненный код погрешности).

Форм.ула изобретения

1, Устройство для автоматической проверки преобразователя угол - код, содержащее привод, вал которого кинематически соединен с валом эталонного преобразователя, угла поворота вала в код, который является кинематическим входом устройства, преобразо- ватель кода, входы которого-являются информационными входами устройства, а выходы соединены с входами первого дешифратора нулевого кода и и индикатора смены кода, преобразователь кода с дополнительным старшим разрядом, входы основных разрядов.которого подключены к выходам разрядов эталонного преобразователя угла по- ворота вала в код, а выходы соедине- Hbi с входами второго дешифратора ну- л евого кода, триггер, первый регистр делитель частоты, сумматор, отличающееся тем, что, с целью повышения информативности устройства за счет обеспечения возможности определения систематических и случайных погрешностей, в него введены дешифратор, второй регистр, блок управления, блок выделения сектора, блок усреднения, первый и второй циф- роаналоговые преобразователи, аналоговый вычитатель, выходы преобразователя кода являются первой группой цифровых выходов устройства и соединены с первой группой входов сумматора, выход индикатора смены кода соединен со счетным входом делителя частоты и с входом записи второго регистра, выход первого дешифратора нулевого кода соединен с первым входом триггера, входом записи первого регистра и первым входом блока управления, первая групгта выходов которого является втс рпй группой цифровых вы

0

5

20

25

30

35

40

45

50

55

ходов устройства и соединена через дешифратор с входами разрядов усили- теля частоты, выход которого соединен с вторым входом блока управления, вторая группа выходов которого соединена с первой группой входов блока усреднения, а третья группа выходов соединена с первой группой входов блока выделения сектора, выходы которого соединены с второй группой входов блока усреднения, выходы которого являются третьей группой цифровых выходов устройства и соединены с вхо- даьш первого цифроаналогового преобразователя, выход которого является первым аналоговым выходом устройства и соединен с первым входом аналогового вычит-ателя, выход второго дешифратора нулевого кода соединен, с вторым входом триггера, выход которого соединен с входом дополнительного старшего разряда преобразователя кода с дополнительным старшим разрядом, выходы которого соединены с второй группой входов сумматора и с информационными входами первого регистра, выходы которого соединены с третьей группой входов сумматора, выходы которого соединены с второй группой входов блока выделения сектора и с информационными входами второго регистра, выходы которого являются вертой группой цифровых выходов устройства и соеди)ены с входами второго цифроаналогового преобразователя, выход которого является вторым аналоговым выходом устройства и соединен с вторым входом аналогового вычитате- ля, выход которого является третьим аналоговым выходом устройства,

.. Устройство по п., о т л и - чающееся тем, что блок управления содержит первый, второй, третий и четвертый формирователи импульсов, первый, второй и третий инверторы, первый и второй генераторы импульсов, первый и второй дешифраторы и счетчик, вход первого формирователя импульсов является вторым входом блока управления, а выход соединен с входом первого инвертора, выход которого соединен с входом второго формирователя импульсов, выход которого соединен с входами первого генератора импульсов и второго инвертора, выход которого соединен с входом третьего формирователя импульсов, выход которого, coejniHeH с

управляющим входом второго генератора импульсов и с входом третьего инвертора, выход которого соединен с входом четвертого формирователя , импульсов, вход счетчика является первым входом блока управления, выходы счетчика являются первой группой выходов блока управления и сое- ; динены с входами первого и второго (о дешифраторов, выходы первого дешифратора соединены с информационными входами второго генератора импульсов,- выходы второго дешифратора совместно

соединены с информационными входами одноименных регистров памяти, одно- именные управляющие входы регистро памяти объединены, выходы регистров памяти соединены с одноименными гр пами информационных входов коммута тора, выходы которого являются выхо дами блока выделения сектора, управ ляющие входы первого регистра сдвиг первого регистра памяти и коммутат ра являются первой группой входов блока выделения сектора,

4. Устройство по П.1, о т л и с выходами первого и второго формиро- 5 чаюв1ееся тем, что блок усвателей импульсов, первого генератора импульсов являются третьей группой выходов блока управления, выходы третьего, четвертого .формирователей импульсов и второго генератора 20 импульсов являются второй группой выходов блока управления,

3. Устройство по п,1, отличающееся тем, что блок выделения сектора содержит К регист- 25 ров сдвига, К регистров памяти и коммутатор, информационные входы К .регистров сдвига являются второй группой входов блока выделения сектора, управляющие входы К регистров сдвига зо объединены, выходы-регистров сдвига

реднейия содержит сумматор, регистр сдвига и регистр памяти, информаци ные входы сумматора являю.тся в торой группой входов блока усреднения, уп равляющий вход сумматора соединен, управляющим входом регистра памяти выходы сумматора соединены с инфор ционными входами регистра сдвига, выходы к оторого соединены с информационными входами регистра памят выходы которого являются выходами блока усреднения, управляющий вход сумматора, первый и второй управля щие входы регистра сдвига являются первой группой входов блока усреднения.

соединены с информационными входами одноименных регистров памяти, одно-, именные управляющие входы регистров памяти объединены, выходы регистров памяти соединены с одноименными группами информационных входов коммутатора, выходы которого являются выходами блока выделения сектора, управляющие входы первого регистра сдвига, первого регистра памяти и коммутатора являются первой группой входов блока выделения сектора,

4. Устройство по П.1, о т л и чаюв1ееся тем, что блок усреднейия содержит сумматор, регистр сдвига и регистр памяти, информационные входы сумматора являю.тся в торой группой входов блока усреднения, управляющий вход сумматора соединен, с управляющим входом регистра памяти, выходы сумматора соединены с информа ционными входами регистра сдвига, выходы к оторого соединены с информационными входами регистра памяти выходы которого являются выходами блока усреднения, управляющий вход сумматора, первый и второй управляющие входы регистра сдвига являются первой группой входов блока усреднения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1797161A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Преобразователь сдвига фазы в код | 1984 |

|

SU1193812A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для автоматического измерения погрешности преобразователей угла поворота вала в код. Целью изобретения является повьшение информативности устройства за счет обеспечения возможности определения систематических и случайных погрешностей. Для этого в устройство для автоматической проверки преобразователя угла поворота вала в код, содержащее привод, эталонный преобразователь, преобразователь кода, преобразователь кода с дополнительным старшим разрядом, триггер, два дешифратора нулевого кода, первый регистр, индикатор смены кода, сумматор, делитель частоты, введены дешифратор, второй регистр, блок управления, блок выделения сектора, блок усреднения, два цифроаналоговых преобразователя,аналоговый вычитатель. Поставленная цель достигается усреднением результатов измерения погрешности в заданном интервале углов поворота вала преобразователя. Изменение в широком диапазоне заданного интервала позволяет последовательно выделять и исследовать различные систематические составляющие погрешности воспроизведения. Сравнением результатов измерения по двум отдельным каналам достигается выделение случайной составляющей погрешности. Полный цикл измерения завершается не более, чем за N-M оборотов вала, где N - информационная емкость испытуемого преобразова- зователя угла поворота вала в код, а М - количество рассматриваемого в выделяемом секторе квантов кода испытуемого преобразователя. 3 з.п. ф-лы, 5 ил, (О (Л 1 4 4 00

f ЦВМ

Ксомот/сцу

(Риг.2

t/г.

9

50 4i Ц2 45 46

47 48

L

.JIJL

Составитель Е.Вударина Редактор А.Ревин . Техред М.ДидыкКорректор М.Васильева

Заказ 6295/56 Тираж

БНИИПИ Государственного комитета CCCt по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг..4

ЛЛЛЛ

JU.

Фие.5

| Устройство для определения погрешности преобразователя угла поворота вала в код | 1981 |

|

SU993307A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для автоматической проверки преобразователя угол-код | 1972 |

|

SU447742A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-30—Публикация

1987-04-22—Подача