блок задержки (17), четыре элемента И-ИЛИ (18-21,25), три элемента И (22-24, 26). Предлагаемая реализация регулятора позволяет осуществить защиту привода от сбоя цифровой части привода, так как в течение времени сбоя происходит медленное нарастание рассогласования, пропорциональное скоростной ошибке привода. 5 ил., 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля электропривода | 1987 |

|

SU1481717A1 |

| Устройство для регулирования расхода | 1986 |

|

SU1377832A1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Система позиционного управления электроприводом | 1985 |

|

SU1312521A1 |

| Система для передачи телеизмерительной информации | 1982 |

|

SU1113832A1 |

| Цифровая система регулирования скорости центробежного аппарата | 1983 |

|

SU1176302A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство управления движением транспортного средства | 1990 |

|

SU1837328A1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

Изобретение относится к автоматике и может быть использовано в системах автоматического управления технологическими процессами. Целью является повышение точности. Регулятор содержит электропривод (1), блок анализа ускорения (2), блок анализа рассогласования (3), два вычитате- ля (4, 5), два компаратора (6, 7), сумматор (8), делитель частоты (9), четыре регистра (ID- 13), интегратор (14), два триггера (15, 16),

Изобретение относится к автоматике и может быть использовано в системах автоматического управления технологическими процессами.

Цель изобретения - повышение точности регулятора.

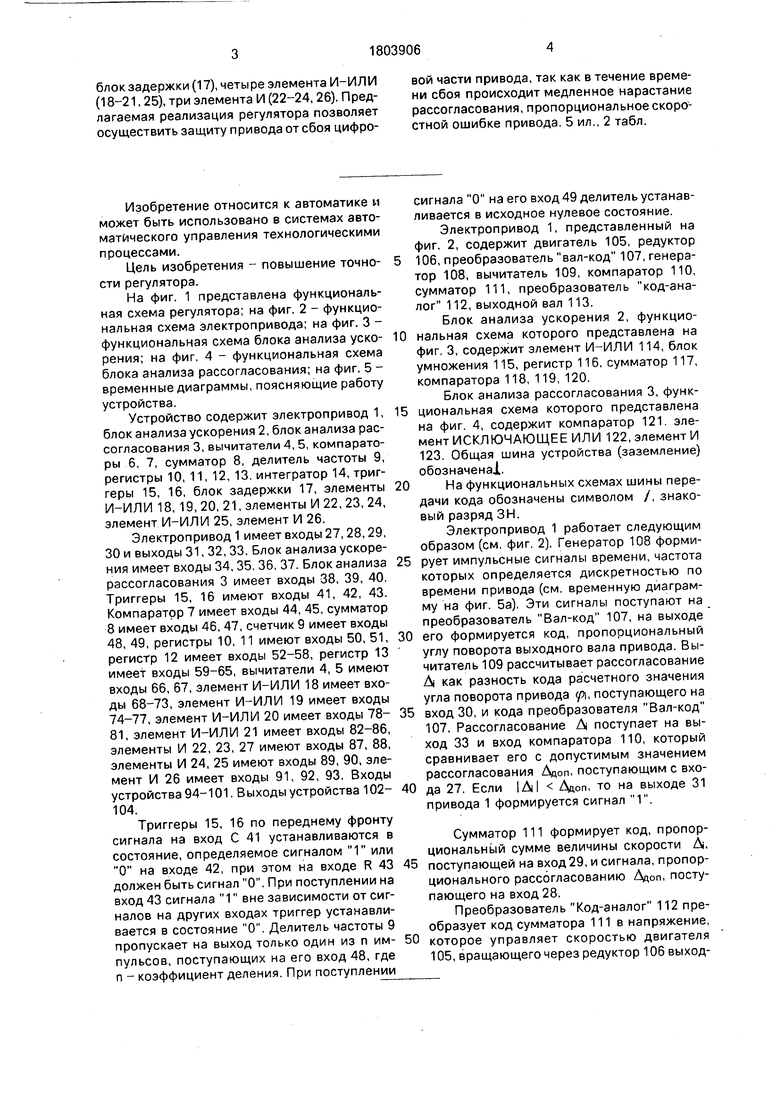

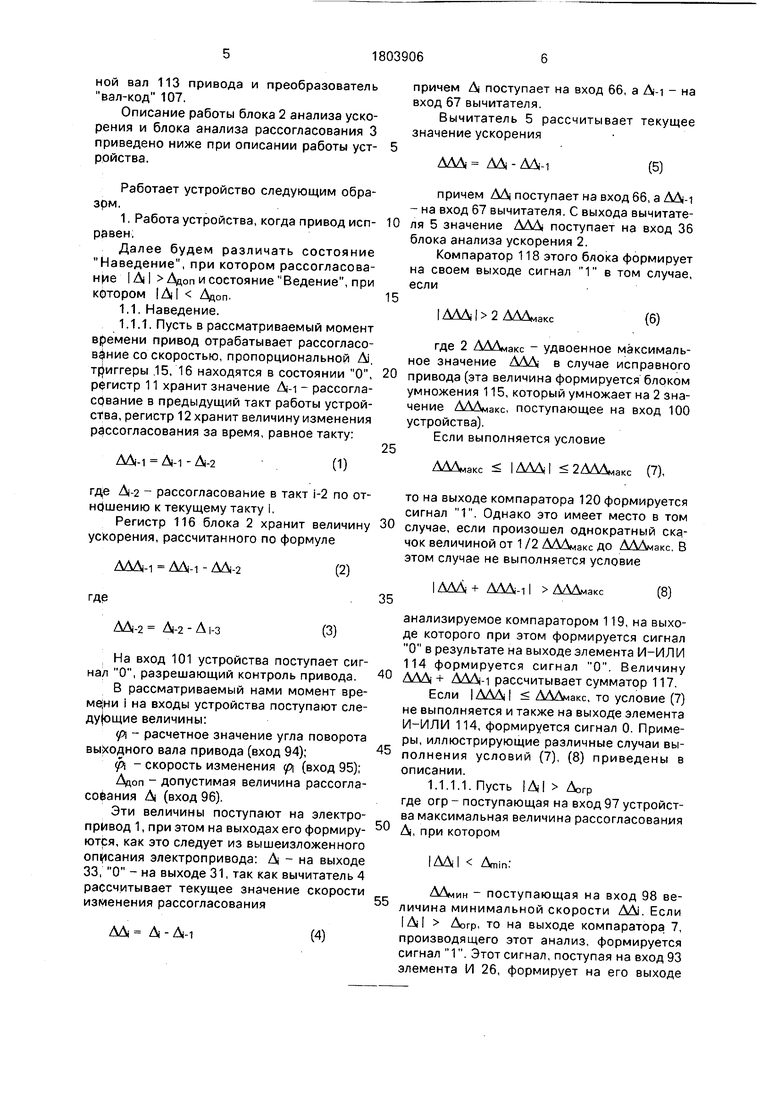

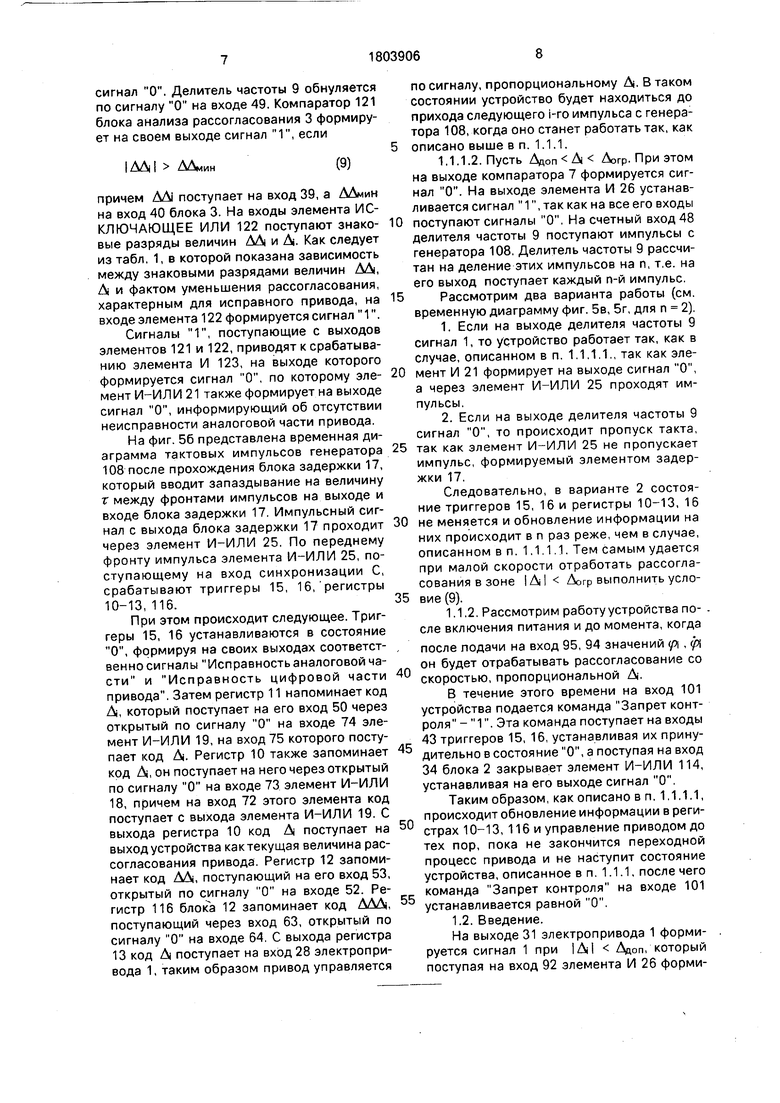

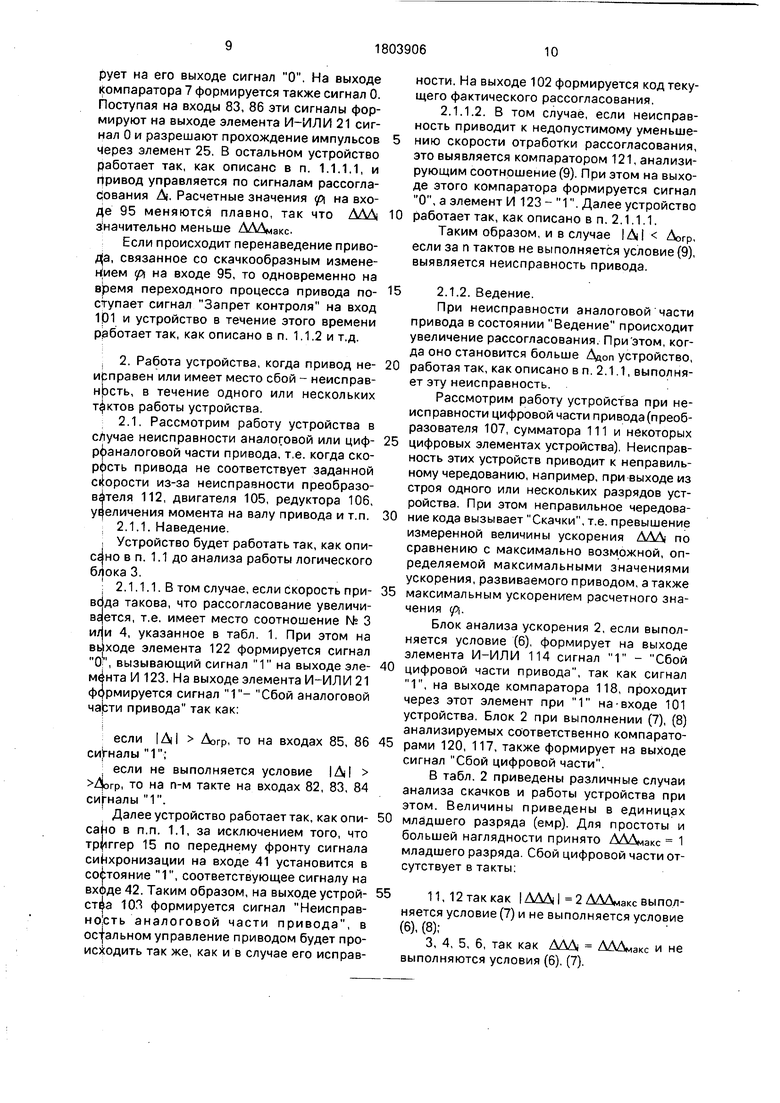

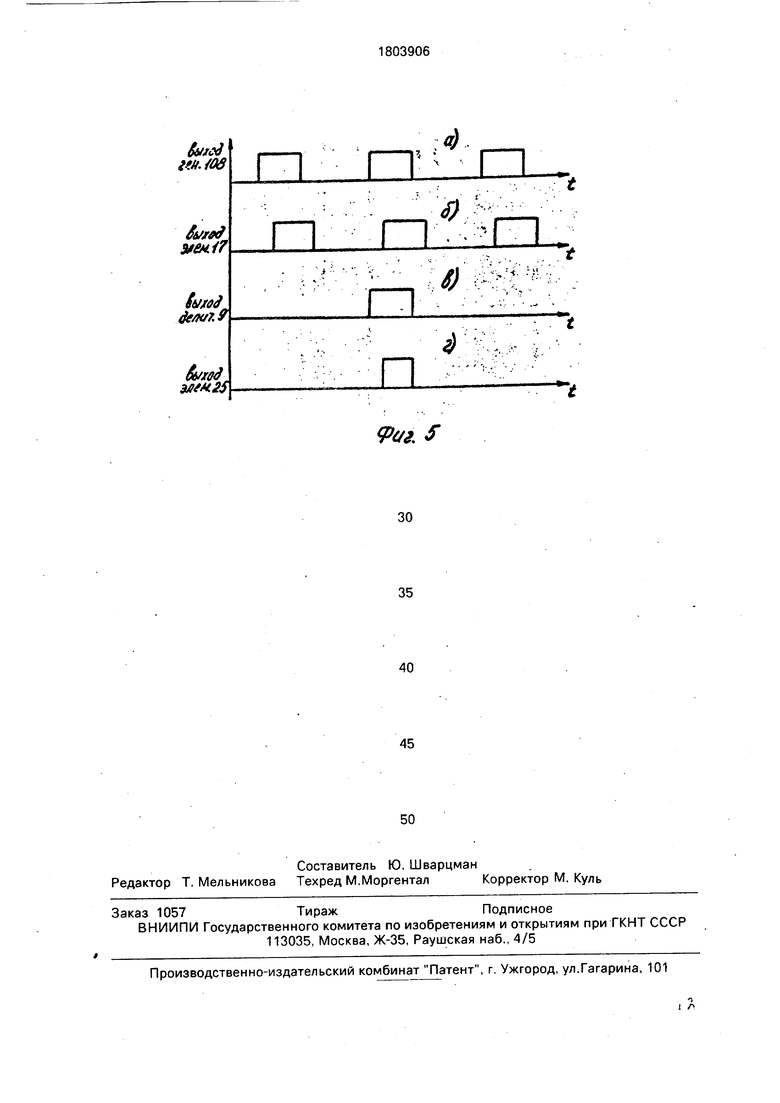

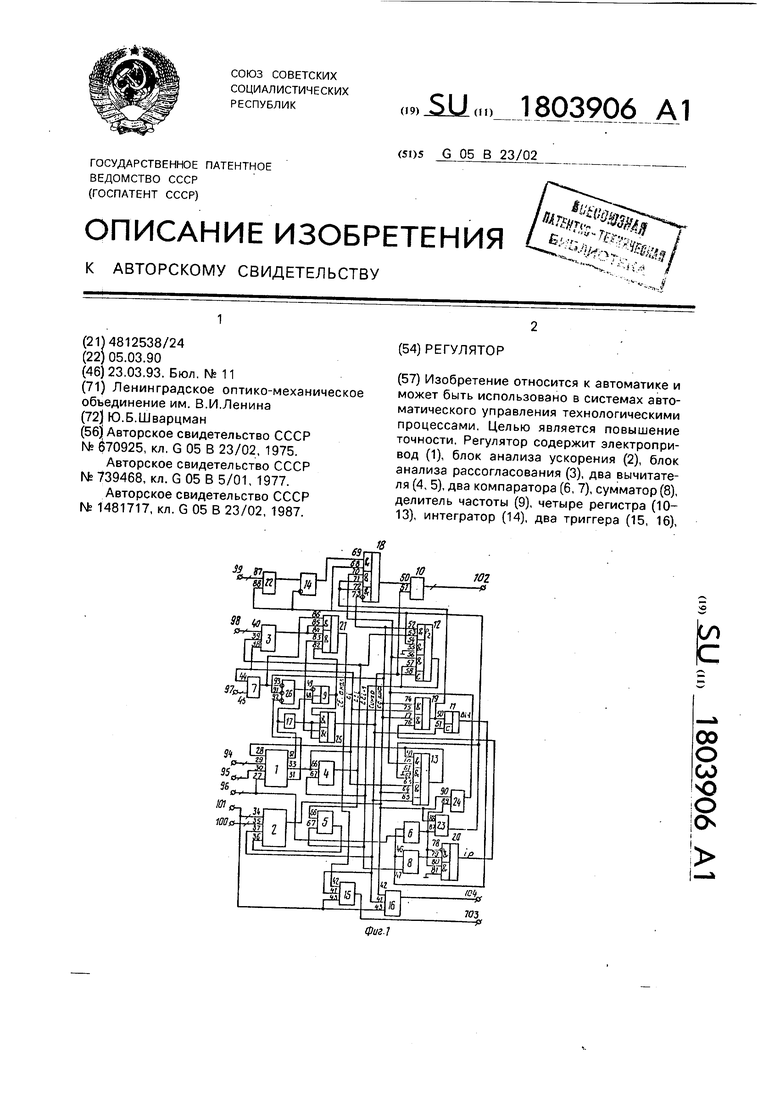

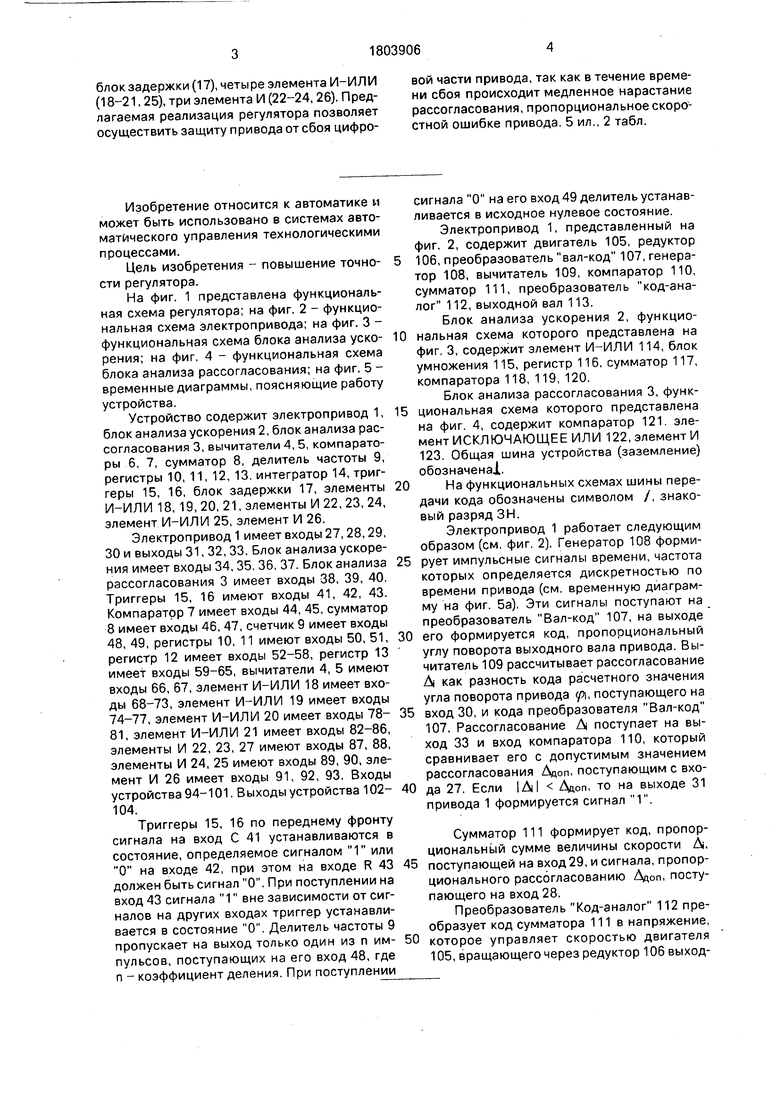

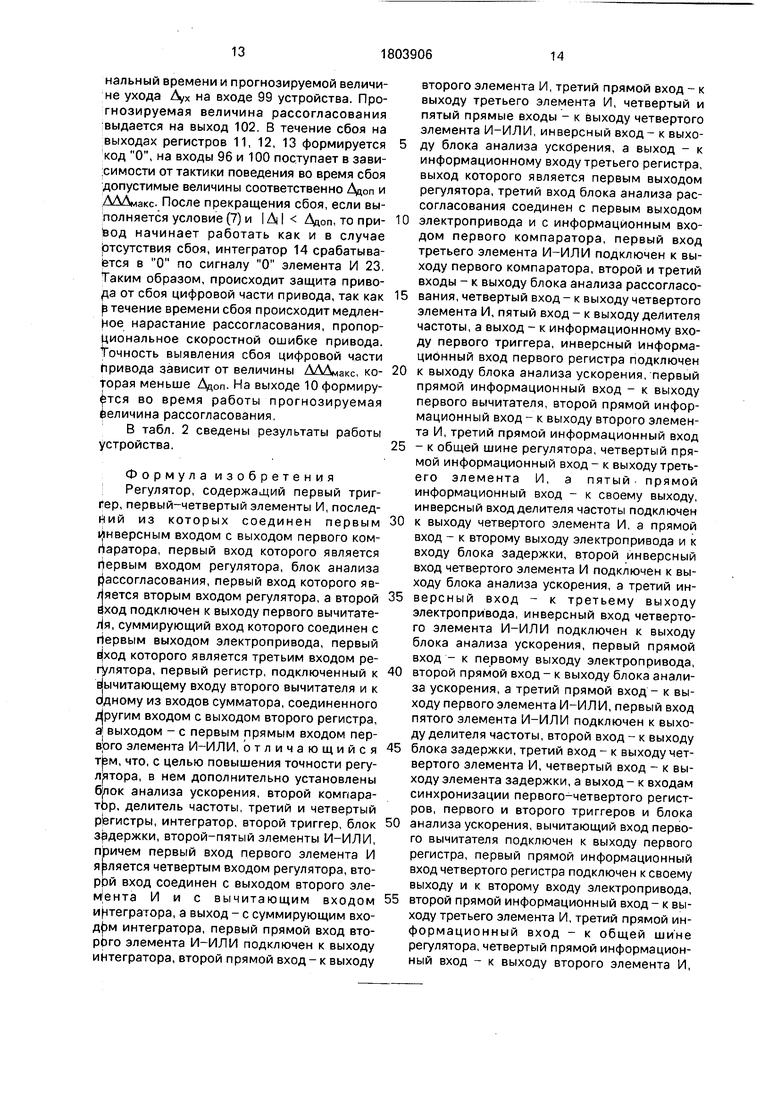

На фиг. 1 представлена функциональная схема регулятора; на фиг. 2 - функциональная схема электропривода; на фиг. 3 - функциональная схема блока анализа ускорения; на фиг. 4 - функциональная схема блока анализа рассогласования; на фиг. 5 - временные диаграммы, поясняющие работу устройства,

Устройство содержит электропривод 1, блок анализа ускорения 2,блок анализа рассогласования 3, вычитатели 4, 5, компараторы 6, 7, сумматор 8, делитель частоты 9, регистры 10, 11, 12, 13, интегратор 14, триггеры 15, 16, блок задержки 17, элементы И-ИЛИ 18, 19, 20, 21, элементы И 22, 23, 24, элемент И-ИЛИ 25, элемент И 26.

Электропривод 1 имеет входы 27,28,29, 30 и выходы 31, 32, 33. Блок анализа ускорения имеет входы 34, 35, 36, 37. Блок анализа рассогласования 3 имеет входы 38, 39, 40. Триггеры 15, 16 имеют входы 41, 42, 43. Компаратор 7 имеет входы 44, 45, сумматор 8 имеет входы 46,47, счетчик 9 имеет входы 48, 49, регистры 10, 11 имеют входы 50, 51, регистр 12 имеет входы 52-58, регистр 13 имеет входы 59-65, вычитатели 4, 5 имеют входы 66, 67, элемент И-ИЛИ 18 имеет входы 68-73, элемент И-ИЛИ 19 имеет входы 74-77, элемент И-ИЛИ 20 имеет входы 78- 81, элемент И-ИЛИ 21 имеет входы 82-86, элементы И 22, 23, 27 имеют входы 87, 88, элементы И 24, 25 имеют входы 89, 90, элемент И 26 имеет входы 91, 92, 93. Входы устройства 94-101. Выходы устройства 102- 104.

Триггеры 15, 16 по переднему фронту сигнала на вход С 41 устанавливаются в состояние, определяемое сигналом 1 или О на входе 42, при этом на входе R 43 должен быть сигнал О. При поступлении на вход 43 сигнала 1 вне зависимости от сигналов на других входах триггер устанавливается в состояние О. Делитель частоты 9 пропускает на выход только один из п импульсов, поступающих на его вход 48, где П - коэффициент деления. При поступлении

сигнала О на его вход 49 делитель устанавливается в исходное нулевое состояние.

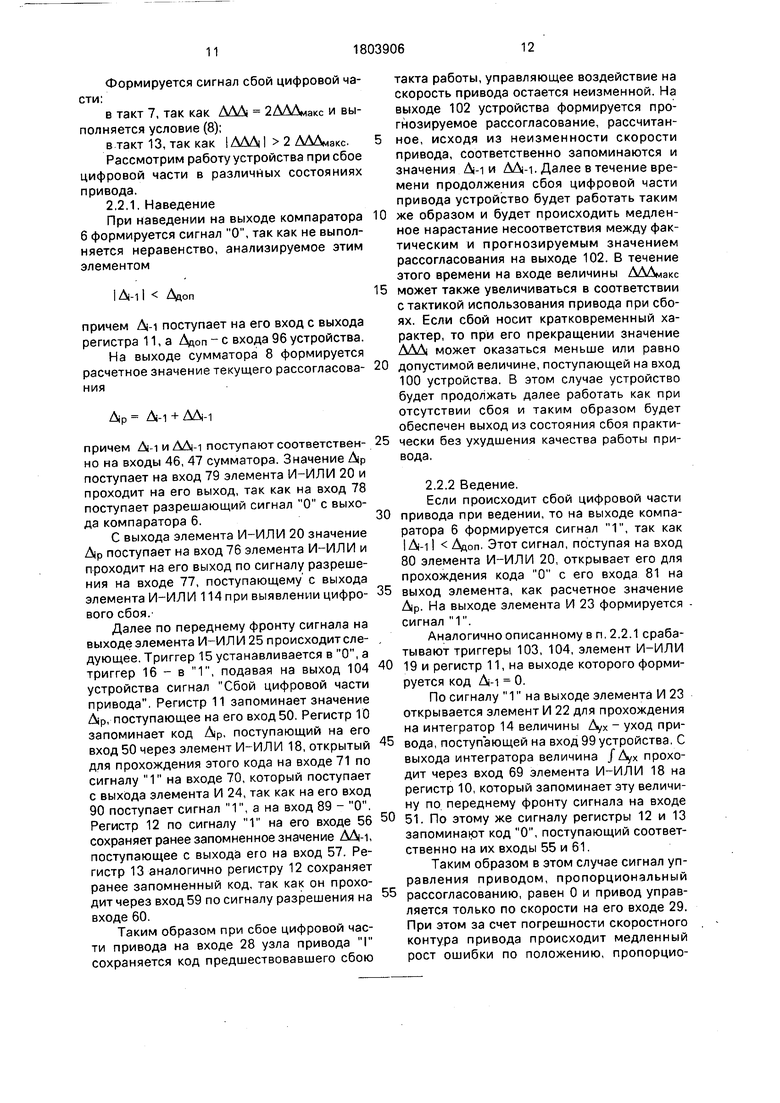

Электропривод 1, представленный на фиг. 2, содержит двигатель 105, редуктор

106, преобразователь вал-код 107, генератор 108, вычитатель 109, компаратор 110, сумматор 111, преобразователь код-аналог 112, выходной вал 113.

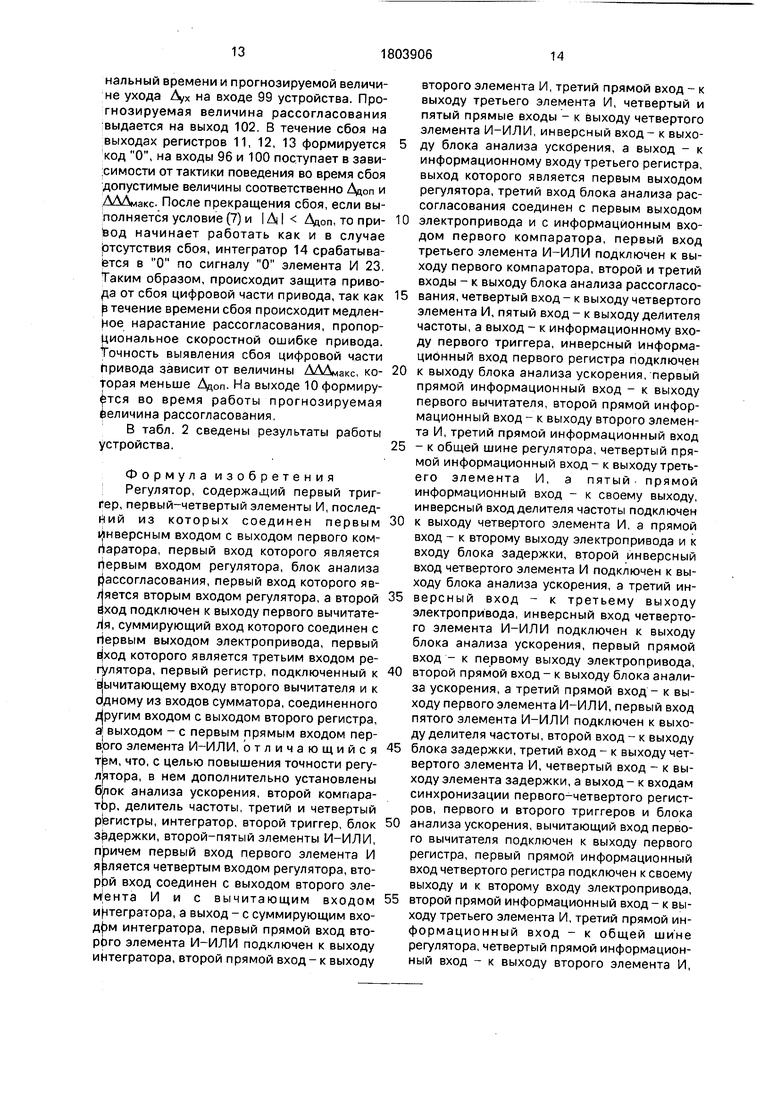

Блок анализа ускорения 2, функциональная схема которого представлена на фиг. 3, содержит элемент И-ИЛИ 114, блок умножения 115, регистр 116, сумматор 117, компаратора 118, 119, 120.

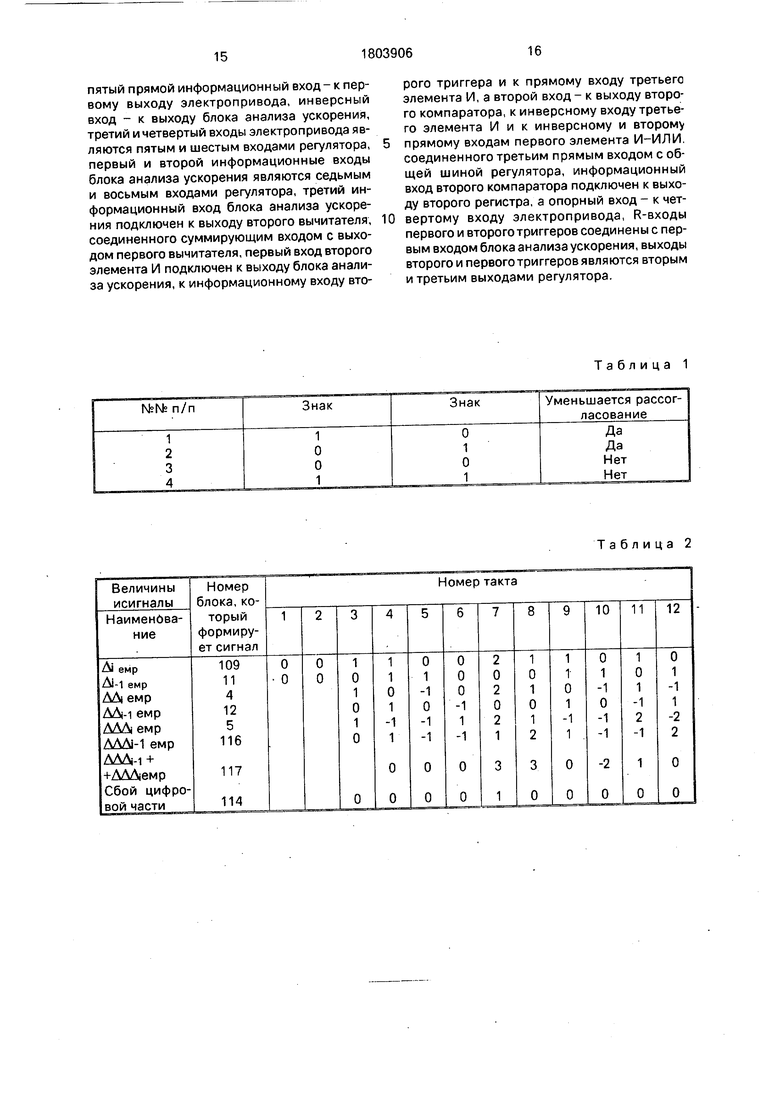

Блок анализа рассогласования 3, функциональная схема которого представлена на фиг. 4, содержит компаратор 121. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 122,элемент И 123. Общая шина устройства (заземление) обозначена.

На функциональных схемах шины передачи кода обозначены символом /, знаковый разряд ЗН.

Электропривод 1 работает следующим образом (см. фиг. 2). Генератор 108 формирует импульсные сигналы времени, частота которых определяется дискретностью по времени привода (см. временную диаграмму на фиг. 5а). Эти сигналы поступают на преобразователь Вал-код 107, на выходе

его формируется код, пропорциональный углу поворота выходного вала привода. Вычитатель 109 рассчитывает рассогласование Д как разность кода расчетного значения угла поворота привода f, поступающего на

вход 30, и кода преобразователя Вал-код 107. Рассогласование Д поступает на выход 33 и вход компаратора 110, который сравнивает его с допустимым значением рассогласования Ддоп, поступающим с входа 27. Если |Д Дцоп, то на выходе 31 привода 1 формируется сигнал 1.

Сумматор 111 формирует код, пропорциональный сумме величины скорости Д, поступающей на вход 29, и сигнала, пропорционального рассогласованию Адоп, поступающего на вход 28.

Преобразователь Код-аналог 112 преобразует код сумматора 111 в напряжение, которое управляет скоростью двигателя 105, вращающего через редуктор 106 выходной вал 113 привода и преобразователь вал-код 107.

Описание работы блока 2 анализа ускорения и блока анализа рассогласования 3 приведено ниже при описании работы устройства.

Работает устройство следующим образом,

Далее будем различать состояние Наведение, при котором рассогласование 1Д1 Дцоп и состояние Ведение, при

КОТОрОМ | Д | Ддоп.

ДД-1 Д-1 - Д-2

(1)

где Д-2 - рассогласование в такт i-2 по отношению к текущему такту i,

Регистр 116 блока 2 хранит величину ускорения, рассчитанного по формуле

ЛАД-1 АД-1 - АД-2

(2)

где

АД-2 Д-2 - А |-з

(3)

На вход 101 устройства поступает сигнал О, разрешающий контроль привода.

В рассматриваемый нами момент вре- ме|ни i на входы устройства поступают сле- ду$ощие величины:

р - расчетное значение угла поворота выходного вала привода (вход 94);

ф - скорость изменения де (вход 95);

Ддоп допустимая величина рассогласования Д (вход 96).

Эти величины поступают на электропривод 1, при этом на выходах его формируются, как это следует из вышеизложенного описания электропривода: Д - на выходе 33, О - на выходе 31, так как вычитатель 4 рассчитывает текущее значение скорости изменения рассогласования

АД Д - Д-1

(4)

причем Д поступает на вход 66, а Д-1 - на вход 67 вычитателя.

Вычитатель 5 рассчитывает текущее значение ускорения

ААД АД-АД-1

(5)

причем АД поступает на вход 66, а АД-1 - на вход 67 вычитателя. С выхода вычитателя 5 значение ЛАД поступает на вход 36 блока анализа ускорения 2.

Компаратор 118 этого блока формирует на своем выходе сигнал 1 в том случае, если

|ААД| 2 АААма

(6)

где 2 АДАмакс - удвоенное максимальное значение ЛЛД в случае исправного привода (эта величина формируется блоком умножения 115, который умножает на 2 значение ДАЛмакс, поступающее на вход 100 устройства).

Если выполняется условие

АДАмакс 1ДДД1 2ДДЛма

(7),

то на выходе компаратора 120 формируется сигнал 1. Однако это имеет место в том случае, если произошел однократный скачок ВеЛИЧИНОЙ ОТ 1 /2 ДДДмакс ДО ДААмакс. В

этом случае не выполняется условие

35

1ААД+ ААД-11 ДДДмакс

(8)

0

5

0

5

анализируемое компаратором 119, на выходе которого при этом формируется сигнал О в результате на выходе элемента И-ИЛ И 114 формируется сигнал О. Величину ДАД + ДДД-1 рассчитывает сумматор 117.

Если |ААД| ДДДмакс, то условие (7) не выполняется и также на выходе элемента И-ИЛИ 114, формируется сигнал 0. Примеры, иллюстрирующие различные случаи выполнения условий (7), (8) приведены в описании.

где огр - поступающая на вход 97 устройства максимальная величина рассогласования Д, при котором

IAAI Anin;

ААмин - поступающая на вход 98 величина минимальной скорости АД. Если |Д| Догр, то на выходе компаратора 7, производящего этот анализ, формируется сигнал 1. Этот сигнал, поступая на вход 93 элемента И 26, формирует на его выходе

сигнал О. Делитель частоты 9 обнуляется по сигналу О на входе 49. Компаратор 121 блока анализа рассогласования 3 формирует на своем выходе сигнал 1, если

IMI ДА™

причем ДД| поступает на вход 39, а ДАмин на вход 40 блока 3. На входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 122 поступают знаковые разряды величин ДД и Д. Как следует из табл, 1, в которой показана зависимость между знаковыми разрядами величин ДД, Д и фактом уменьшения рассогласования, характерным для исправного привода, на входе элемента 122 формируется сигнал 1.

Сигналы 1, поступающие с выходов элементов 121 и 122, приводят к срабатыванию элемента И 123, на выходе которого формируется сигнал О, по которому элемент И-ИЛИ 21 также формирует на выходе сигнал О, информирующий об отсутствии неисправности аналоговой части привода.

На фиг. 56 представлена временная диаграмма тактовых импульсов генератора 108 после прохождения блока задержки 17, который вводит запаздывание на величину т между фронтами импульсов на выходе и входе блока задержки 17. Импульсный сигнал с выхода блока задержки 17 проходит через элемент И-ИЛИ 25. По переднему фронту импульса элемента И-ИЛИ 25, поступающему на вход синхронизации С, срабатывают триггеры 15, 16, регистры 10-13, 116.

При этом происходит следующее. Триггеры 15, 16 устанавливаются в состояние О, формируя на своих выходах соответственно сигналы Исправность аналоговой части и Исправность цифровой части привода. Затем регистр 11 напоминает код Д, который поступает на его вход 50 через открытый по сигналу О на входе 74 элемент И-ИЛИ 19, на вход 75 которого поступает код Д. Регистр 10 также запоминает код Д, он поступает на него через открытый по сигналу О на входе 73 элемент И-ИЛИ 18, причем на вход 72 этого элемента код поступает с выхода элемента И-ИЛИ 19. С выхода регистра 10 код Д поступает на выход устройства как текущая величина рассогласования привода. Регистр 12 запоминает код Л/V поступающий на его вход 53, открытый по сигналу О на входе 52. Регистр 116 блока 12 запоминает код ЛЛД. поступающий через вход 63, открытый по сигналу О на входе 64. С выхода регистра 13 код Д поступает на вход 28 электропривода 1, таким образом привод управляется

10

15

20

25

30

35

40

45

50

55

по сигналу, пропорциональному Д, В таком состоянии устройство будет находиться до прихода следующего i-ro импульса с генератора 108, когда оно станет работать так, как описано выше в п. 1.1.1.

1,1.1.2. Пусть Ддоп Д Догр. При этом на выходе компаратора 7 формируется сигнал О. На выходе элемента И 26 устанавливается сигнал 1,так как на все его входы поступают сигналы О. На счетный вход 48 делителя частоты 9 поступают импульсы с генератора 108. Делитель частоты 9 рассчитан на деление этих импульсов на п, т.е. на его выход поступает каждый n-й импульс.

Рассмотрим два варианта работы (см. временную диаграмму фиг. 5в, 5г, для п 2).

Следовательно, в варианте 2 состояние триггеров 15, 16 и регистры 10-13, 16 не меняется и обновление информации на них происходит в п раз реже, чем в случае, описанном в п. 1.1.1.1. Тем самым удается при малой скорости отработать рассогласования в зоне 1Д1 Догр выполнить условие (9).

после подачи на вход 95, 94 значений (р , ф{ он будет отрабатывать рассогласование со скоростью, пропорциональной Д.

В течение этого времени на вход 101 устройства подается команда Запрет контроля - 1. Эта команда поступает на входы 43 триггеров 15, 16, устанавливая их принудительно в состояние О, а поступая на вход 34 блока 2 закрывает элемент И-ИЛИ 114, устанавливая на его выходе сигнал О.

Таким образом, как описано в п. 1.1.1.1, происходит обновление информации в регистрах 10-13, 116 и управление приводом до тех пор, пока не закончится переходной процесс привода и не наступит состояние устройства, описанное в п. 1.1.1, после чего команда Запрет контроля на входе 101 устанавливается равной О.

На выходе 31 электропривода 1 формируется сигнал 1 при |Д Ддоп, который поступая на вход 92 элемента И 26 формирует на его выходе сигнал О. На выходе Компаратора 7 формируется также сигнал 0. Поступая на входы 83, 86 эти сигналы формируют на выходе элемента И-ИЛИ 21 сигнал 0 и разрешают прохождение импульсов через элемент 25. В остальном устройство работает так, как описано в п. 1.1.1.1, и г|ривод управляется по сигналам рассогласования Д. Расчетные значения до на вхо- Де 95 меняются плавно, так что ЛЛ/ Значительно меньше ДДДмакс.

Если происходит перенаведение привода, связанное со скачкообразным измене- до на входе 95, то одновременно на время переходного процесса привода по ступает сигнал Запрет контроля на вход 101 и устройство в течение этого времени работает так, как описано в п. 1.1.2 и т.д.

-

, 2. Работа устройства, когда привод не- ирправен или имеет место сбой - неисправ- , в течение одного или нескольких тфктов работы устройства.

; 2.1. Рассмотрим работу устройства в случае неисправности аналоговой или циф- р|)аналоговой части привода, т.е. когда ско- рфсть привода не соответствует заданной скорости из-за неисправности преобразо- 112, двигателя 105, редуктора 106, увеличения момента на валу привода и т.п. 2.1.1. Наведение.

i Устройство будет работать так, как опи- са|но в п. 1.1 до анализа работы логического б/|ока 3.

| 2.1.1.1. В том случае, если скорость при- всда такова, что рассогласование увеличивается, т.е. имеет место соотношение № 3 и/и 4, указанное в табл. 1. При этом на выходе элемента 122 формируется сигнал 0|, вызывающий сигнал 1 на выходе эле- м4нта И 123. На выходе элемента И-ИЛИ 21 формируется сигнал Сбой аналоговой ча|сти привода так как:

если |Д| Догр, то на входах 85, 86 сигналы

; если не выполняется условие |Д 4огр, то на n-м такте на входах 82, 83, 84 сигналы 1.

Далее устройство работает так, как опи- сайо в п.п. 1.1, за исключением того, что триггер 15 по переднему фронту сигнала синхронизации на входе 41 установится в состояние 1, соответствующее сигналу на входе 42. Таким образом, на выходе устрой- ст(Ц 103 формируется сигнал Неисправ- но|сть аналоговой части привода, в остальном управление приводом будет происходить так же, как ив случае его исправности. На выходе 102 формируется код текущего фактического рассогласования.

Таким образом, и в случае |Д| Догр, если за п тактов не выполняется условие (9), выявляется неисправность привода.

15 2.1.2. Ведение.

При неисправности аналоговой части привода в состоянии Ведение происходит увеличение рассогласования. При этом, когда оно становится больше Ддоп устройство,

20 работая так, как описано в п. 2.1.1, выполняет эту неисправность.

Рассмотрим работу устройства при неисправности цифровой части при вода (преобразователя 107, сумматора 111 и некоторых

25 цифровых элементах устройства). Неисправность этих устройств приводит к неправильному чередованию, например, при выходе из строя одного или нескольких разрядов устройства. При этом неправильное чередова30 ние кода вызывает Скачки, т.е. превышение измеренной величины ускорения ЛЛД по сравнению с максимально возможной, определяемой максимальными значениями ускорения, развиваемого приводом, а также

35 максимальным ускорением расчетного значения до.

Блок анализа ускорения 2, если выполняется условие (6), формирует на выходе элемента И-ИЛИ 114 сигнал 1 - Сбой

40 цифровой части привода, так как сигнал 1, на выходе компаратора 118, проходит через этот элемент при 1 на-входе 101 устройства. Блок 2 при выполнении (7), (8) анализируемых соответственно компарато45 рами 120, 117, также формирует на выходе сигнал Сбой цифровой части.

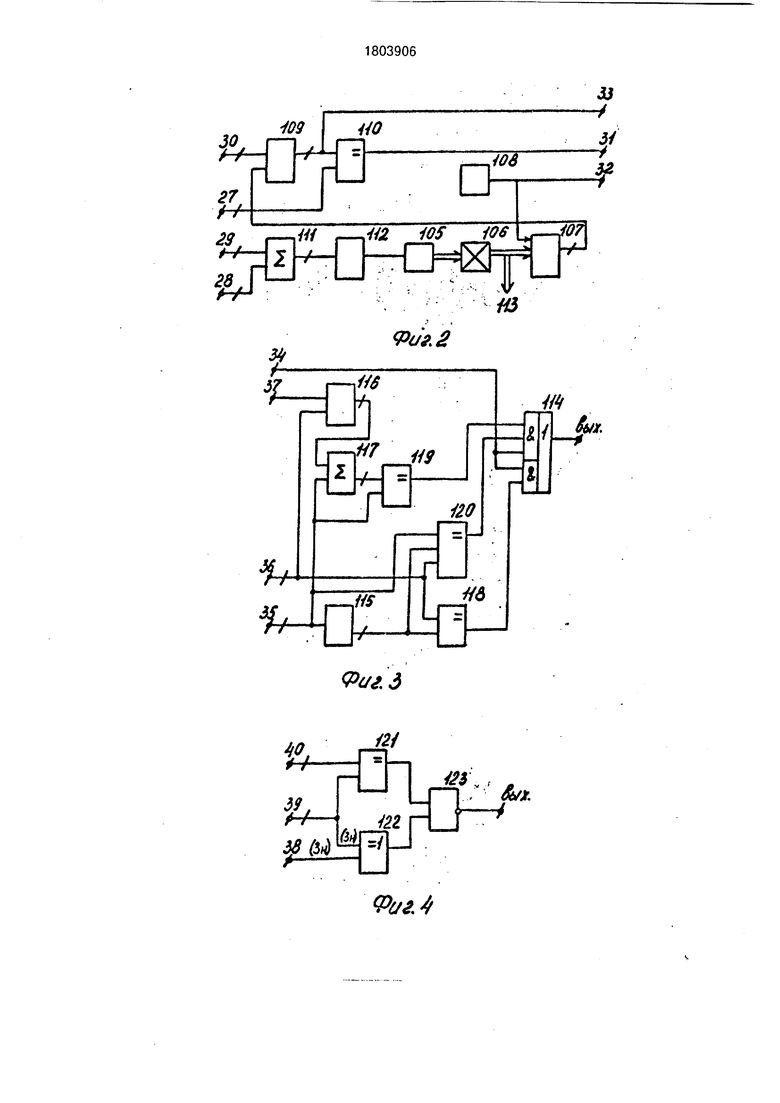

В табл. 2 приведены различные случаи анализа скачков и работы устройства при этом. Величины приведены в единицах

50 младшего разряда (емр). Для простоты и большей наглядности принято ДДДмакс 1 младшего разряда. Сбой цифровой части отсутствует в такты:

55 11, 12 так как |ДДД| 2 ДДДмакс выполняется условие (7) и не выполняется условие (6), (8);

3, 4, 5, 6, так как ЛАД ДДДмакс и не выполняются условия (6), (7).

Формируется сигнал сбой цифровой части:

в такт 7, так как ДЛД 2АДДмакс и выполняется условие (8);

в такт 13, так как I МД| I 2 ДДДмакс.

Рассмотрим работу устройства при сбое цифровой части в различных состояниях привода.

При наведении на выходе компаратора 6 формируется сигнал О, так как не выполняется неравенство, анализируемое этим элементом

I Д-11 Ддоп

причем Л-1 поступает на его вход с выхода регистра 11, а Ддоп - с входа 96 устройства. На выходе сумматора 8 формируется расчетное значение текущего рассогласова- ния

Др Дм + ДД-1

причем Д-1 и ДД-i поступают соответствен- но на входы 46, 47 сумматора. Значение Др поступает на вход 79 элемента И-ИЛИ 20 и проходит на его выход, так как на вход 78 поступает разрешающий сигнал О с выхода компаратора 6.

С выхода элемента И-ИЛИ 20 значение Др поступает на вход 76 элемента И-ИЛИ и проходит на его выход по сигналу разрешения на входе 77, поступающему с выхода элемента И-ИЛИ 114 при выявлении цифро- вого сбоя/

Далее по переднему фронту сигнала на выходе элемента И-ИЛИ 25 происходит еле- дующее. Триггер 15 устанавливается в О, а триггер 16 - в 1, подавая на выход 104 устройства сигнал Сбой цифровой части привода. Регистр 11 запоминает значение Др, поступающее на его вход 50. Регистр 10 запоминает код Др, поступающий на его вход 50 через элемент И-ИЛИ 18, открытый для прохождения этого кода на входе 71 по сигналу 1 на входе 70, который поступает с выхода элемента И 24, так как на его вход 90 поступает сигнал 1, а на вход 89 - О. Регистр 12 по сигналу 1 на его входе 56 сохраняет ранее запомненное значение ДД-1, поступающее с выхода его на вход 57. Регистр 13 аналогично регистру 12 сохраняет ранее запомненный код, так как он проходит через вход 59 по сигналу разрешения на входе 60.

Таким образом при сбое цифровой части привода на входе 28 узла привода I сохраняется код предшествовавшего сбою

0

5

0

5 0

5

0 5 0 5

такта работы, управляющее воздействие на скорость привода остается неизменной. На выходе 102 устройства формируется прогнозируемое рассогласование, рассчитанное, исходя из неизменности скорости привода, соответственно запоминаются и значения Д-i и ДД-1. Далее в течение времени продолжения сбоя цифровой части привода устройство будет работать таким же образом и будет происходить медленное нарастание несоответствия между фактическим и прогнозируемым значением рассогласования на выходе 102. В течение этого времени на входе величины ДДДмакс может также увеличиваться в соответствии с тактикой использования привода при сбоях. Если сбой носит кратковременный характер, то при его прекращении значение ДАЛ может оказаться меньше или равно допустимой величине, поступающей на вход 100 устройства. В этом случае устройство будет продолжать далее работать как при отсутствии сбоя и таким образом будет обеспечен выход из состояния сбоя практически без ухудшения качества работы привода.

Если происходит сбой цифровой части привода при ведении, то на выходе компаратора 6 формируется сигнал 1, так как I Д-11 Ддоп. Этот сигнал, поступая на вход 80 элемента И-ИЛИ 20, открывает его для прохождения кода О с его входа 81 на выход элемента, как расчетное значение Др. На выходе элемента И 23 формируется сигнал 1.

Аналогично описанному в п. 2.2.1 срабатывают триггеры 103, 104, элемент И-ИЛИ 19 и регистр 11, на выходе которого формируется код Д-1 0.

По сигналу 1 на выходе элемента И 23 открывается элемент И 22 для прохождения на интегратор 14 величины ДуХ - уход привода, поступающей на вход 99 устройства. С выхода интегратора величина /Дух проходит через вход 69 элемента И-ИЛИ 18 на регистр 10, который запоминает эту величину по переднему фронту сигнала на входе 51. По этому же сигналу регистры 12 и 13 запоминают код О, поступающий соответственно на их входы 55 и 61.

Таким образом в этом случае сигнал управления приводом, пропорциональный рассогласованию, равен 0 и привод управляется только по скорости на его входе 29. При этом за счет погрешности скоростного контура привода происходит медленный рост ошибки по положению, пропорциональный времени и прогнозируемой величине ухода 4уХ на входе 99 устройства. Прогнозируемая величина рассогласования выдается на выход 102. В течение сбоя на выходах регистров 11, 12, 13 формируется код О, на входы 96 и 100 поступает в зависимости от тактики поведения во время сбоя допустимые величины соответственно Ддоп и ДДДмакс. После прекращения сбоя, если выполняется условие (7) и IДI Дцоп, то при- йод начинает работать как и в случае (отсутствия сбоя, интегратор 14 срабатывается в О по сигналу О элемента И 23. Таким образом, происходит защита привода от сбоя цифровой части привода, так как р течение времени сбоя происходит медленное нарастание рассогласования, пропорциональное скоростной ошибке привода. Точность выявления сбоя цифровой части привода зависит от величины ДДДмакс, ко- торая меньше Дцоп. На выходе Юформиру- Јтся во время работы прогнозируемая величина рассогласования.

В табл. 2 сведены результаты работы устройства.

Формула изобретения ; Регулятор, содержащий первый триггер, первый-четвертый элементы И, послед- иий из которых соединен первым инверсным входом с выходом первого компаратора, первый вход которого является г)ервым входом регулятора, блок анализа рассогласования, первый вход которого яв- л|яется вторым входом регулятора, а второй йход подключен к выходу первого вычитате- л|я, суммирующий вход которого соединен с Первым выходом электропривода, первый в;ход которого является третьим входом регулятора, первый регистр, подключенный к вычитающему входу второго вычитателя и к одному из входов сумматора, соединенного Другим входом с выходом второго регистра, а| выходом - с первым прямым входом первого элемента И-ИЛИ, отличающийся тем, что, с целью повышения точности регу- л|ятора, в нем дополнительно установлены б|лок анализа ускорения, второй компаратор, делитель частоты, третий и четвертый регистры, интегратор, второй триггер, блок задержки, второй-пятый элементы И-ИЛИ, причем первый вход первого элемента И я зляется четвертым входом регулятора, вто- рэй вход соединен с выходом второго эле- И и с вычитающим входом интегратора, а выход - с суммирующим вхо- дрм интегратора, первый прямой вход вто- Р0го элемента И-ИЛИ подключен к выходу интегратора, второй прямой вход- к выходу

второго элемента И, третий прямой вход - к выходу третьего элемента И, четвертый и пятый прямые входы - к выходу четвертого элемента И-ИЛИ, инверсный вход- к выходу блока анализа ускбрения, а выход - к информационному входу третьего регистра, выход которого является первым выходом регулятора, третий вход блока анализа рассогласования соединен с первым выходом электропривода и с информационным входом первого компаратора, первый вход третьего элемента И-ИЛИ подключен к выходу первого компаратора, второй и третий входы - к выходу блока анализа рассогласования, четвертый вход - к выходу четвертого элемента И, пятый вход - к выходу делителя частоты, а выход - к информационному входу первого триггера, инверсный Информационный вход первого регистра подключен к выходу блока анализа ускорения, первый прямой информационный вход - к выходу первого вычитателя, второй прямой информационный вход- к выходу второго элемента И, третий прямой информационный вход - к общей шине регулятора, четвертый прямой информационный вход - к выходу третьего элемента И, а пятый, прямой информационный вход - к своему выходу, инверсный вход делителя частоты подключен к выходу четвертого элемента И, а прямой вход - к второму выходу электропривода и к входу блока задержки, второй инверсный вход четвертого элемента И подключен к выходу блока анализа ускорения, а третий инверсный вход - к третьему выходу электропривода, инверсный вход четвертого элемента И-ИЛИ подключен к выходу блока анализа ускорения, первый прямой вход - к первому выходу электропривода, второй прямой вход - к выходу блока анализа ускорения, а третий прямой вход - к выходу первого элемента И-ИЛИ, первый вход пятого элемента И-ИЛИ подключен к выходу делителя частоты, второй вход - к выходу блока задержки, третий вход - к выходу четвертого элемента И, четвертый вход - к выходу элемента задержки, а выход - к входам синхронизации первого-четвертого регистров, первого и второго триггеров и блока анализа ускорения, вычитающий вход первого вычитателя подключен к выходу первого регистра, первый прямой информационный вход четвертого регистра подключен к своему выходу и к второму входу электропривода, второй прямой информационный вход - к выходу третьего элемента И, третий прямой информационный вход - к общей шине регулятора, четвертый прямой информационный вход - к выходу второго элемента И,

пятый прямой информационный вход- к первому выходу электропривода, инверсный вход - к выходу блока анализа ускорения, третий и четвертый входы электропривода являются пятым и шестым входами регулятора, первый и второй информационные входы блока анализа ускорения являются седьмым и восьмым входами регулятора, третий информационный вход блока анализа ускорения подключен к выходу второго вычитателя, соединенного суммирующим входом с выходом первого вычитателя, первый вход второго элемента И подключен к выходу блока анализа ускорения, к информационному входу вто0

рого триггера и к прямому входу третьего элемента И, а второй вход - к выходу второго компаратора, к инверсному входу третьего элемента И и к инверсному и второму прямому входам первого элемента И-ИЛИ. соединенного третьим прямым входом с общей шиной регулятора, информационный вход второго компаратора подключен к выходу второго регистра, а опорный вход - к четвертому входу электропривода, R-входы первого и второго триггеров соединены с первым входом блока анализа ускорения, выходы второго и первоготриггеров являются вторым и третьим выходами регулятора.

Таблица 1

Таблица 2

Фа 3

#W.Ј

Фиг. 4

Фа f

| Устройство для функционального контроля цифрового привода | 1975 |

|

SU670925A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для управления электроприводом | 1977 |

|

SU739468A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для функционального контроля электропривода | 1987 |

|

SU1481717A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-03-23—Публикация

1990-03-05—Подача