Изобретение относится к автоматике и вычислительной технике и предназначено для обработки булевых и аналоговых сигналов в устройствах программно-логического управления технологическими установками и агрегатами.

Известно устройство, содержащее операционный триггер, триггер результата, элемент И, элемент ИЛИ, первый и второй узлы инвертирования 1 .

Недостатком данного устройства являются ограниченные функциональные возможности.

Наиболее близким к предлагаемому является устройство для вычисления булевых функций, содержащее операционный триггер, триггер результата, первый элемент И, элемент ИЛИ, триггер конъюнктивной формы, первый и второй узлы инвертирования, причем выход .: первого узла инвертирования соединен с первым входом операционного триггера, выход которого соединен с первыми входами триггера результата, первого элемента И и элемента ИЛИ, выход триггера результата соединен с вторыми входами первого элемента И и элемента ИЛИ, третьи вхо.йы элемента И и элемента ИЛИ соединены с вторыми

входами операционного триггера и триггера результата и с выходом триггера конъюнктивной . формы, входы первого эл емента И и элемента ИЛИ соединены с информационным входом второго узла инвертирования, управляющие входы операционного триггера, триггера результата, первого и второго узлов инвертирования и вход

10 триггера конъюнктивной формы соединены с управляющим входом устройства, а выход устройства соединен с выходом второго узла инвертирования (|2 .

Недостатками известного устройства

15 являются ограниченные функциональные возможности, связанные с тем, что в качестве входной информации используется только информация в виде булевых переменных. В устройствах же програм20мно-логического управления наряду с булевыми сигналами часто необходимо обрабатывать и аналоговую информацию, поступаквдую От всевозможных частотных датчиков, причем в качестве обрабатываемой информации используется не само значение частоты, а ее область нахождения, выше или ниже заданной граничной величины.

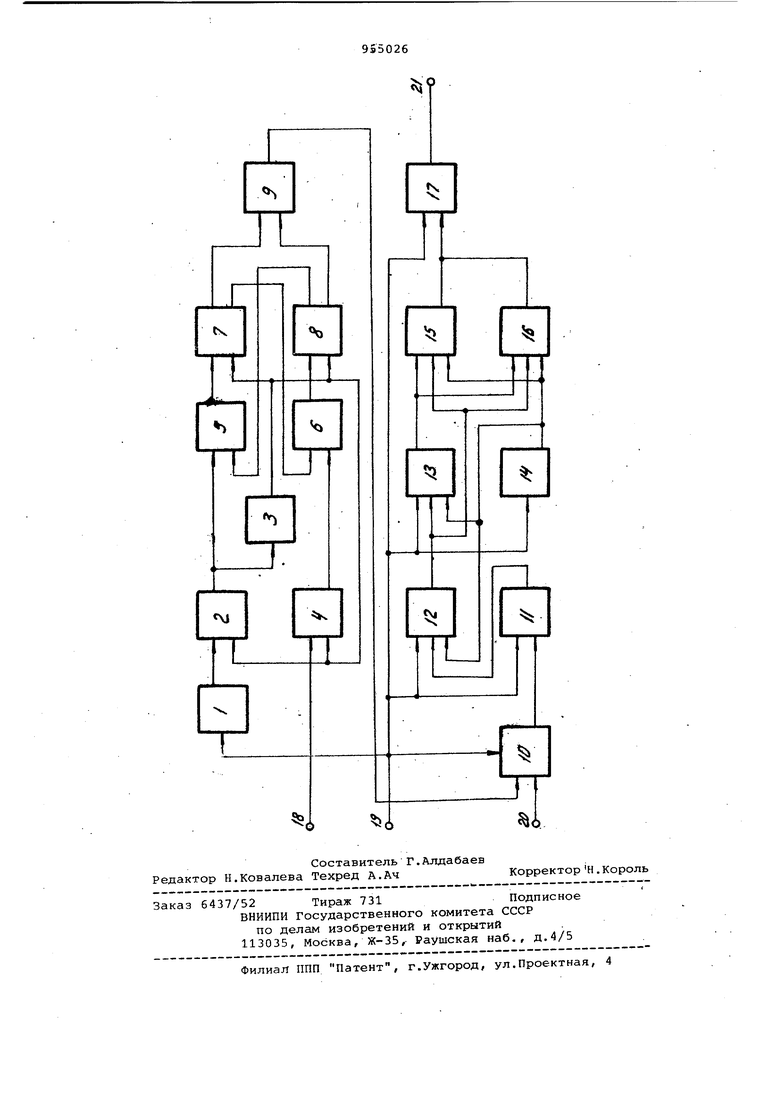

Цель изобретения - расширения функциональных возможностей устройства за счет возможности обработки аналоговых сигналов. Поставленная цель достигается тем что в устройство для вычисления булевых функций, содержащее операционный триггер, триггер результата, первый элемент И, элемент ИЛИ, триггер конъюнктивной формы, первый и второй узлы инвертирования, причем выход первого узла инвертирования соединен с первым входом операционного триггера, выход которого соединен с первыми входами триггера результата, первого элемента И и элемента ИЛИ, выход триггера результата соединен со вторыми входами первого элемента И и элемента ИЛИ третьи входы первого элемента И и эле мента ИЛИ соединены с вторыми входами операционного триггера и триггера результата и с выходом триггера конъюнк тивной формы, выходы первого элемента И и элемента ИЛИ соединены с информационным входом второго узла инвертирования, -управляющие входы операционного триггера, триггера результата, первого и второго узлов инвертирования и вход триггера конъюнктивной формы соединены с управляющим входом устрой ства, а выход устройства соединен с выходом второго узла инвертирования, дополнительно введены программный генератор, первый и второй делители частоты, элемент задержки, второй и третий элементы И, первый и второй триггеры, информационный триггер и коммутатор, причем управляющие входы коммутатора и программного генератора соединены с управляющим входом устройства, выход программного генератора соединен с информационным входом первого делителя частоты, выход которого соединен с входом элемента задержки, выходы первого и второго делителей частоты соединены соответственно с первыми входами второго и третьего элементов И, выходы которых соединены соответственно с еди-.. ничными установочными входами первого и второго триггеров, прямые выходы которых соединены соответственно с единичным и нулевым установочными входг1ми информационного триггера f выход которого соединен с первым вхо .дом коммутатора, второй входкоторого является булевым информационным входом устройства, выход элемента за держки соединен с нулевыми установоч ными входами первого и второго делителей частоты и первого и второго триггера, инверсные выходы первого и второго триггеров соединены соответственно с вторыми входами третьего и второго элементов И, а выход коммутатоЕ а соединен с информационным вхо . дом первого узла инвертирования, информационный вход второго делителя частоты соединен с аналоговым информационным входом устройства. На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит программный генератор 1, делитель 2 частоты, элемент 3 задержки, делитель 4 частоты, второй и третий элементы И 5 и 6, первый и второй триггеры 7 и 8, информационный триггер 9, коммутатор 10, первый узел 11 инвертирования, операционный триггер 12, триггер 13 результата, триггер 14 конъюнктивной формы, первый элемент И 15, Элемент ИЛИ 16, второй узел 17 инвертирования, входы 18-20 устройства соответственно аналоговый информационный, управляющий И булевый информационный и выход 21 устройства. Устройство работает следующим образом. По первому включению первый импульс с выхода делителя 2 частоты через элемент 3 задержки поступает на нулевые установочные входы первого и второго делителей 2 и 4 частоты и первого и второго триггеров 7 и 8. При поступлении на управляющий вход 19 у-стройства сигнала, соответствующего булевой информации, ког/мутатор 10 подключает булевый информационный вход 20 к информационному входу первого узла 11 инвертирования. При отсутствии на управляющем входе 19 устройства сигнала битовой информации, что соответствует аналоговой информации, коммутатор 10 подключает к информационному входу первого узла 11 инвертирования выход информационного триггера 9, котррый устанавливается в соответствующее состояние области нахождения измеряемого параметра. На управляющий вход программного генератора 1 подается код, соответствующий выбранной граничной частоте для данного параметра. Эта частота поступает на информационный вход первого делителя 2 частоты. Одновременно с этим на информационный вход второго делителя 4 частоты поступает .с информационного аналогового входа 18 устройства измеряемая частота. Первый и второй делители 2 и 4 частоты, имеющие одинаковые коэффициенты еления, сводят ошибку, за счет несовпадения по фазе первых импульсов с аналогового информационного входа 18 и с выхода программного генератора 1 , к минимуму. Принцип сравнения частот основан на различном во времени появлении импульсов на выходах делителей 2 и 4 частоты за счет набега фазы измеряемой частоты относительно установленной граничной частоты. Этот набег фазы может быть как положительным, так и отрицательным, в зависимости от соотношения частот. При значении измеряемой частоты, меньше установленной граничной, импульс на выходе первого делителя 2 частоты появится раньше, чем на выхо де второго делителя 4 частоты. Этот импульс через второй элемент И 5 поступит на единичный установочный вхо первого триггера 7 и установит его в единичное состояние. Единичный сигнал с прямого выхода первого триг гера 7 поступит на единичный установочный вход информационного триггера 9, который установится в единичное состояние. Одновременно с этим нулевой сигнал с инверсного выхода первого триггера 7 поступит на второй вход третьего элемента И 6, вследствие чего будет запрещено прохождение импульса с вькода второго делителя 4 частоты через этот элемент на единич ный установочный вход второго тригге ра 9, что не приведет к изменению состояния информационного триггера 9 При значении измеряемой частоты, выше установленной граничной, на выходе второго делителя 4 частоты импульс появится раньше, чем на выходе первого делителя 2 частоты. Этот импульс поступит через элемент И б на единичный установочный вход второго триггера 8 и установит его в единичНое состояние. -Единичный сигнал с прямого выхода второго триггера 8 поступает на нулевой установочный вход информационного триггера 9, который установится в нулевое состояние. Одновременно с этим нулевой сигнал с инверсного выхода второго триггера 8 поступит на второй вход второго элемента И 5 и запретит прохождение импульса с выхода первого делителя 2 частоты через второй элемент И 5 на первый триггер 7, что не приведет к изменению состояния информационного триггера 9. Импульс с выхода первого делителя 2 частоты поступает также на вход элемента 3 задержки, на выходе которого появится импульс, задержанный на время про хождения сигнала с выхода первого делителя 2 частоты через второй элемент И 5, первый триггер 7 и время, необходимое для установления информа ционного триггера 9 в устойчивое сос тояние. Этот задержанный импульс, по ступая на нулевые .установочные входы первого и второго делителей 2 и 4 частоты и первого и второго триггеров 7 и 8, устанавливает их в исход ное состояние. После этого цикл срав нения частот может быть повторен при необходимости несколько раз, в зави симости от выбранных частот работы. Последующие циклы будут каждый раз подтверждать состояние информационного триггера 9, если область нахож:дения измеряемой частоты не меняется В противном случае, при изменении области нахождения измеряемой частоты относительно установленнойграничной частоты, состояние информационного триггера 9 изменится на противоположное. Следовательно, на выходе информационного триггера 9 будет сигнал, соответствующий области нахождения измеряемой частоты, причем единичному значению соответствует область эна чений измеряемых частот меньших установленному значению граничной часроты, а нулевое значение - области с частотами выае граничной частоты. Полученный, таким образом, ре- . зультат сравнения частот с выхода информационного триггера 9 поступает через коммутатор 10 Дальше для обработки и обрабатывается как обычный булевой сигнал. Далее полученная информация на выходе коммутатора 10 поступает на вход первого узла 11 инвертирования. При наличии сигнала инвертирования, поступаклдего с управляющего входа 19 устройства на управляющий вход первого узла 11 инвертирования, в последнем производится инвертирование информации, поступившей с выхода коммутатора 10. Обработанная таким образом, информация подается на первый вход операционного триггера 12. При наличии на управлякяцем входе 19 устройства сигнала начала предложения -и отсутствие сигнала конъюнктивной в операционный триггер 12 заносится информация с выхода первого узла 11 инвертирования, а триггер 13 результата и триггер 14 конъюнктивной формы устанавливаются в нулевое состояние-. При нaJIИчии сигнала конъюнк-. тивной формы операционный триггер 12, триггер 13 результата и триггер 14 конъюнктивной формы устанавливаются в единичное состояние. При наличии на управляющем входе 19 устройства сигнала дизъюнкции, нулевом состоянии триггера 14 конъюнктивной формы и единичном - операционного триггера 12, триггер 13 результата устанавливается в единичное состояние,после этого при наличии на выходе первого узла 11 инвертирования единичного сигнала, операционный триггер 12 устанавливается в единичное состояние. При наличии на управляющем входе 19 устройства сигнала конъюнкции, единичном состоянии триггера 14 конъюнктивной формы и нулевом состоянии операционного триггера 12, триггер 13 результата устанавливается р нулевое состояние, после этого при наличии на выходе первого узла 11 инвертирования нулевого сигнала, операционный триггер 12 устанавливается в нулевое состояние. При наличии на управляющем входе 19 устройства сигнала указания в. еди ничном состоянии триггера 14 конъюнк тивной формы на информационный вход второго узла 17 инвертирования подается информация с первого элемента И 15, при нулевом состоянии триггера 14 конъюнктивной формы на второй узе 17 инвертирования подается информаци с элемента ИЛИ 16, если при этом на управляющий вход второго узла 17. инвертирования подается сигнал инвертирования, .производится инвертирование информации, поступившей на его информационный вход, и выдача ее на выход 21 устрОйЬтва. При отсутствии сигнала инвертирования второй узел 17 инвертирования пропускает поступившую на его информационный вход ийформацию, не изменяй ее. Осуществляя таким образом последо вательную обработку булевой и анало,говой частотной информации, формирую значения логического выражения. Таким образом,.предлагаемое устройство позволяет обрабатывать как булевые, так и аналоговые сигналы от частотных датчиков в такой степени, как это необходимо в устройствах программно-логического управления различными технологическими процессами. Формула изобретения Устройство для вычисления булевых функций, содержащее операционный триггер, триггер результата, первый, элемент И, элемент ИЛИ, триггер конъ юнктивной формы, первый и второй узлы инвертирования, причем выход, пер«вого узла инвертирования соединен с первым входом операционного триггера выход которого соединен с первыми вх дами триггера результата, первого эл мента И и элемента ИЛИ, выход тригге ра результата соединен со вторыми вх дами первого элемента И и элемента ИЛИ, третьи входы первого элемента И и элемента ИЛИ соединены с вторыми входами операционного триггера и три гера результата и с выходом триггера конъюнктивной формы, выходы первого элемента И и элемента ИЛИ соединены с информационным входом второго узла инвертирования, управляющие входы опе рационного триггера, триггера результата, первого и второго узлов инвер- . тирования .и вход триггера конъюнктивной формы соединены с управляющим входом устройства, а выход устройства соединен с внкодом второго узла инвертирования, отлич ающеес я тем, что, с целью расширения функциональных возможностей устройства за счет возможности обработки аналоговых сигналов, в него дополнительно введены программный генератор, первый и второй делители частоты,элемент задержки, второй и третий элементы И, первый и второй триггеры, информационный триггер и коммутатор, причем управлякицие входы коммутатора и программного генератора соединены с управляющим входом устройства, выход программного генератора соединен с информационньм входом первого делителя частоты, выход которого соединен с входом элемента задержки, .выходы первого и второго делителей частоты соединены соответственно с первыми входами второго и третьего эл.ементов И, выходы которых соединены соответственно с единичными установочными входами первого и второго триггеров, прямые выходы которых соединены соответственно с единичным и нулевым установочными входами информационного триггера, выход которого соединен с первым входом коммутатора, второй вход которого является булевым информационным входом устройства, выход элемента задержки соединен с нулевыйи установочными входами первого и второго делителей частоты и первого и второго триггеров, инверсные выходы первого и второго триггеров соединены соответственно со вторыми входами третьего и второго элементов И, а выход коммутатора соединен с информационным входом первого узла инвертирования, информационный вход второго делителя частоты соединен с аналоговым информационным входом устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 433475, кл. G Об F 7/00, 1974, 2.Авторское свидетельство СССР 610104, кл. G 06 F 7/00, 1974 (прототип . .

«М

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU798805A1 |

| Устройство для вычисления булевыхфуНКций | 1978 |

|

SU807272A1 |

| Устройство для вычисления булевых функций | 1975 |

|

SU610104A1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство задержки сигналов | 1982 |

|

SU1015491A1 |

| Устройство для считывания графической информации | 1989 |

|

SU1683046A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство формирования времен-НыХ иНТЕРВАлОВ | 1979 |

|

SU824417A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

Авторы

Даты

1982-08-30—Публикация

1979-04-23—Подача