I

Изобретение относится к области вычислительной техники, а более конкретно к схемам ЦВМ и может быть использовано при моделировании цифровых схем с целью их проверки и циагностики.

Известно устройство для моделирования логических схем, содержащее блоки памяти, блок вычисления ло ических функций, коммутаторы, элементы И, блок сравнения и блок управления f 1 ,

Недостатком известного изобретения является невозможность моделирования конечных автоматов, содержащих неисправности.

Наиболее близким по техническому решению к предлагаемому является устройство, содержащее первый блок памяти, мультиплексор, выход которого подключен к первому входу сумма-; тора по модулю цва, второй вход которого соединен с первым выходом первого блока памяти, первый и второй

выходы сумматора по модулю два подключены к первому и второму входам блока вычисления булевых функций, группа входов которого соединена с выходами первого дешифратора, первый регистр, выходы которого соединены со входом второго дешифратора, второй регистр, вых«эаы которого подключе1гы к первой группе входов мульти-, плёксора. {2.1.

Недостатком известного устройства является сложность подготовительных операций, необходимых при моделировании неисправностей, возникающих в конечном автомате.

Цель изобретения - расширение функциональных возможностей за счет моделирования ксиечных автоматов с учетом неисправностей автомата.

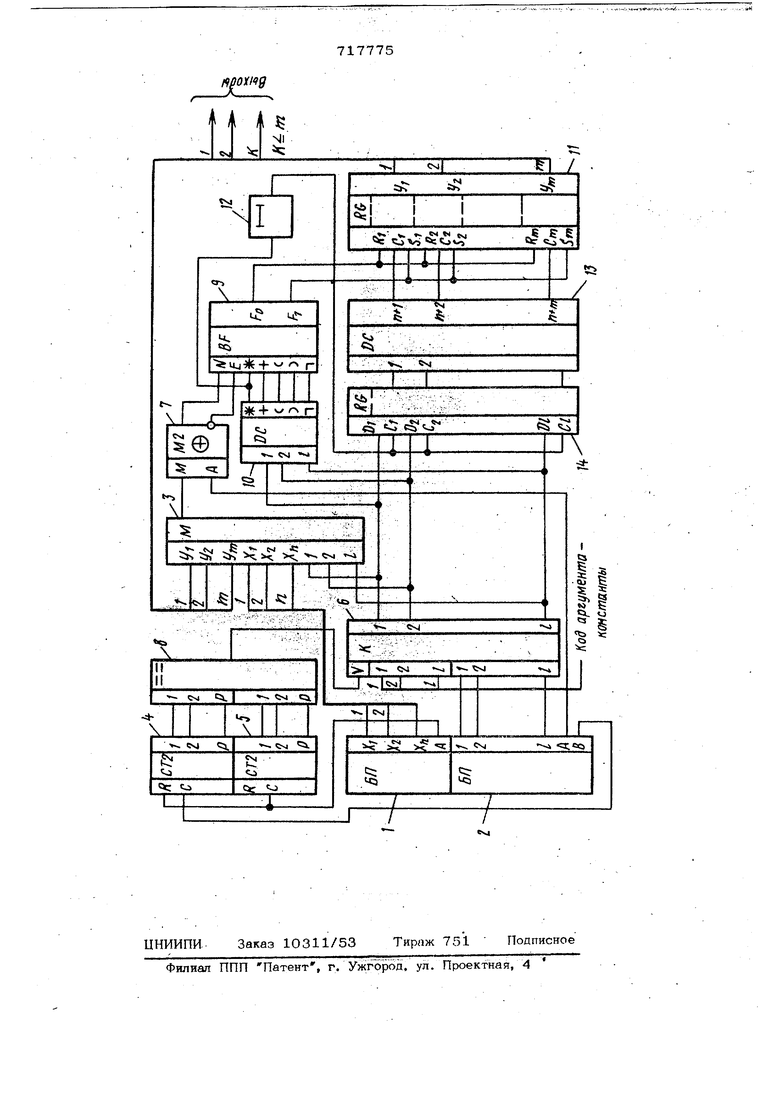

Поставленная цель достигается тем, что в устройство дополнительно введены второй блок памяти, коммутатор, .первый и второй счетчики, блок ера&нения и элемент задержки, причем пер-. -. - -3 -;---вый выход второго блока памяти подключен ко входу первого счетчика и к первому входу второго счетчика, второй вход которого соединен со вторым выходом первого блока памяти, выходы первого и второго счетчиков подключены ко входам блока сравиения, выход коФорого соединен с первым входом ком мутатора, первая группа входов которо.го соединена с входом устройств, вторая группа входов коммутатора coetuiнена с выходами первого блока памяти, выходы коммутатора подключены ко второй группе входов мультиплексора, ко входам первого дешифратора и к первой группе входов первого регистра, вторая группа входов которого через элемент задержки соединена b первым выходом первог аешифратьра, вь ходы второго дешифратора подключен к первой группе входов второго регистра, вторая и третья группы входов которого соединены с первым и вторым вьгходами блока вычисления булевых фу кций, группа выходов второго блока памяти подключена к третьей группе входов мультиплексора. Описываемое устройство представлено на чертеже. Оно содержит блоки памяти 1 и 2, мультиплексор 3, счетчики 4 и 5, коммутатор 6, сумматор по Модулю два 7, блок сравнения 8, блок вычисления булевых функций 9, дешифратор служебных символов 10, регистр внутренних переменных 11, эле мент задержки 12, дешифратор внутрен них переменных 13, регистр функций 1 Устройство работает следующим образом. Моделируемый конечный автомат описывается в виде системы булевых функций. Эти функции должны быть представлены в форме, при которой знаки отрицания относятся либо тйлько-;к одному аргументу, либо ко 1всему аналитичеокому выражению функций, знaк равенсг ва удаляется, а перед символом функции и в конце всей системы ставится символ . Например, система функций будет представлена следующим образом , VsC «Л :Записанная геаааЛ образом сйстемй функций кодируется позначно и уводится в блок памяти 2. В блок памяти 1 5.4 вводится массив, отражающий времендую диаграмму входных сигналов моделируемого объекта в вице меняющихся переменных х, При моделировании конечного автоМата без неисправностей в блок памяти 1 вводится единица в разряде А первого слова, а в блок памяти 2 в разряде В будут нули. При этом в начале моделирования счетчики 4 и 5 устанавливак тся соответственно в состояния О и , которые сохраняются до конца моделирования, т.е. до полного считывания блока памяти 1. На выходе схемы сравнения 8 будет все время нуль и коммутатор 6 будет пропускать информацию с блока памяти 2. .Информация с блока памяти 2 будет подаваться ци|слически, причем каждому циклу соответствует одна итерация моделируемой схемы. Один или несколько циклов блока памяти 2 соответствуют выборке очередного слова блока памяти 1. Ири каждом цикле блока памяти 2 будет произ.водиться вычисление значений, булевых функций, хранящихсяв нем, и для каждого набора аргументов будет вычислен набор значений функций. Это происходит следующим образом. Первый выведенный из блока памяти 2 символ будет дешифрован дешифратором 10, который подаст сигналы на блок вычисления булевых функций 9 и элемент задержки 12, с выхода которого задержанный сигнал запишет в регистр функций 14 код функции, следующий за знаком . Код функции будет дешифрован дешифратором внутренних переменных 13, и на соответствую- щий триггер регистра внутренних переменных 11 будет подан разрешающий потенциал, т.е. будет выбрана вычисляемая функция. Следующий за знаком функции знак аргумента будет воздействовать на Мультиплексор 3 по входам 1, 2, .... с и соответствующее значение аргумента 9 одного из его входов; .;.%.У1-«г-Ут . , подано на выход мультиплексора 3,, . после чего поступит на вхой М сумматора по модугар два 7. Одновременно будет подан разряд А с блока памяти 2 на вход А сумматора по модулю два 7. Сравнение сигналов, поступивших на входы сумматора по модулю два 7 обеспечит подачу одного из сигналов Ё или Н на входы блока вычисления булевых функций 9. Сигналы Е или N будут появляться на входах 9 каждый раз при считывании аргументов, и их значения являются результатом подстановки KoHRpeTHbui значений аргументов на входах мультиплексора 3 в ана .литическое выражение функции. Кроме этсс сигналов на вхооы блока вычисления булевых функций 9 подаются сигналы + ,С ,Э и 1с выходов

дешифратора служебньк символов в ре зультате дешифрации кодов этих символов. Эти символы имеют следующие значения: - символ стоящий перед символом функции, порождающий сигнал записи кода функции в регистр М, + - символ дизъюнкции, с иО - СИМ- волы скобок и 1 - символ отрицания, означаюший отрицание функции и сто- ящий в конце пиалптического выраже-. ния функции. Подацнь е в определенной последо.вательности сигналыЫ ,Е , ,ЧС,0и1 на входы блока вычисления булевых функций 9 при выводе из блока памяти 2 аналитического выражения функции обеспечат вычисление конкретного значения функции блоком 9 и появление в результате одного из сигналов F или FI на его выходе. Этот сигнал запишет значение вь1численной булевой функции в один из триггеров регистра внутренних переменных 11. Все следующие булевые функции будут вычислены аналогичным образом. Вычисленные значения булевых функций подаются на входы мультиплексора 3

и могут участвоЕ ать

У,У

,У

2.1

гл

в дальнейших вычислениях. 3 результате многократного вычисления функций на выходах регистра внутренних переменных 11 формируется временная зиаграмма выходных сигналов.

Моделирование неисправностей конечного автомата происходит следующим образом. .

Блок памяти 1 заполняется так же, как при моделировании без неисправностей. В блок памяти 2, кроме сяисания моделируемой схемы, вводится список неисправностей в виде единиц в разряде В. Первое считываемое слово блока памяти 1 установит счетчик 4 в состояние О, а счетчик 5 отсчитает единицу в разряде А блока памяти 1. После этого начнется вывод информации блока памяти 2. При этом первая моделируемая неисправность заданного списка в разряде В будет от считана счетчиком 4, в результате

чего на выходе схемы сравнения 8 . явится единица, которая будет подана на управляющий вход V коммутатора 6, в результате чего на выход коммутатора будет пропущен код аргумента-константы, т.е. код одной из переменных, предва1рительно зафиксированных на нуле либо йа единице на одном из входов .V п 11У2-Уг 1 мультиплексора 3. При дальнейшем выводе информации из блока памяти 2 счет чик 4 будет подавать на выход 1,2, ...., Р двоичные цифры 2, 3, 4, ... и т.д., а счетчик 5 будет сохраняться в состоянии 1 до окончания вывода

информации из блока памяти 1. При этом на выход схемы сравнения 8 до конца считывания содержимого блока памяти 1 будет подаваться О и коммутатор 6 будет пропускать информацию из блока памяти 2. В результате этого при первом цикле блока памяти 1 моделируется первая неисправность списка, хранящегося в блоке памяти 2. Второй, третий и дальнейшие циклы блока па. мяти 1 будут моделировать вторую, третью и дальнейшие неиспоавности.

При этом на выходах регистра внутренних переменньк11 будут формироваться временные диаграммы при различных неисправностях. Эти временные диаграммы могут быть использованы для построения таблиц неиспра ностей, диагностических словарей или для проверки полноты текстов.

Устройство для моделирования конечных автоматов благодаря наличию блоков и связей между ними позволяет существенно снизить затраты ручного труда при моделировании конечного автомата с неисправностями.

45 ф

ормула изобретения

Устройство ОЛЯ моделирования автоматов, содержащее первый блок памяти, мультиплексор, выход которого подключен к niepBtwy входу сумматора по модулю два, второй ЕЖОД которого соединен с первым выходом первого блока памяти, перыз1й и второй выходы сумматора по модулю два подключены к первому и второму входам блока вычисления булевых функций, группа входов которого соедийена с выходами первого дешифратора, йервый регистр.

Ёьцсопы которого соегшнены со входом второго дешифратора, второй регистр, выхооы которого пооключёнь к. первой группе входов мультиплексора, о т л и ч а ю щ ё ее я тем, что, с целью расширения фуикщональных вoзмoжнooтей за счет моделирования конечных автоматов с учетом неисправностей автомата, в устройство дополнительно введены второй блок памяти, коммутатор, первый и второй счетчики, блок сравнения и элемент задержки, причем первый выход второго блока памяти подключён ко входу первопэ счетчика и к Новому входу второго счетчика, второй вход которого соединен со вторым выхооом первого блока памяти, выходы первого и второго счетчиков подключены ко восодам блока сравнения выход которого соединен с первым входом коммутатора, первая группа входов которого соёдйиён а йо нходой yci ройства, вторая группа входов коммутатора соединена с ш исодами первого блока памяти, выходы коммутатора

подключены ко второй группе входов мультиплексора, ко входам первого дешифратора и к первой груте вхопов первого регистра, вторая группа ЕКОПО которого через элемент задержки соединена с первым выходом первого де- шифратора, выходы второго дешифратора подключены к первой группе входов второго регистра, вторая и третья группы входов которого соединены с первым и вторым выходами блока вычисления булевых функций, группа выходов второго блока памяти подключена к третьей группе входов мультиплексора.

Источники информации, .принятые во внимание при экспертизе

1.Авторское свидетельство № 471587, кл. G 06 F 15/2О, 03.05.73.

2.Авторское свидетельство СССР N9 383О43, кл. G 06 F 7/38, 10.11.69.

i pojiitg

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ КОНЕЧНЫХ АВТОМАТОВ | 1973 |

|

SU383043A1 |

| Устройство для моделирования конечных автоматов | 1988 |

|

SU1520534A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для реализации булевых функций | 1982 |

|

SU1032451A1 |

| Логический вычислитель в системе остаточных классов | 2016 |

|

RU2637488C1 |

| Устройство для извлечения корня п-й степени | 1979 |

|

SU883898A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2007 |

|

RU2373564C2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

Авторы

Даты

1980-02-25—Публикация

1977-03-21—Подача