N

4i Ч О5 ЬР

Изобретение отйосится к вычислительной технике, а именно к программному управлению технологическим оборудованием, и может быть использовано при построении программируемых устройств управления.

Цель изобретения - расширение области применения устройства за счет самоконтроля.

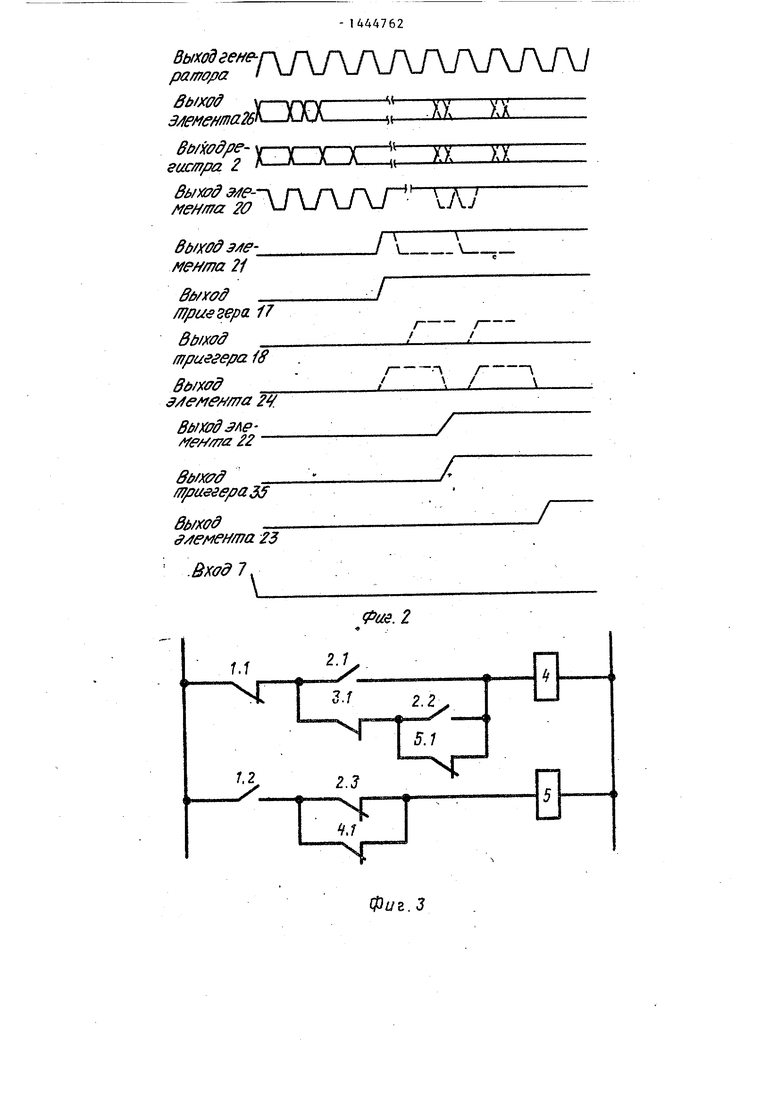

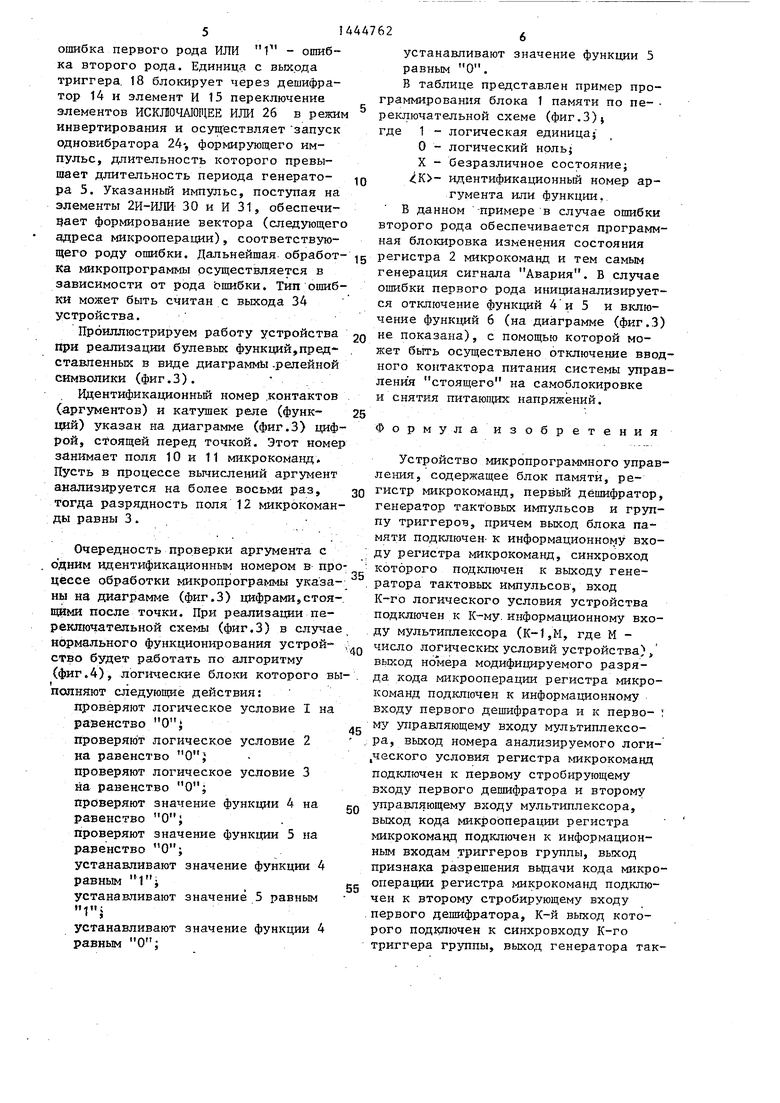

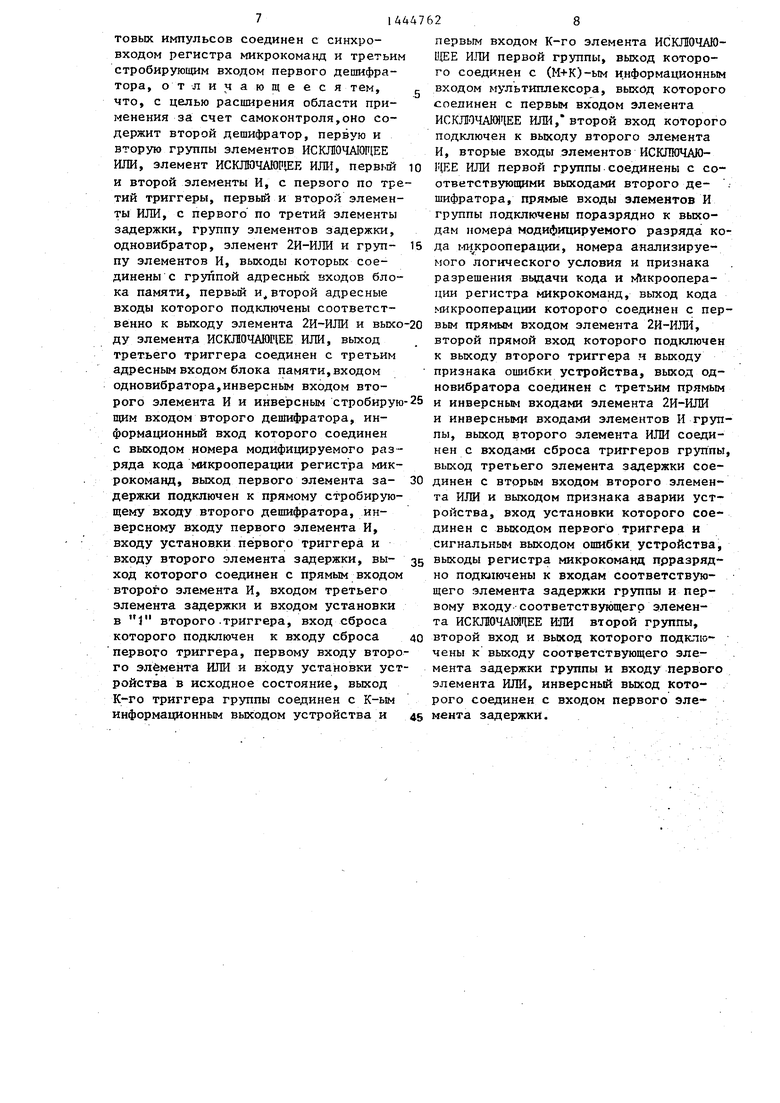

На фиг.1 изображена структзгрная схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройства, иллюстрирующие взаимное расположение сигналов на выходах блоков устройства} на фиг.З - переключательная схема, изображенная в виде диаграммы релейной символики; на фиг,4 - блок-схема алгоритма работы устройства;;

J Устройство содержит дамя- ти, регистр 2 микрокоманд, первый дешифратор 3, мультиплексор 4, генератор 5 импульсов, группу триггеров 6, Вход 7 начальной установки устройст- за, вход 8 логических условий ус трой- ства, инфррмационньй вькод 9 устрой- ства, выход 10 номера модифицируемого разряда кода микрооперации, выход 11 номера анализируемого логического условия, выход 12 кода микрооперации, выход 13 признака разрешения выдачи кода микрооперации, второй дешифратор 14, второй 15 и первый 16 элементы И, первьй 17 и второй 18 . Триггеры, второй 19 и первьй 20 элементы ИЛИ, первьй 21, второй 22 и тртий 23 элементы задержки, одновибра- Тор 24, первую группу элементов ИСК- ЛОЧАЮЩЕЕ ИЛИ 25, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26, втору группу ИС ШОЧАЮЩЕЕ ИЛИ 27, группу элементов 28 задержки, выходы 29 триггеров группы, элемент 2И-Ш1И 30, группу элементов И 3t, выход 32 признака аварии, вы- ход 33 признака ошибки и вьтод 34 типа ошибки.

Устройство работает спедуюшдм образом.

Значения логических условий поступают через вход 8 устройства -и циклически анализируются. Вычисленные в виде кода микрооперации значения фунций запоминаются в триггерах 6 и поступают на вькод 9 устройства. В каждом такте микрокоманда из блока 1 памяти загружается в регистр 2 микрокоманд. Адрес следующей микрокоманды формируется в соответствии со значе

0

s 0

5 о ддд

0

5

нием (О или 1) анализируемого аргумента - логического условия или промежуточного результата вычисления (фракции), подаваемого через мультиплексор 4 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26 на третий адресный вход блока 1 памяти и содержимого регистра 2 микрокоманд, поступающего.на адресные входы блока 1 памяти. Если ана- лизируемьй аргумент входит в вычисляемую булевую функцию с инверсией и равен 1 или входит без инверсии и равен О, то из блока 1 памяти выбирается следующая микрокоманда, соответствующая аргументу, входящему в дизъюнкцию к анализируемой части функции. Если такая дизъюнкция отсутствует, то выбирается следующая икpoкo- манда, инициализирующая через первьй , дешифратор 3 установку в О соответствующего триггера 6 группы. Если анализируется аргумент, входяЩий в вычисляемую булевую функцию с инверсией и равньй О 1-ши входящий без инверсии и равньй 1, то из блока 1 памяти выбирается следующая микроко- анда,.соответствующая аргументу,входящему в конъюнкцию к анализируемой части функции. Если таковая конюнк- ция-отсутствует, то выбирается еле- дующая микрокоманда, инициализирующая через дешифратор 3 установку в 1 соответствующего триггера 6 группы.

Если вьшолняется микрокоманда, инициализирующая установки триггеров 6 группы в состояние О или 1, то выход триггера 6 контролируется через элемент ИСКЛОЧАЮЩЕЕ ИЛИ 25 пбр- вой группы, мультиплексор 4 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26. Если состояние триггера 6 группы совпадает с желаемым, то выбирается следующая микрокоманда, соответствующая проверке аргумента для вычисления очередного кода микрооперации. Если состояние триггера 6 группы не совпадает с желаемым, то снова выбирается микрокоманда, соответствующая требуемой .установке.

Выбранная микрокоманда в следующем такте загружается в регистр 2 микрокоманд, и вьш1еуказанньй процесс возобновляется.

Запись в регистр 2 микрокоманд может инициализировать по положительному фронту импульсов с генератора 5, а запись кода микрооперации в тригrep 6 группы - по отрицательному фронту.

Перед началом работы устройства на вход 7 начальной установки подается иг пульс установки в исходное состояние, длительность которого превьша- ет максимально возможное время, необходимое для вычисления кода микрооперации, при этом осуществляется сброс триггеров 6 группы, а также с первого по третий триггеров устройства (фиг,2).

В случае нормального функционирования О с выхода первого элемента 21 задержки обеспечивает блокировку второго дешифратора 14, при этом низкие уровни сигналов на выходах послед.

15 новкой сигнала 1 на выходе 33 признака ошибки устройства. Единичньй сигнал с выхода элемента Х1 задержки разрешает работу дешифратора 14, который обеспечивает перевод элемента

него, поступая на одни входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой гр1Т1пы, 20ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой группы, дают возможность для работы этихсоответствующего выходу устройства, элементов в режиме повторения сигна- определяемому номером модифицируемо- лов на их других входах. Сигнал О .го разряда кода микрооперации, в ре- с выхода второго элемента 22 задержкижим инвертирования входной информа- поступаег через второй элемент И 15 25.ции. При этом по переключению выходов на вход элемента ИСКЛОЧАЮГЩЕ ИЛИ 26,регистра 2 микрокоманд судят о на- обеспечивая прохождение сигнала с мультиплексора 4 на блок 1 памяти без инверсии. Сигнал О с выхода третьего триггера 18 через одновибратор 24 зомикрокоманд не протпо через время, поступает на входы элементов 2И-ИЛИ 30превышающее длительность одного цик- иИ 31,обеспечивая беспрепятственноела генератора 5, то срабатывает вто- прохождение информации с выхода ре-рой элемент 22 задержки и через гистра 2 микрокоманд на входы бло-элемент И 15 элемент ИСКЛЮЧАЮЩЕЕ.

ка 1 памяти.ЧсИЛИ 26 переводится в режим инверти 5Ь„ . J

В случае нарушения работы устройства (например, из-за нарушения конличии ошибки первого ряда (например, перегорание одного из предохранителей) . Если переключение регистра 2

рования входной информации. Йсли и после этого переьслючение регистра 2 микрокоманд, свидетельствующее о наличии ошибки второго рода, ие протактов разъемных соединений, связывающих узлы устройства, выхода из

обеспечивающее достоверное определение нарушения в работе устройства и имеет малое время восстановления. Элементы 28 задержки группы настроены на время задержки, равное половине длительности периода генератора 5, обеспечивающее формирование на выходе элемента ИЛИ 20 импульса, перекрывающего по длительности время восстановления элемента 21 задержки. Появ- ление 1 на выходе элемента 21 задержки фиксируется в триггере 17 усI111I

15 новкой сигнала 1 на выходе 33 признака ошибки устройства. Единичньй сигнал с выхода элемента Х1 задержки разрешает работу дешифратора 14, который обеспечивает перевод элемента

0ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой группы, соответствующего выходу устройства, определяемому номером модифицируемо- .го разряда кода микрооперации, в ре- жим инвертирования входной информа- 25.ции. При этом по переключению выходов регистра 2 микрокоманд судят о на- зомикрокоманд не протпо через время, превышающее длительность одного цик- ла генератора 5, то срабатывает вто- рой элемент 22 задержки и через элемент И 15 элемент ИСКЛЮЧАЮЩЕЕ.

ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой группы, соответствующего выходу устройства, определяемому номером модифицируемо- го разряда кода микрооперации, в ре- жим инвертирования входной информа- ции. При этом по переключению выходов регистра 2 микрокоманд судят о на- микрокоманд не протпо через время, превышающее длительность одного цик- ла генератора 5, то срабатывает вто- рой элемент 22 задержки и через элемент И 15 элемент ИСКЛЮЧАЮЩЕЕ.

личии ошибки первого ряда (например, перегорание одного из предохранителей) . Если переключение регистра 2

„ . J

рования входной информации. Йсли и после этого переьслючение регистра 2 микрокоманд, свидетельствующее о наличии ошибки второго рода, ие про

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1984 |

|

SU1236476A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Система для программного управления резервированными объектами и их диагностирования | 1989 |

|

SU1741295A1 |

Изобретение относится к области вычислительной техники, а именно к программному управлению технологическим оборудованием, и может быть использовано при построении программируемых контроллеров. Цель изобретения - расширение области применения за счет самоконтроля. Устройство микропрограммного управления содержит блок памяти, регистр микрокоманд, дешифраторы, мультиплексор, генератор тактовых импульсов, группу триггеров, группы элементов ИСКЛОЧАЮ- ЩЕЕ ИЛИ, элемент ИСКЛОЧАКЯЦЕЕ ИЛИ, элементы И, триггеры, элементы ИЛИ, элементы задержки, группу элементов задержки, одновибратор, элементы 2И-ИЛИ, группу элементов И. Устройство позволяет идентифицировать три приоритетных уровня ошибки, переходить к выполнению микропрограммы по обработке аварийного режима или „осуществлять экстренное отключение устройства, а также обеспечивает сигнализацию наличия и уровня -ошибки. 4 ил., 1 табл. о S (Л

строя триггеров 6 группы, регистра 2 40 изошло через время, превьшгающее дш1тельность цикла генератора 5, то срабатывает третий элемент 23 задержки, в результате чего на выходе 32 устроймикрркоманд, мультиплексора 4, генератора 5 и т.п.) информация на выходе регистра 2 микрокоманд перестает сменяться. Обеспечение фиксации одной и той же информации в регистре 2 45 зирующий об аварии, через элемент микрокома щ может быть.осуществлено ИЛИ 19 осуществляется сброс тригге- программно, т.е. в результате повто- реьшя циклов выбора одной и той же микрокоманды при неудовлетворительной инициализации циклов записи очередно- 50 го кода микрооперации в триггеры б группы. При этом на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 27 второй группы перестают появляться импульсы, осуществляющие через элемент ИЛИ 20 сброссс с первого по третий элементы задерж- первого элемента 21 задержки. Эле- .ки, в.результате чего на выходе элемент 21 задержки обеспечивает задерж- мента И 16 появляется 1, устанар- . ку сигнала высокого уровня на вре- .ливающая триггер 18. При этом в триг- мя (несколько циклов генератора 5), . гере 35 фиксируется тип ошибки: О

ства появляется сигнал 1, сигнапиров 6 группы и обеспечивается отключение устройства от объекта управления.

Если была зафиксирована ошибка первого или второго рода, т.е. про- изопшо переключение регистра 2 микрокоманд., то на выходе элемента ИЛИ 20 формируется импульс, сбрасывающий

изошло через время, превьшгающее дш1тельность цикла генератора 5, то срабатывает третий элемент 23 задержки, в результате чего на выходе 32 устройзирующий об аварии, через элемент ИЛИ 19 осуществляется сброс тригге- с первого по третий элементы задерж- .ки, в.результате чего на выходе элемента И 16 появляется 1, устанар- . .ливающая триггер 18. При этом в триг- гере 35 фиксируется тип ошибки: О

зирующий об аварии, через элемент ИЛИ 19 осуществляется сброс тригге- с первого по третий элементы задерж- ки, в.результате чего на выходе элемента И 16 появляется 1, устанар- . ливающая триггер 18. При этом в триг гере 35 фиксируется тип ошибки: О ства появляется сигнал 1, сигнапизирующий об аварии, через элемент ИЛИ 19 осуществляется сброс тригге- с первого по третий элементы задерж- .ки, в.результате чего на выходе элемента И 16 появляется 1, устанар- . .ливающая триггер 18. При этом в триг гере 35 фиксируется тип ошибки: О ров 6 группы и обеспечивается отключение устройства от объекта управления.

Если была зафиксирована ошибка первого или второго рода, т.е. про- изопшо переключение регистра 2 микрокоманд., то на выходе элемента ИЛИ 20 формируется импульс, сбрасывающий

514

ошибка первого рода ИЛИ Т - ошибка второго рода. Единица с выхода триггера, 18 блокирует через дешифратор 14 и элемент И 15 переключение элементов ИСКЛОЧАЮЩЕЕ ИЛИ 26 в режим инвертирования и осжествляет запуск одновибратора 24-, формирующего импульс, длительность которого превышает длительность периода генерато- pa 5. Указанный импульс, поступая на элементы 2И-ИЛИ 30 и И 31, обеспечивает формирование вектора (следующего адреса микрооперации), соответствую

щего роду ошибки. Дальнейшая обработ- jg регистра 2 микрокоманд и тем самым

ка микропрограммы осуществляется в зависимости от рода Ьшибки. Тип ошибки может быть считан с выхода 34 устройства.

Проиллюстрируем работу устройства при реализации булевых функций,представленных в виде диаграммы -релейной символики (фиг.3).

Идентификациоиньй номер .контактов Саргументов) и катушек реле (функций) указан на диаграмме (фиг.З) цифрой, стоящей перед точкой. Этот номер занимает поля 10 и 11 микрокоманд. Пусть в процессе вычислений аргумент анализируется на более восьми раз, тогда разрядность поля 12 микрокоманды равны 3,

Очередность проверки аргумента с одним идентификационным номером в процессе обработки микропрограммы указаны на диаграмме (фиг.З) цифрами,стоя- щщ после точки. При реализации переключательной схемы (фиг,3) в случае нормального функционирования устрой- , ство будет работать по алгоритму

45

(фиг.4), лопиеские блоки которого вы- . да кода микрооперации регистра микро- полняют следующие действия;

тфоверяют логическое условие I на

равенство

проверяют логическое условие 2

на равенство

проверяют логическое условие 3

на равенство

проверяют значение функции 4 на

50

команд подключен к информационному входу первого дешифратора и к перво- му управляющему входу мультиплексора, выход номера анализируемого логи- ,ческого условия регистра микрокоманд подключен к первому стробирующему входу первого дешифратора и второму управляющему входу мультиплексора, выход кода микрооперации регистра микрокоманд подключен к информационным входам триггеров группы, вькод признака ра зрешения вьщачи кода микрооперации регистра микрокоманд подключен к второму стробирующему входу .первого дешифратора, К-й выход которого подключен к синхровходу К-го триггера группы, выход генератора такравенство

проверяют значение функции 5 на

равенство

устанавливают значение функции 4

равным

устанавливают значение 5 равным

)

устанавливают значение функции 4 равным

устанавливают значение функции 5 равным О.

В таблице представлен пример программирования блока 1 памяти по пе- реключательной схеме (фиг.З) где 1 - логическая единица- О - логический ноль; X - безразличное состояниеj идентификационный номер аргумента или функции. В данном -примере в случае ошибки второго рода обеспечивается программная блокировка изменения состояния

генерация сигнала Авария, В случае ошибки первого рода иницианализирует- ся отключение функций 4 и 5 и включение функций б (на диаграмме (фиг.З) не показана), с помощью которой может быть осуществлено отключение вводного контактора питания системы управления стоящего на самоблокировке и снятия питаюпрсс напряжений.

Формулаизобретения

Устройство микропрограммного управления, содержащее блок памяти, регистр микрокоманд, первьй дешифратор, генератор тактовых импульсов и группу триггеров, причем выход блока памяти подключен- к информационному входу регистра микрокоманд, синхровход которого подключен к вькоду генератора тактовых импульсов-, вход К-го логического условия устройства подключен к К-му. информационному входу мультиплексора (К-1,Ы, где М - число логических условий устройства) вькод номера модифицируемого разря5

. да кода микрооперации регистра микро-

0

5

команд подключен к информационному входу первого дешифратора и к перво- му управляющему входу мультиплексора, выход номера анализируемого логи- ,ческого условия регистра микрокоманд подключен к первому стробирующему входу первого дешифратора и второму управляющему входу мультиплексора, выход кода микрооперации регистра микрокоманд подключен к информационным входам триггеров группы, вькод признака ра зрешения вьщачи кода микрооперации регистра микрокоманд подключен к второму стробирующему входу .первого дешифратора, К-й выход которого подключен к синхровходу К-го триггера группы, выход генератора тактовых импульсов соединен с синхро- входом регистра микрокоманд и третьим стробирующим входом первого дешифратора, отличающеес я тем, что, с целью расширения области применения за счет самоконтроля,оно содержит второй дешифратор, первую и вторую группы элементов ИСКЛОЧАЮПЩЕ ИЛИ, элемент ИСКЛЮЧАЮП1ЕЕ ИЛИ, первый и второй элементы И, с первого по третий триггеры, первый и второй элементы ИЛИ, с первого по третий элементы задержки, группу элементов задержки, одновибратор, элемент 2И-ИЛИ и груп- пу элементов И, выходы которых соединены с группой адресных входов блока памяти, первый и второй адресные входы которого подключены соответственно к выходу элемента 2И-ИЛИ и выхо ду элемеитд ИСКЛОЧАЮР ЕЕ ИЛИ, вькод третьего триггера соединен с третьим адресным входом блока памяти, входом одновибратора,инверсным входом второго элемента И и инверсным стробирую щим входом второго дешифратора, информационный вход которого соединен с выходом номера модифицируемого разряда кода микрооперации регистра микрокоманд, выход первого элемента за- держки подключен к прямому стробирую- щему входу второго дешифратора, инверсному входу первого элемента И, входу установки первого триггера и входу второго элемента задержки, вы- ход которого соединен с прямым входом второго элемента И, входом третьего элемента задержки и входом установки в } второго .триггера, вход сброса которого подключен к входу сброса первого триггера, первому входу второго элемента ИЛИ и входу установки устройства в исходное состояние, выход К-го триггера группы соединен с К-ым информационным выходом устройства и

первым входом К-го элемента ИСКЛОЧАЮ- LHEE ИЛИ первой группы, выход которого соединен с (М+К)-ым информационным входом мультиплексора, выход которого соединен с первым входом элемента ИСКЛОЧАКИ1ЕЕ ИЛИ, второй вход которого подключен к выходу второго элемента И, вторые входы элементов ИСКЛЮЧАЮ- I lEE ИЛИ первой группы соединены с соответствующими выходами второго де- шифратора, прямые входы элементов И группы подключены поразрядно к выходам номера модифицируемого разряда кода t-шкрооперации, номера анализируемого логического условия и признака разрешения вьщачи кода и NftiKpoonepa- ции регистра микрокоманд, выход кода микрооперации которого соединен с первым прямым входом элемента 2И-ИЛ1 1, второй прямой вход которого подключен к выходу второго триггера и выходу признака ошибки устройства, выход одновибратора соединен с третьим прямым и инверсным входами элемента 2И-ИЛИ и инверсными входами элементов И группы, выход второго элемента ИЛИ соединен с входами сброса триггеров группы выход третьего элемента задержки соединен с вторым входом второго элемента ИЛИ и выходом признака аварии устройства, вход установки которого соединен с выходом первого триггера и сигнальным выходом ошибки устройства, выходы регистра микрокоманд прразряд- но подю1ючены к входам соответствующего элемента задержки группы и первому входу соответств5п6щегр элемента ИСКЛОЧАКЯЦЕЕ ИЛИ второй группы, второй вход и вькод которого подключены к выходу соответствующего элемента задержки группы и входу первого элемента ИЛИ, инверсный выход которого соединен с входом первого элемента задержки.

О

о 1 1 1

1 о о о 1

(0) (0) (4) (5) (6)

0о

11 11 11 11

1 о

о .1

о

(0) (4) (5)

(6) (4)

S A/VAyVX/WWX/

Stf/xod у-YTT з/1Рмента26 -л лЛ

BiJ/xodf e- у-u-V sucffipa 2

4V

f

Bb/xiy 9/fe-- n rv r мента Л7 AJ VJ VJ J

23

.Вход 7

. XX XX

4VXX

Фие.г

Фиг.З

Фиъ. It

| Мейзда Ф | |||

| Интегральные схеьва: технология и применение | |||

| М.: Мир, 1981, с | |||

| Деревянное стыковое скрепление | 1920 |

|

SU162A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1236476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-02—Подача