Изобретение относится к автомати,ке и вычислительной технике, в частности к функциональным устройствам, осуществляющих умножение аналоговых сигналов, и может быть использовано в аналоговых вычислительных машинах, в радиотехнических устройствах различного назначения (в модуляторах, детекторах и т.д.),а также в электроизмерительной технике.

Известен аналоговый умножитель, содержащий четыре интегратора в це/пях обратной связи, десять ключей, источники опорных и тестовых напряжений. Этот умножитель (при условии дополнения его схемой программного управления ключами) может быть использован как четырехквадратный умножитель , работающий в режиме разделения времени, когда в первую половину периода он настраивается на минимальное значение статической ПОР решности, во вторую половину перио-j

да осуществляется собственно операция перемножения двух информационных сигналов, затем цикл настройкаперемножение повторяется и т.д.1. Недостатком умножителя является то, что для осуществления перемножения сигналов в течение всего периода (чтобы исключить потерю информации во время цикла настройки ум,Q ножителя на минимальную статическую погрешность) необходимо двухканальное устройство, действующее в режиме разделения времени по каналам, т.е. аппаратурные затраты воз

15 растают примерно вдвое, т.е. устройство становится чрезмерно сложным. Наиболее близким к предлагаемому по технической сущности является аналоговый умножитель, содержащий блок

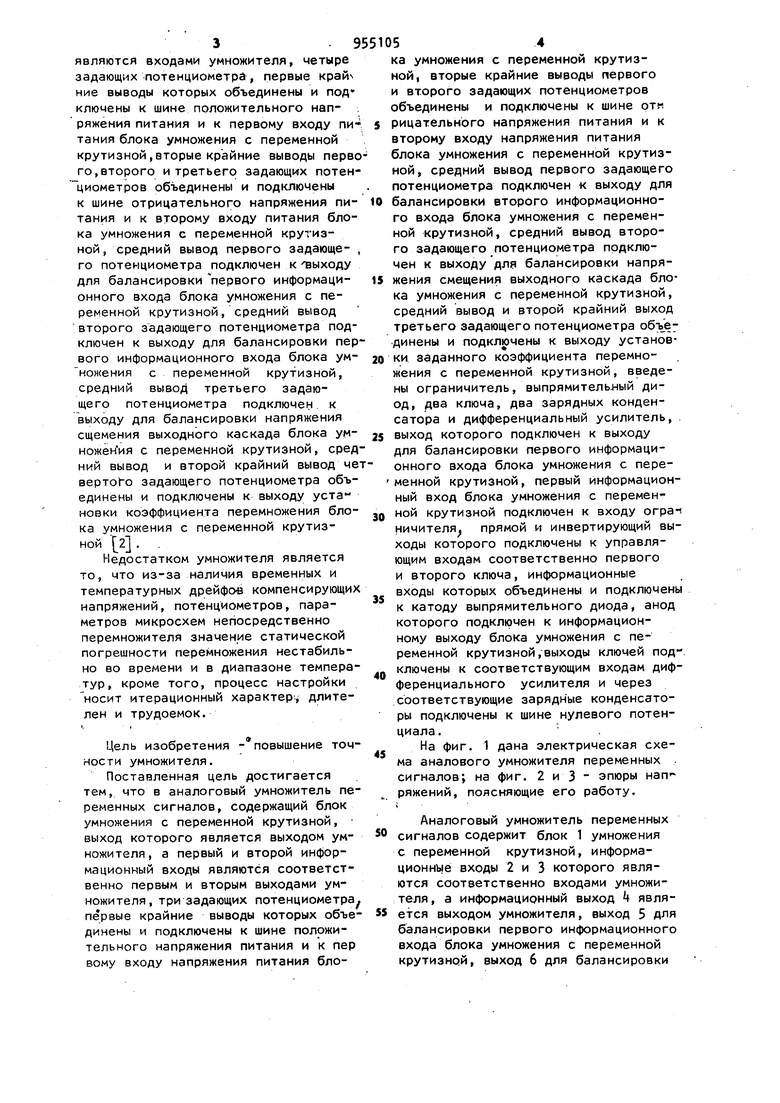

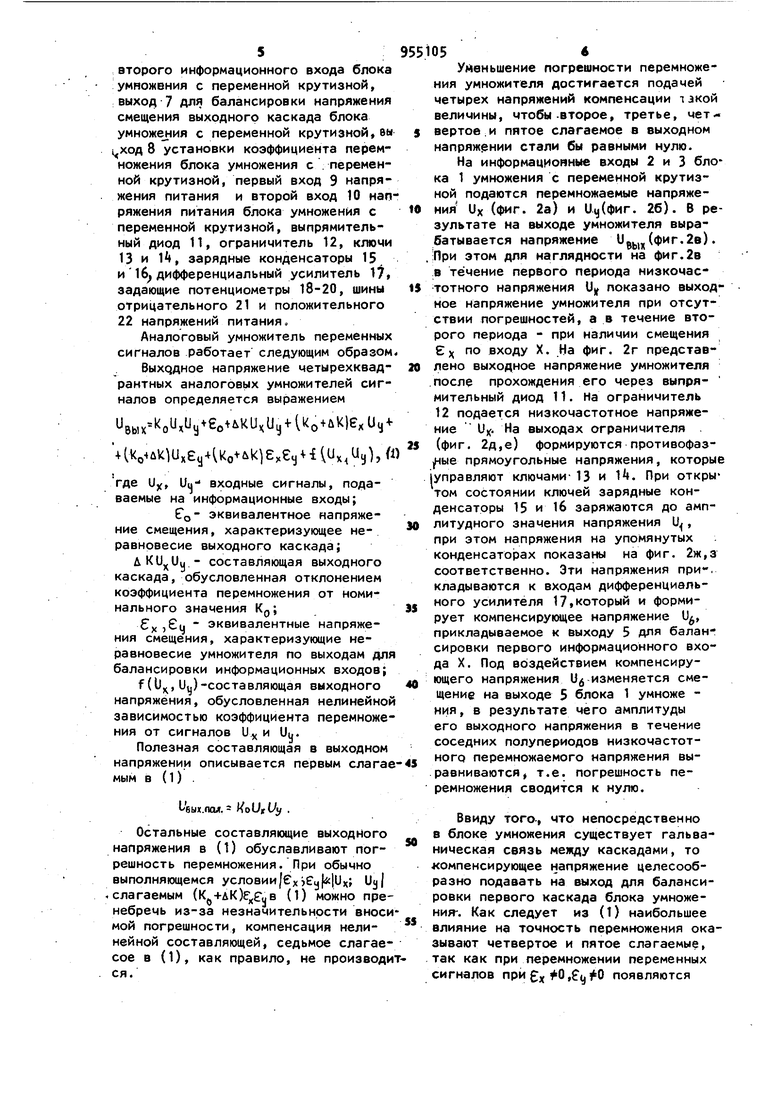

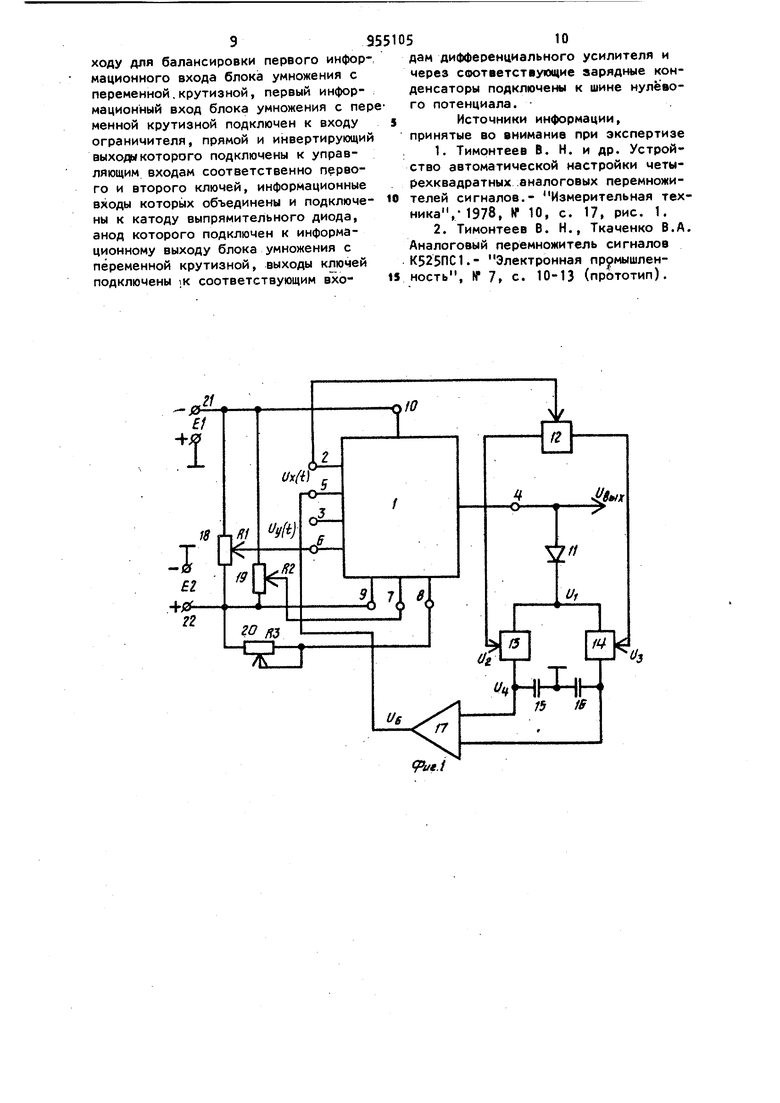

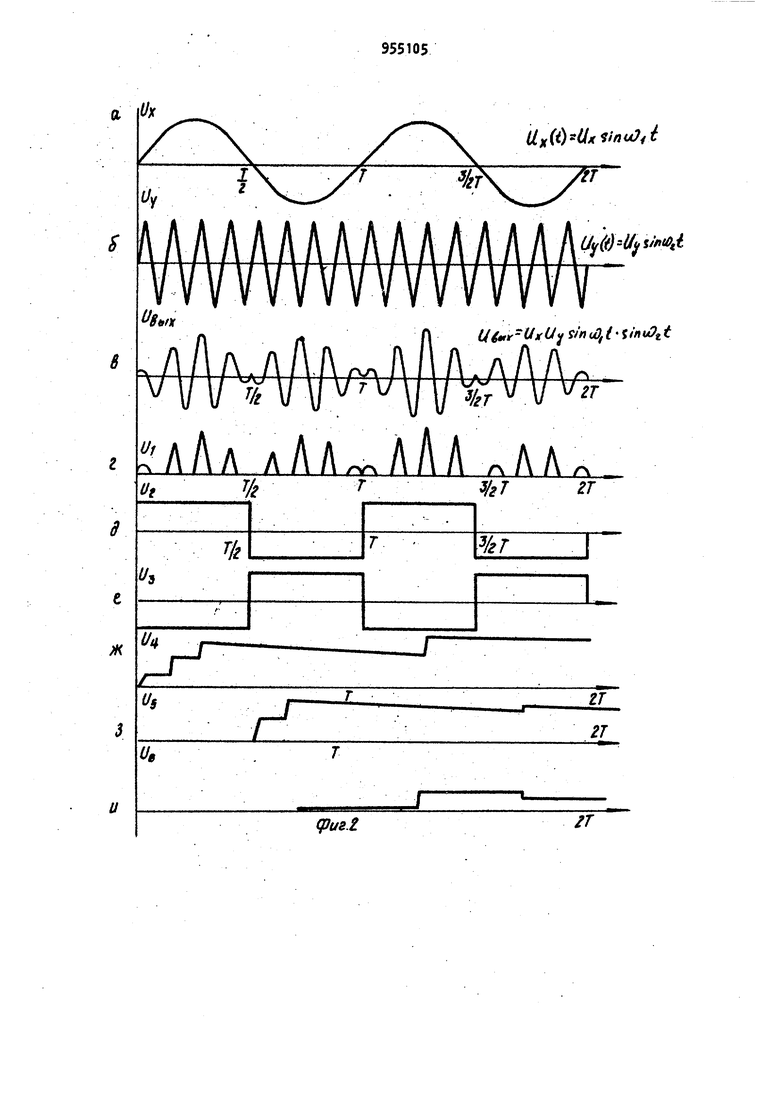

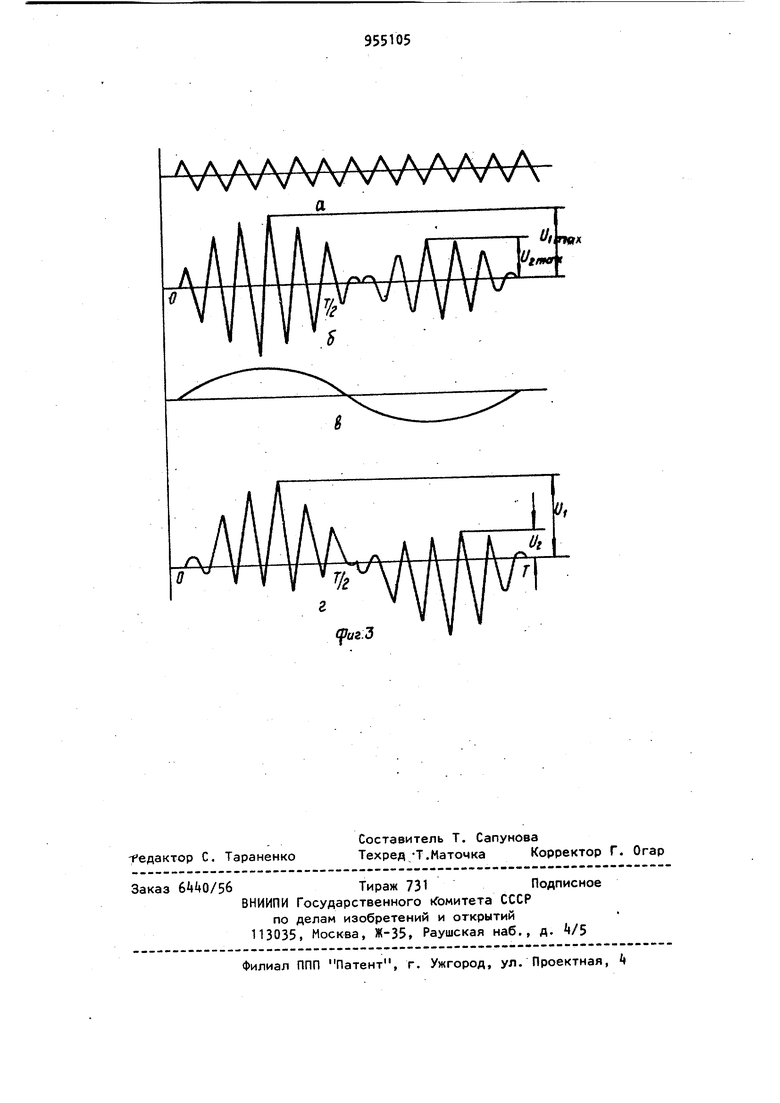

20 умножения с переменной крутизной, выход которого является выходом устройства; а первый и второй информационные входы блока умножения являются входами умножителя, четыре задающих потенциометре, первые кpaй ние выводы которых объединены и под ключены к шине положительного напряжения питания и к первому входу пи тания блока умножения с переменной крутизной,вторые крайние выводы перв го, второго и третьего задающих потен циометров объединены и подключены к шине отрицательного напряжения питания и к второму входу питания блока умножения с переменной крутизной, средний вывод первого задающего потенциометра подключен квыходу для балансировки первого информационного входа блока умножения с переменной крутизной, средний вывод второго задающего потенциометра подключен к выходу для балансировки пер вого информационного входа блока умножения с переменной крутизной, средний вывод третьего задающего потенциометра подключен, к выходу для балансировки напряжения сщемения выходного каскада блока умножен ия с переменной крутизной, сред ний вывод и второй крайний вывод че вepтo o задающего потенциометра объединены и подключены к выходу установки коэффициента перемножения блока умножения с переменной крутизной 2J . Недостатком умножителя является то, что из-за наличия временных и температурных дрейфов компенсирующих напряжений, потенциометров, параметров микросхем непосредственно перемножителя значение статической погрешности перемножения нестабильно во времени и в диапазоне температур, кроме того, процесс настройки носит итерационный характер, длителен и трудоемок. Цель изобретения - повышение точмости умножителя. Поставленная цель достигается тем, что в аналоговый умножитель переменных сигналов, содержащий блок умножения с переменной крутизной, выход которого является выходом умножителя, а первый и второй информационный входы являются соответственно первым и вторым выходами умножителя, три задающих потенциометра, первые крайние выводы которых объединены и подключены к шине положительного напряжения питания и к пер вому входу напряжения питания блока умножения с переменной крутизной, вторые крайние выводы первого и второго задающих потенциометров объединены и подключены к шине отм рицательного напряжения питания и к второму входу напряжения питания блока умножения с переменной крутизной, средний вывод первого задающего потенциометра подключен к выходу для балансировки второго информационного входа блока умножения с переменной крутизной, средний вывод второго задающего потенциометра подключен к выходу дла балансировки напряжения смещения выходного каскада блока умножения с переменной крутизной, средний вывод и второй крайний выход третьего задающего потенциометра объединены и подключены к выходу установки заданного коэффициента перемножения с переменной крутизной, введены ограничитель, выпрямительяый диод, два ключа, два зарядных конденсатора и дифференциальный усилитель, . выход которого подключен к выходу для балансировки первого информационного входа блока умножения с переменной крутизной, первый информационный вход блока умножения с переменной крутизной подключен к входу orpai ничителя прямой и инвертирующий выходы которого подключены к управляющим входам соответственно первого и второго ключа, информационные входы которых объединены и подключены к катоду выпрямительного диода, анод которого подключен к информационному выходу блока умножения с переменной крутизной,выходы ключей под, ключены к соответствующим входам дифференциального усилителя и через соответствующие зарядные конденсаторы подключены к шине нулевого потенциала . На фиг. 1 дана электрическая схема аналового умножителя переменных . сигналов; на фиг. 2 и 3 - эпюры нап ряжений, поясняющие его работу. Аналоговый умножитель переменных сигналов содержит блок 1 умножения с переменной крутизной, информационнЬ1е входы 2 и 3 которого являются соответственно входами умножителя, а информационный выход k является выходом умножителя, выход 5 для балансировки первого информационного входа блока умножения с переменной крутизной, выход 6 для балансировки второго информационного входа блока умножения с переменной крутизной, выход 7 для балансировки напряжения смещения выходного каскада блока умножения с переменной крутизной,вы 8 установки коэффициента перемножения блока умножения с переменной крутизной, первый вход 9 напряжения питания и второй вход 10 нап ряжения питания блока умножения с переменной крутизной, выпрямительный диод 11, ограничитель 12, ключи 13 и И, зарядные конденсаторы 15. и 16, дифференциальный усилитель 17 задающие потенциометры 18-20, шины отрицательного 21 и положительного 22 напряжений питания. Аналоговый умножитель переменных сигналов работает следующим образом Выхддное напряжение четырехквадрантных аналоговых умножителей сигналов определяется выражением UBbu oUxtJy €o &KU UL, + iKo + uK)exUi,4. )Uxey4Ko- k,ec,4lu,Uy),(i где Uy, Uu входные сигналы, подаваемые на информационные входы; CQ- эквивалентное напряжение смещения, характеризующее неравновесие выходного каскада; Д - составляющая выходного каскада, обусловленная отклонением коэффициента перемножения от номинального значения эквивалентные напряжения смещения, характеризующие неравновесие умножителя по выходам для балансировки информационных входов; f(U, Uy)-составляющая выходного напряжения, обусловленная нелинейной зависимостью коэффициента перемножения от сигналов U и Uu. Полезная составляющая в выходном напряжении описывается первым слагае мым в (1) . 1бых.п(м. f oUjffi/. Остальные составляющие выходного напряжения в (1) обуславливают погрешность перемножения. При обычно выполняющемся условии lexjeyJAlUx; Ujl .слагаемым (),|В (1) можно пренебречь из-за незначительности вноси мой погрешности, компенсация нелинейной составляющей, седьмое слагаесое в (1), как правило, не производи ся. Уменьшение погрешности перемножения умножителя достигается подачей четырех напряжений компенсации т зкой величины, чтобы-второе, третье, четвертое, и пятое слагаемое в выходном напряжении стали бы равными нулю. На информационные входы 2 и 3 блока 1 умножения с переменной крутизной подаются перемножаемые напряжения Ux (фиг. 2а) и . 26). В результате на выходе умножителя вырабатывается напряжение (фиг.2в). ;При этом для наглядности на фиг.2в в течение первого периода низкочастотного напряжения U показано выходное напряжение умножителя при отсутствии погрешностей, а в течение второго периода - при наличии смещения ех по входу X. На фиг. 2г представлено выходное напряжение умножителя после прохождения его через выпрямительный диод 11. На ограничитель 12 подается низкочастотное напряжение и. На выходах ограничителя . (фиг. 2д,е) формируются противофаз ыe прямоугольные напряжения, которые управляют ключами- 13 и 14. При открытом состоянии ключей зарядные конденсаторы 15 и 16 заряжаются до амплитудного значения напряжения U, при этом напряжения на упомянутых конденсаторах показаны на фиг. 2ж,з соответственно. Эти напряжения при-, кладываются к входам дифференциального усилителя 17,который и формирует компенсирующее напряжение U, прикладываемое к выходу 5 для балансировки первого информационного входа X. Под вЬздействием компенсирующего напряжения U изменяется смещение на выходе 5 блока 1 умноже ния, в результате чего амплитуды его выходного напряжения в течение соседних полупериодов низкочастотного перемножаемого напряжения выравниваются « т.е. погрешность перемножения сводится к нулю. Ввиду того-, что непосредственно в блоке умножения существует гальваническая связь между каскадами, то компенсирующее напряжение целесообразно подавать на выход для балансировки первого каскада блока умножения-. Как следует из (1) наибольшее влияние на точность перемножения оказывают четвертое и пятое слагаемые, так как при перемножении переменных сигналов при j( ,f tj 0 появляются новые спектральные составляющие с частотами перемножаемых наЛряжений. Второе слагаемое погрешности Е приводит лишь к добавлению постоянной составляющей в выходной сигнал ум-; ножителя, а третье слагаемое AKU,UO оказывает влияние на амплитуду выходного сигнала перемножителя, т.е. эти слагаемые не вносят дополнительных частотных искажений (дополнительных спектральных состав ляющих) в выходной сигнал АПС. На фиг. 2а,б изображены перемножаемые сигналы, на фиг. 2в представлен выходной сигнал умножителя при отсутствии статической погрешности. На фиг. За приведена составляющая погрешности, обусловленная напряжением смещения g по информационному входу X, на фиг. 36 - выходной .сигнал умножителя с учетом указанной выше погрешности, на фиг. Зв - состй ляющая погрешности, вызванная напря жением смещения ц по информационному входу у., на фиг. Зг - выходной си нал умножителя при наличии смещения на информационном входе У. При отсутствии напряжений смещений ,6 у фиг. 2в максимальные амплитуды выход ного напряжения умножителя в каждо полупериоде низкочастотного напряже ния равны. Как видно из фиг. напряжения смещения ,у-информацион ных входов X, У вызывают изменение максимального значения амплитуды вы ходного напряжения умножителя в течение каждого полупериода низкочас тотного перемножаемого напряжения Uj/. Это обстоятельство позволяет при появлении смещения на йнформационных входах х ,и автоматически сформировать компенсирующее напряжение такой величины, чтобы свести нулю составляющие погрешности выход ;ного напряжения, обусловленные напряжениями смещения В предлагаемом умножителе настро ка на минимальное значение статической погрешности происходит автоматически, режима разделения во вре мани не требуется, дополнительные тестовые напряжения также не нужны. Схема не критична к изменению параметров элементов, так как выходное напряжение умножителя через -ключи прикладывается как к зарядному конденсатору 15, так и к зарядному кон денсатору 1б через один и тот же выпрямительный диод 11, изменение емкостей конденсаторов 15 и 1б не оказывает заметного влияния, так как заряд их происхопйт до. амплитудного значения напряжения Ugy.,, при этом постоянная времени заряда ма;ла, а постоянная разряда обеспечивается достаточно большой ввиду высокого входного сопротивления усилителя 17 постоянного тока и большого сопротивления ключей 13 и 1 в .запертом состоянии. Экономический эффект от использования изобретения обусловлен его техническими особенностями, приведенными выше. Формула , изобретения Аналоговый умножитель переменных сигналов, содержащий, блок умножения с переменной крутизной, выход которого является выходом умножителя, а первый и второй информационные входы являются соответственно первым и вторым выходами умножителя, три задающих потенциометра, первые крайние выводы которых объединены и подключены к шине положительного напряжения питания и к первому входу напряжения питания блока умножения с переменной крутизной, вторые крайние выводы первого и второго задающего потенциометров объединены и . подключены к шине отрицательного напряжения питания и к второму входу напряжения питания блока умножения с Переменной крутизной, средний вывод первого задающего потенциометра подключен к выходу для балансировки второго информационного входа блока умножения с переменной крутизной, средний вывод второго задающего потенциометра подключен к выходу для балансировки напряжения смещения выходного каскада блока умножения с переменной крутизной, средний вывод и второй крайний вывод третьего задающего потенциометра объединены и подключены к выходу установки заданного коэффициента перемножения блока умножения с переменной крутизной, отличающийся тем, что, с целью повышения точности умножения, в него введены ограничитель, выпрямительный диод, два клюма, два зарядных конденсатора и дифференциальный усилитель, выход которого подключен к выходу для балансировки первого инфор-, мационного входа блока умножения с переменной.крутизной, первый информационный вход блока умножения с пере менной крутизной подключен к входу ограничителя, прямой и инвертирующий выходы которого подключены к управляющим входам соответственно первого и второго ключей, информационные входы которых объединены и подключены к катоду выпрямительного диода, анод которого подключен к информационному выходу блока умножения с переменной крутизной, выходы ключей подключены IK соответствующим входам дифференциального усилителя и через соответствующие зарядные конденсаторы подключены к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1.Тимрнтеев В. Н. и др. Устройство автоматической настройки четырехквадратных аналоговых перемножителей сигналов.- Измерительная техника,; 1978, № 10, с. 17, рис. 1.

2.Тимонтеев В. Н., Ткаченко В.А. Аналоговый перемножитель сигналов К525ПС1.- Электронная промышленность, Vf 7, с. 10-13 (прототип). ЛЛл лЛЛ

С Ж U(i}((}i U,f(f}-U ii ti Uf 4rUK(Jy svV «J i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перемножения сигналов переменного тока | 1982 |

|

SU1037277A1 |

| Устройство для настройки аналоговых умножителей напряжений | 1975 |

|

SU618748A1 |

| Перемножитель электрических сигналов | 1991 |

|

SU1836694A3 |

| Четырехквадратный умножитель | 1981 |

|

SU978160A1 |

| Функциональный преобразователь | 1974 |

|

SU598092A1 |

| Устройство для настройки аналоговых умножителей напряжений | 1978 |

|

SU742963A1 |

| Множительное устройство | 1980 |

|

SU926673A1 |

| Аналоговый умножитель | 1980 |

|

SU945871A1 |

| Четырехквадрантный умножитель | 1988 |

|

SU1594522A2 |

| Четырехквадрантный умножитель сигналов постоянного тока | 1981 |

|

SU980104A1 |

и

(риг.1

гт

V/ sAA/A /AV

Авторы

Даты

1982-08-30—Публикация

1981-02-05—Подача