1 (61) 978160

(21)4492144/24-24

(22)10.10.88

(46) 23.09.90. Бюло № 35

(71)Омский политехнический институт и Томский политехнический институт им, С.М.Кирова

(72)В.А.Пятибратов и Д.Г.Бурмантов

(53)681.335 (088.8)

(56)Авторское свидетельство СССР № 978160, кл. G 06 G 7/16, 1981.

(54)ЧЕТЫРЕХКВДЦРАНТНЫЙ УМНОЖИТЕЛЬ

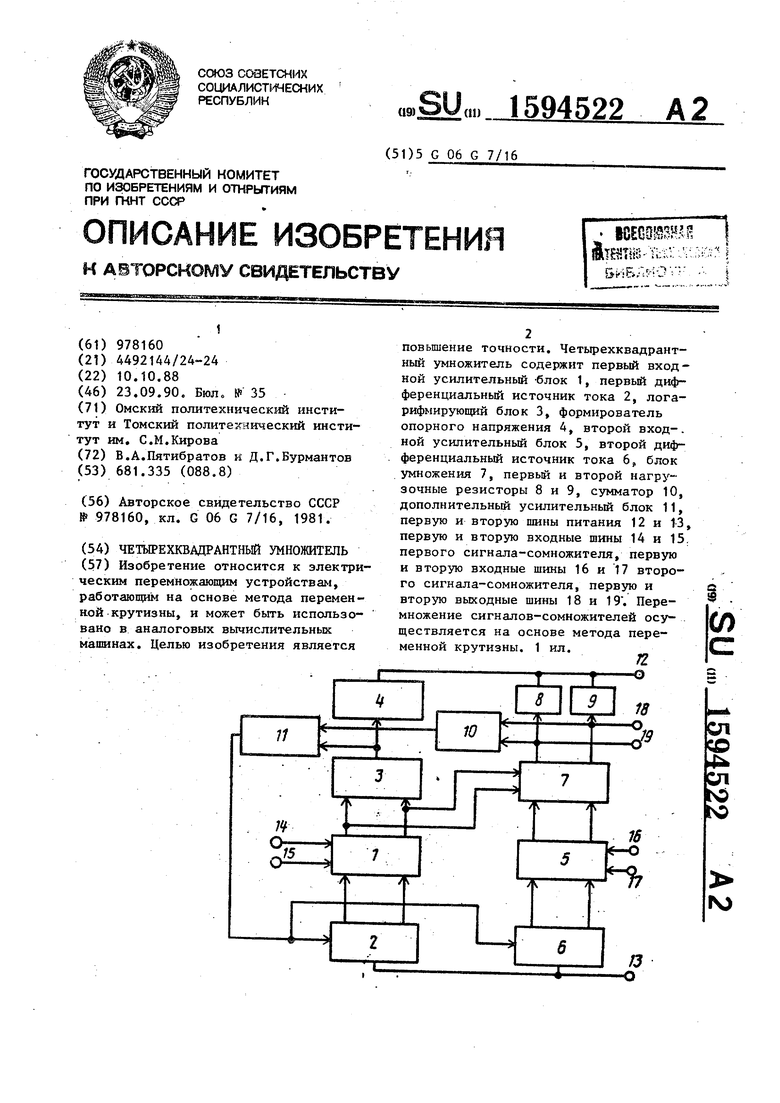

(57)Изобретение относится к электрическим перемножающим устройствам, работающим на основе метода переменной крутизны, и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является

повышение точности. Четьфехквадрант- ный умножитель содержит первый вход- нон усилительный -блок 1, первый дифференциальный источник тока 2, логарифмирующий блок 3, формирователь опорного напряжения 4, второй вход-, ной усилительный блок 5, второй дифференциальный источник тока 6, блок .умножения 7, первый и второй нагрузочные резисторы 8 и 9, сумматор 10, дополнительный усилительный блок 11, первую и вторую шины питания 12 и 13, первую и вторую входные шины 14 и 15. первого сигнала-сомножителя, первую и вторую входные шины 16 и 17 второго сигнала-сомножителя, первую и вторую выходные шины 18 и 19. Перемножение сигналов-сомножителей осуществляется на основе метода переменной крутизны. 1 ил.

К

(Л

31

Изобретение относится к электри - ческнм перемножакшщм устройствам, работающим на основе метода перемер ной крутизны, может быть использова но в аналоговых вычислительных машинах и является усовершенстнованием умножителя по авт„св,.№ 978160.

Целью изобретения является повышение точности.

На чертеже изобрал ена функциональ НЭ.Я схема четырехквадрантного умножк- 1геля,

Схема содержит первый входной усилительный блок 1, первый диф4зе

ренциальньй источник 2 тока, лога- )Ифмирующий блок 3 s формирователь 4 | порного напряжения, второй входной усилительньй блок 5, второй диффе- («енциальный источник 6 тока, блок 7 Умножения, первый 8 и второй 9 нагру ючные резисторы, сумматор 10, до- олиительньй усилительный блок 11, jiapByro 12 и вторую 13 шины питания первую 14 и вторую 15 входные шины jiepBoro сигнала-сомнож11теля, первую 6 и вторую 17 входные шилы второго |;игнала-сомножителя, первую 18 и вторую 19 выходные шины, ; Первый 1 и второй 5 усшштельные блоки выполняют функцию ди фферен17,я- ального преобразователя напряжения t3 ток, выполнены одинаково и кааодый: из них представляет собой дифферен- Циалы-гую пару биполярные: транзисторов, базы которых являются входами. ; Эмиттеры транзисторов, соединенны между собой масштабиру ощга.1 резистором,, являются таковы№-1 вх одами. Коллекторы транзисторов-, образу от Дифференциальный выход,

Каждьц из источников 2 и б тока выполнен на двух идентичных управ- |1яемых генераторов тока, каждый из которых построен на основе биполяр™ пого транзистора, эмиттер которого соедш1ен с масштабир аощим резистором Выводы резисторов соединены между собой и являются входом источника тока. Баз Л транзисторов соединены между собой и образуют управляющий вход. Коллекторы транзисторов являются вьпсодами

Логарифмирующий блок 3 может быть выполнен на .основе двух р-п-перехо- дов, например двух диодов,, первые одноименные электроды которых под- KJmчeны к первому выводу балластного резистора, второй вывод которого

4

0

50

5

0

5

0

5

0

5

является выходом логарифмирующего блока, вторые электроды диодов являются входами логарифмирующего блока.

Блок 7 умнолсения может быть вы-, полнен на двух дифференциальных парах биполярных транзисторов с объединенными эмиттерами. Объединенные эмиттеры являются линейными входами. База первого транзистора первой пары соединена с базой второго транзистора второй пары, а база второго транзистора первой пары соединена с базой первого транзистора второй пары. Соединенные базы являются нелинейными входами. Соединение между собой коллектора первых транзисторов первой и второй пары и соединенные между собой коллекторы вторых транзисторов являются соответсткенно первым и вторым выходами блока умножения.

Формирователь опорного напряже о- ния может быть выполнен например, на стабилитроне шти в виде резистора.

Четырехквадрантный умножитель работает следующим- образом,

Напрянсение первого си гнал а-сомножителя, действующее между входными, ш-шами 14 и 15J преобразуется в разность токов на nejjBOM и втором выхо дах первого входного усилительного - блока 1 г. -

Этот сигнал преобразуется в логарифмирующем блоке 3 в напряжение.- Напряжение сигнала с логарифмируйще- го каскада 3 поступает на первый и второй нелинейные входы блока 7 умножения. На первый и второй линейные входы блока 7 -умножения с. выходов второго входного усилительного блока 5 поступает второй сигнал-сомножитель.-

Произведение первого и второго си гнало в-сомножителей представляет- ся в ввде разности токов на первом и втором выходах блока 7 умножения, которая далее преобразуется с помощью первого 8 и второго 9 нагрузочных резисторов в дифференциальное напряжение на первой 18 и второй 19 выходных шинах.,

Начальный уровень токов, поступающих на первьй 1 и второй 5 входные усилительные блоки, формируется первьм 2 и вторьм б диф(|)еренциальны- мн источниками тока, стабильность токов которьк определяет стабильность. коэффициента перемножения.

51

Характерньм свойством является то, что суммарный выходной ток блока 7 умножения, протекающий по первому 8 и .второму 9 нагру8очнь&1 резне- торам, не зависит от произвёд екия сигналов-сомножителей Это свойство позволяет осуществить стабздлизацию тока первого 2 и второго 6 дифференциальных источников тока по суммарному току первого В и второго 9 нагрузочных резисторов. Использование, .сумматора 10 позволяет получить напряжение между его выходом и первой шиной 12 питания пропорцио- нальное сумме выходных токов блока 7 умножения, и в силу идентичности первого 8 и второго 9 нагрузочных резисторов, не зависимое от разности этих токов.

. Выходной сигнал сумматора 10 сравнивается с опорным напряжением с помощью дополнительного усушительно- го блока 115 на выходе которого вырабатывается сигнал управления пер- вым 2 и вторым 6 дифференциальными источниками тока, обеспечивая заданный уровень тока.

2

Таким образом, в четьфехквадрант- ном умножителе влияние изменения питающих напряжений и температуры окружающей среды на коэффициент перемно™ жения значительно ослаблено.

Формула изобретения

Четырехквадрантный умножитель по авт.св. Н 978160, отличающийся тем, что, с целью повышения точности, в него введены сумматор и дополнительный усилительный блок, а первый и второй дифференциальные источники тока выполнены управляющими, причем первый и второй входы сумматора подключены соответственно к первому и второму выходам умножителя, выход сумматора соединен с первым, входом дополнительного усилительного блока, к второму входу которого подключен выход формирователя опорного напряжения, выход дополнительного усилительного блока подключен к управляющим входам первого и второго дифференциальных источни -- ков тока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехквадратный умножитель | 1981 |

|

SU978160A1 |

| Аналоговый четырехквадрантный умножитель | 1982 |

|

SU1024939A1 |

| Аналоговое перемножающее устройство | 1988 |

|

SU1654841A1 |

| Аналоговое перемножающее устройство | 1984 |

|

SU1218401A1 |

| Аналоговый умножитель | 1978 |

|

SU742965A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Аналоговый перемножитель | 1989 |

|

SU1709353A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Балансный модулятор | 1980 |

|

SU907765A1 |

Изобретение относится к электрическим перемножающим устройствам, работающим на основе метода переменной крутизны, и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Четырехквадратный умножитель содержит первый входной усилительный блок 1, первый дифференциальный источник тока 2, логарифмирующий блок 3, формирователь опорного напряжения 4, второй входной усилительный блок 5, второй дифференциальный источник тока 6, блок умножения 7, первый и второй нагрузочные резисторы 8 и 9, сумматор 10, дополнительный усилительный блок 11, первую и вторую шины питания 12 и 13, первую и вторую входные шины 14 и 15 первого сигнала - сомножителя, первую и вторую входные шины 16 и 17 второго сигнала - сомножителя, первую и вторую выходные шины 18 и 19. Перемножение сигналов-сомножителей осуществляется на основе метода переменной крутизны. 1 ил.

Авторы

Даты

1990-09-23—Публикация

1988-10-10—Подача