.., - .

Изобретение относится к телемет РИМ и может быть использовано для передачи непрерывныхссообщений в системах связи.

Известно устройство для передачи разностных сигналов, содержащее анализатор знака, преобразователь аналог-код, сумматор, формирователь выходных сигналов, синхронизатор, коммутатор, элемент ИЛИ, элемент задержки и управляющий блок. Устройство позволяет передавать сигналы приращения таким образом, что при передаче одинаковых посылок как на передающей, так и на приемнойт . стороне вес i-и посылки удваивается по сравнению с весом (|-1)-й посылки того же знака, а после смены знака (качества) посылки вес посылки начинается с 1 ; tl .

Недостатком устройства является относительно большая дисперсия ошибки перегрузки (динамической ошибки).

Известно также устройство для передачи сигналов приращения, которое содержит преобразователь аналог код, блок вычитания, сумматор, формирователь сигналов, синхронизатор, триггер, матричный коммутатор, блок задержки, блок сравнения. Устройство, измеряя разность Л между входным цифровым и восстановленным кван,0 тованным Л |i сигналами, определяет знак разности (, - или О), а также определяет, когда разность л меньше удвоенного значения дель- . та-сигнала, Поступившего в сумматор

)5 в предыду1цей тактовой точке, В момен ты t, когда или А А меныие удвоенного веса предыдущей дельта-посылки, в канал связи посылается сигнал О, При других соотношениях передаются положительные или отрицатель ныё весовые посылки С2,

Устройство удовлетворительно работает .только при передаче медленно меняющихся процессов.

Наиболее близким по технической сущности к предлагаемому является устройство для передачи информации, содержащее генератор синхросигналов, преобразователь аналог - цифра, сумматор, анализатор знака, формирователь сигналов, матричный коммутатор, реверсивный счетчик, логический переключатель, выходы преобразователя аналог - цифра соединены с первым входом анализатора знака, вторые входы которого соединены с выходами сумматора, три выхода анализатора знака соединены с выходами логического переключателя, из них два выхода соединены также со входами формирователя сигналов и первыми входами матричного коммутатора, выходы которого соединены с сумматором, вторые входы подключены к выходам реверсивного счетчика, входы которого соединены с выходами логического переключателя, генератор синхросигналов подключен к управляющим входам преобразователя аналог - цифра, сумматора, матричного коммутатора и реверсивного счетчика. В этом устройстве логический переключатель выполнен на элементах ИЛИ, триггерах элементах ЗАПРЕТ.

В устройстве в момент ti сравниваются цифровой сигнал A.u,/() и восстановленный в сумматоре сигнал u,{t)-) и вырабатывается сигнал + t4(ti) u,((, ГЛ {t, 0, (t)0 .Если в процессе передами скачка функции Лц (tj) , .с помощью дельта-сигналов, нарастающих по двоичному закону, в момент t величина Ag,() оказывается больше величиныЛц(t), то с тактовой точки начинают передаваться дельта-посылки противоположного знака с убыванием веса по сравнению с посылкой противоположного знака, переданной в точке t:). Например, скачок величиной 10 передается в виде следующих сигналов:

10 1+2+4+8-t-2+1 З.

Недостатком устройства является относительно невысокая точность изза большой дисперсии ошибки на участках медленного изменения передаваемых функций.

Цель изобретения - повышение точности устройства за счет обеспечениямалой дисперсии ошибок перегрузки как для быстрых, так и для медленно

изменяюц ихся передаваемых параметров, а также получение энергетического выигрыша.

Поставленная цель достигается тем,

что в устройство для передачи сигналов приращений, содержащее генератор синхросигналов, выход которого соединен с управляющими входами блока- определения знака приращений и

аналого-цифрового преобразователя, информационный вход которого соединен со входом устройства, выходы аналого-цифрового преобразователя сое- , диненыг.с первыми информационными

5 входами блока определения знака приращений, вторые информационные входы которого соединены с выходами сумматора, первый выход блока о.преде- ления знака приращений- соединен с

первым входом логического переключателя , второй выход - с вторым входом логического переключателя и первым входом коммутатора, третий выход с третьим входом логического переключателя и вторым входом коммутатора, выходы которого соединены с первыми входами сумматора, первый второй и третий выходы логического переключателя соединены с первыми входами ре- версивного счетчика, выходы которого соединены с третьими входами ком.мутатора и формирователь выходных .сигналов, выход которого соединен с выходом устройства, введен элемент задержки, вход которого подключен к выходу генератора синхросигналов, выход элемента задержки соединен с первым входом формирователя -выходных сигналов, вторыми входами сумматора и реверсивного счетчика и четвертым входом коммутатора, четвертый и пятый выходы блока определения знака приращений соединены сооТ(Ветственно с четвертым- и пятым входами логического переключателя, четвертый и пять1й выходы которого соединены с вторым и третьим входами формирователя выходных сигналов. Логический переключатель выполнен на элементах И, ИЛИ и триггерах, выход

0 первого элемента ИЛИ соединен с

первыми входами второго элемента ИЛИ и первого триггера, второй вход которого соединен с выходом третьего элемента ИЛИ, выход второго элемента ИЛИ

5 соединен с первым входом второго

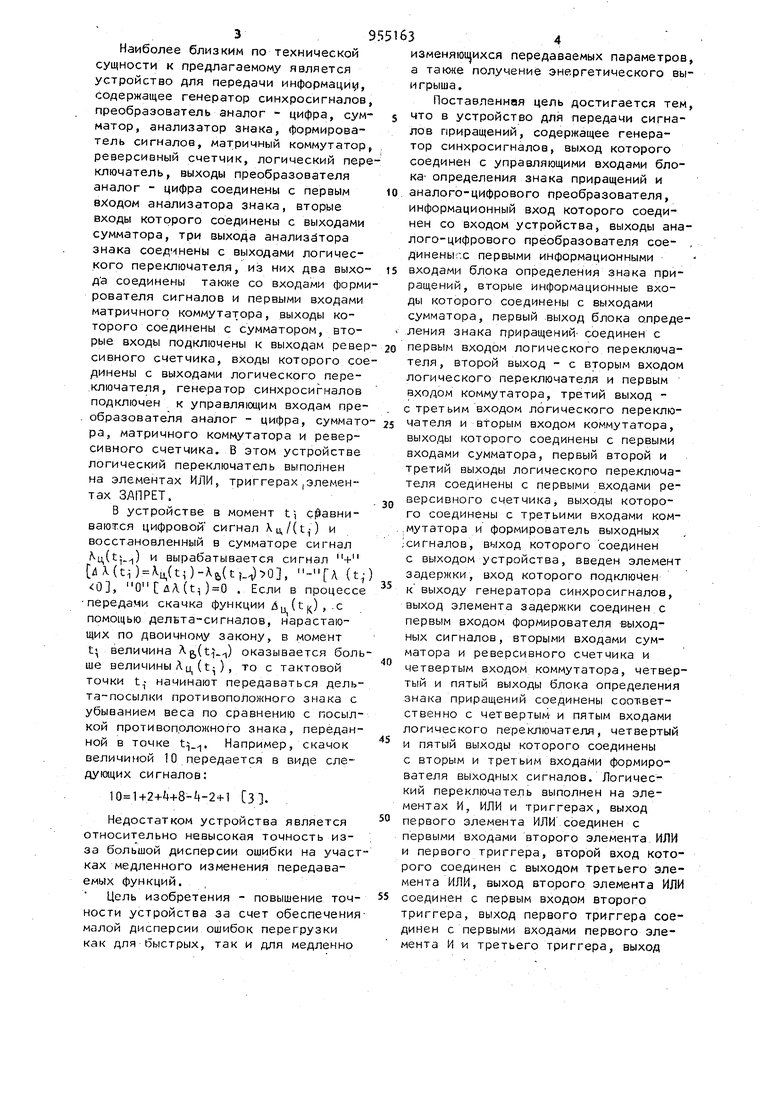

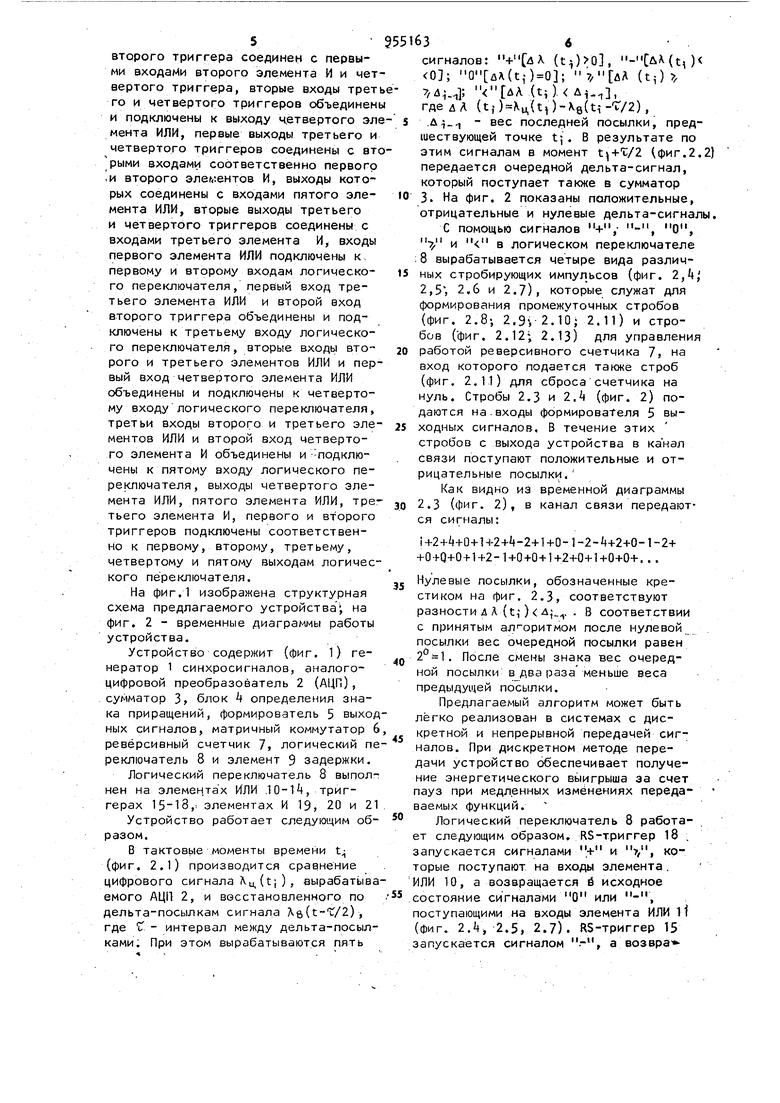

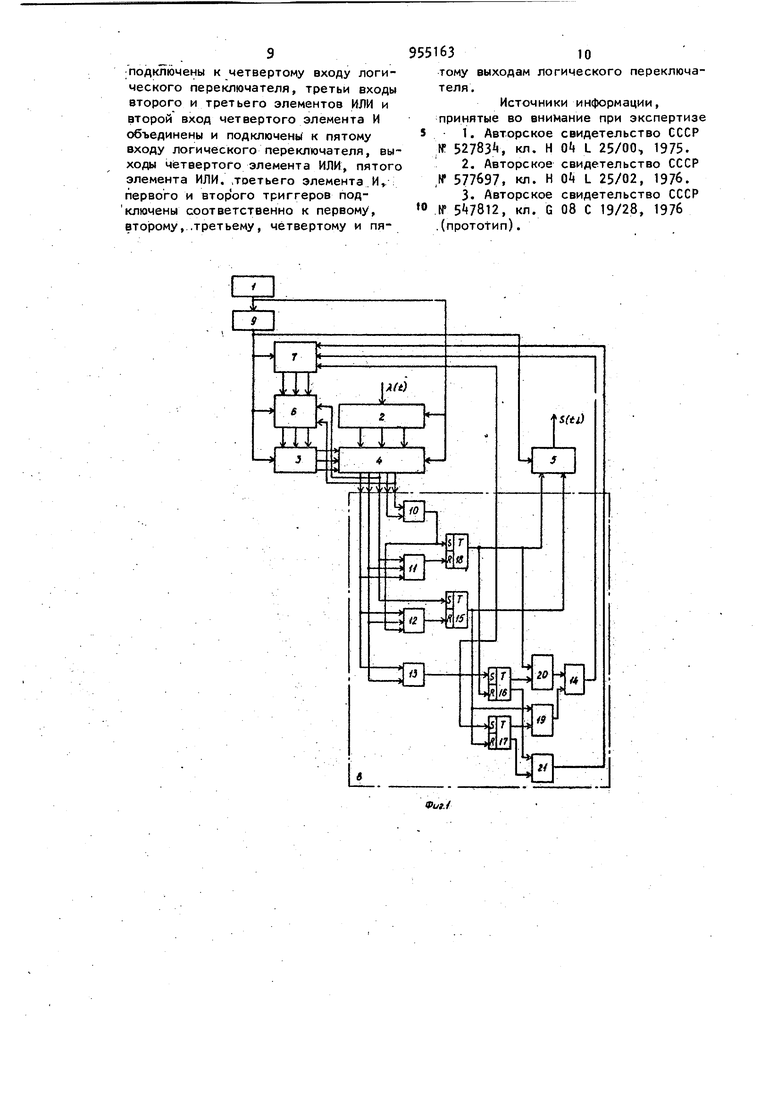

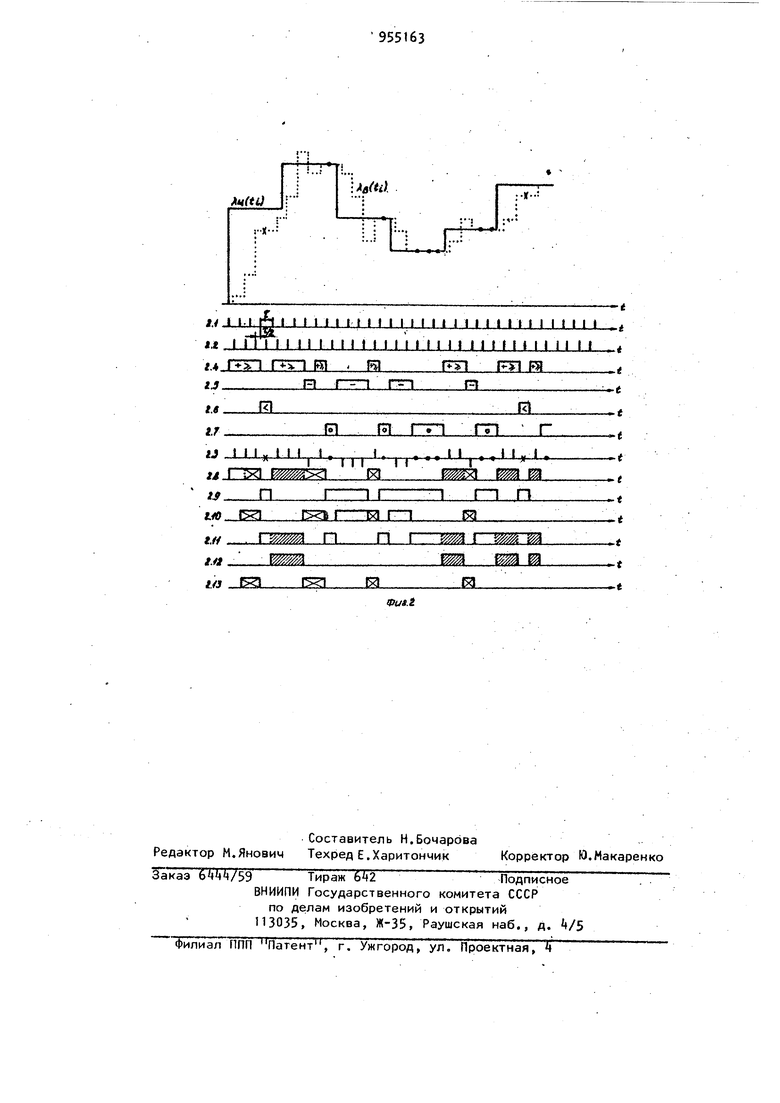

триггера, выход первого триггера соединен с первыми входами первого элемента И -и третьего триггера, выход второго триггера соединен с первыми входами второго элемента И и чет вертого триггера, вторые входы трет го и четвертого триггеров об-ьединен и подключены к выходу четвертого эл мента ИЛИ, первые выходы третьего и четвертого триггеров соединены с вт рыми входами соответственно первого ,и второго эле(ентов И, выходы которых соединены с входами пятого элемента ИЛИ, вторые выходы третьего и четвертого триггеров соединены с входами третьего элемента И, входы первого элемента ИЛИ подключены к первому и второму входам логического переключателя, первый вход третьего элемента ИЛИ и второй вход второго триггера объединены и подключены к третьему входу логического переключателя, вторые входь вто рого и третьего элементов ИЛИ и пер вый вход четвертого элемента ИЛИ объединены и подключены к четвертому входу логического переключателя, третьи входы второго и третьего эле ментов ИЛИ и второй вход четвертого элемента И объединены и --подключены к пятому входу логического переключателя, выходы четвертого элемента ИЛИ, пятого элемента ИЛИ, тре тьего элемента И, первого и второго триггеров подключены соответственно к первому, второму, третьему, четвертому и пятому выходам логичес кого переключателя. На фиг,1 изображена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы устройства. Устройство содержит (фиг. 1) генератор 1 синхросигналов, аналогоцифровой преобразователь 2 (АЦП), сумматор 3 блок 4 определения знака приращений, формирователь 5 выход ных сигналов, матричный коммутатор 6 реверсивный счетчик 7, логический пе реключатель 8 и элемент 9 задержки. Логический переключатель 8 выполнен на элемен.тах ИЛИ .10-1, триггерах 15-18,. элементах И 19, 20 и 2 Устройство работает следующим образом. В TaKTOBbie моменты времени t (фиг, 2.1) производится сравнение цифрового сигнала Лц(t;), вырабатыва емого АЦП 2, и восстановленного по дельта-посылкам сигнала As(t-L/2), интервал между дельта-посылками. При этом вырабатываются пять сигналов: X (t;5)0, (t,) (t,-) 7,йА (t,-) , 7/di.; лА (tj. Д.З, где дл (t)ц(t)(), .uj; - вес последней посылки, предшествующей точке t;. В результате по этим сигналам в момент t +i;/2 1фиг.2.2) передается очередной дельта-сигнал, который поступает также в сумматор 3. На фиг. 2 показаны положительные, отрицательные и нулевые дельта-сигналы. С помощью сигналов + llntl t , И в логическом переключателе 8 вырабатывается четыре вида различных стробирующих импульсов (фиг. 2,, 2,5, 2,6 и 2.7), которые служат для формирования промежуточных стробов (фиг. 2.8-, 2.Э, 2.10; 2.11) и стробов (фиг. 2.12; 2.13) для управления работой реверсивного счетчика 1, на вход которого подается также строб (фиг. 2.11) для сброса счетчика на нуль. Стробы 2.3 и 2,k (фиг. 2) подаются на.входы формирователя 5 выходных сигналов. В течение этих стробов с выхода устройства в канал связи поступают положительные и отрицательные посылки. Как видно из временной диаграммы 2.3 (фиг. 2), в канал связи передаются сигналы: i-f2+ +0+l-i-2+t-2+1+0-1-2-it+2+0-l-2+ +0+0+0+1+2-1+0+0+1+2+0+1+0+0+... Нулевые посылки, обозначенные крестиком на фиг. 2.3, соответствуют разности д Л (t; ) д, . В соответствии с принятым ал оритмом после нулевой посылки вес очередной посылки равен . После смены знака вес очередной посылки в двараза меньше веса предыдущей посылки. Предлагаемый алгоритм может быть легко реализован в системах с дискретной и непрерывной передачей сигналов. При дискретном методе передачи устройство обеспечивает получение энергетического вь1игрыша за счет ауз при медленных изменениях передаваемых функций. Логический переключатель 8 работат следующим образом RS-триггер 18 . апускается сигналами и ,, коорые поступают на входы элемента . ЛИ 10, а возвращается и исходное остояние сигналами О или -, оступающими на входы элемента ИЛИ it (фиг 2.it, 2.5, 2.7). RS-триггер 15 апускается сигналом .-, а возвра - . щается в исходное состояние сигналами О, Ч, -«- и которые посту пают на его вход с выхода элемента ИЛИ 12 (фиг, Z., 2.5 2.6, 2.7), RS-триггер 16 запускается сигналами, поступающими с выхода элемента ИЛИ 1 возвращается в исходное состояние сигналами, поступающими с выхода триггера 18 (фиг. 2.8, 2,9). Я$-триг тер 17.вырабатывает стробы 2.10 и 2.11 (фиг. 2). С помощью элементов И 20 и 19 и выходного элемента ИЛИ 1 вырабатываются стробы 2.12 (фиг..2), в течение которых в реверсивном счет чике 7 происходит сложение. . На выходе элемента И 21 получаются стробы (фиг. 2.13), в течение которых в счетчике.7 происходит вычи тание (каждый импульс, поступивший в счетчик 7 в течение данного строба, уменьшает записанное число на ед ницу). Таким образом, предлагаемое устройство за счет адаптации к входной, передаваемой функции позволяет-умень шить дисперсию ошибки перегрузки как для быстро меняющихся, так и для медленно меняющихся функций, т.е. повышается точность устройства. Кроме того, устройство обеспечивает получение энергетического выигрЬша. Формула изобретения 1. Устройство для передачи сигналов приращений, содержащее генератор синхросигналов, выход которого соединен с управляющими входами блока определения знака приращений и аналого-цифрового преобразователя, информационный вход которого соединен с входом устройства, выходы аналого-цифрового преобразователя соединены с первыми информационными входами блока определения знака приращений, вторые информационные входы которого соединены с выходами сумматора, первый выход блока определения знака приращений соединен с первым входом логического переключателя, второй выход - с вторым входом логического переключателя и первым входом коммутатора, третий выход - С третьим входом логического переключателя и вторым входом коммутатора, выходы которого соединены с первыми входами сумматора, первый, второй и третий выходы логического пере38 , V ключателя соединены с первыми вхо-N дами реверсивного счетчика, выходы которого соединены с третьими входами коммутатора, и формирователь выходных сигналов, выход которого соединен с выходом устройства, отличающееся тем, что, с целью повышения точности устройства, в него введен элемент задержки, вход которого подключен к выходу генератора синхросигналов, выход элемента задержки соединен с первым входом формирователя выходных сигналов, вторыми входами сумматора и реверсивного счетчика и четвертым входом коммутатора, четвертый и пятый выхоДы блока определения знака приращений соединены соответственно с четвертым и пятым входами логического переключателя, четвертый и пятый выходы которого соединены с вторым и третьим входами формирователя выходных си1- налов. 2. Устройство по п. 1, от ли чающееся тем, что логический переключатель выполнен на элементах И, ИЛИ и триггерах, выход первого элемента ИЛИ соединен с первыми входами второго элемента ИЛИ и первого триггера, второй вход которого соединен с выходом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом второго триггера, выход первого триггера соединён с первыми входами первого элемента И и третьего триггера, выход второго триггера соединен с первыми входами второго элемента И и четвертого триггера, вторые входы третьего и ч этвертого триггеров объединены и подключены к выходу четвертого элемента ИЛИ, первые выходы третьего и четвертого триггеров соединены с вторыми входами соответственно (первого и второго элементов И, выходы которых соедпнены с входами пятого элемента ИЛИ, вторые выходы третьего и четвертого триггеров соединены с входами третьего элемента И , входы первого элемента ИЛИ подключены к первому и второму входам логического переключателя, первый вход третьего элемеи. та Или и второй вход второго триггера обгединены и подключены к тре- , тьему входу логического переключателя, вторые входы второго и третьето элементов ИЛИ и первый вход четвертого элемента ИЛИ объединены и .

;подключены к четвертому входу логического переключателя, третьи входы второго и третьего элементов ИЛИ и второй вход четвертого элемента И объединены и подключены к пятому входу логического переключателя, выходы четвертого элемента ИЛИ, пятого элемента ИЛИ. .тоетьего элемента.И первого и второго триггеров подключены соответственно к первому, вто|эому, .третьему, четвертому и пятому выходам логического переключателя.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 52783S . Н О L 25/00, 1975.

2.Авторское свидетельство СССР ,№ 577697, кл. Н Oil L 25/02, 1976.

3.Авторское свидетельство СССР If 547812, кл. G 08 С 19/28, 1976

.(прототип).

Mtti

(td

.K..:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сигналов приращений | 1981 |

|

SU955162A1 |

| Устройство для передачи сигналов приращений с предсказанием | 1978 |

|

SU765857A1 |

| Устройство для передачи сигналов приращений | 1976 |

|

SU601736A1 |

| Устройство для передачи сигналов приращений с предсказанием | 1977 |

|

SU705496A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Устройство для передачи сигналов приращений с предсказанием | 1982 |

|

SU1089605A2 |

| Устройство для решения игровых задач на вычислительных сетях | 1982 |

|

SU1104522A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Устройство для передачи информации | 1975 |

|

SU547812A1 |

Hi I.I ri I I I 1 II li I Ml iM t j 1 I IJ lit

1Д I JTt I I t I I I M t 1 I I I n I M J I t M t I I i I t I

f. 1 t I РП tjJ3

т

PI m m

I I

iXl

XL

/.

g

n П r

y/ . 1 /.«МЖ

J5

г/j g.

t I 1

РП Fn РЯ

JEL

ш

-«

.r.

11

TT

- e

1 rn П

Ш 1 ж%г т

-f

ja

Авторы

Даты

1982-08-30—Публикация

1981-01-05—Подача