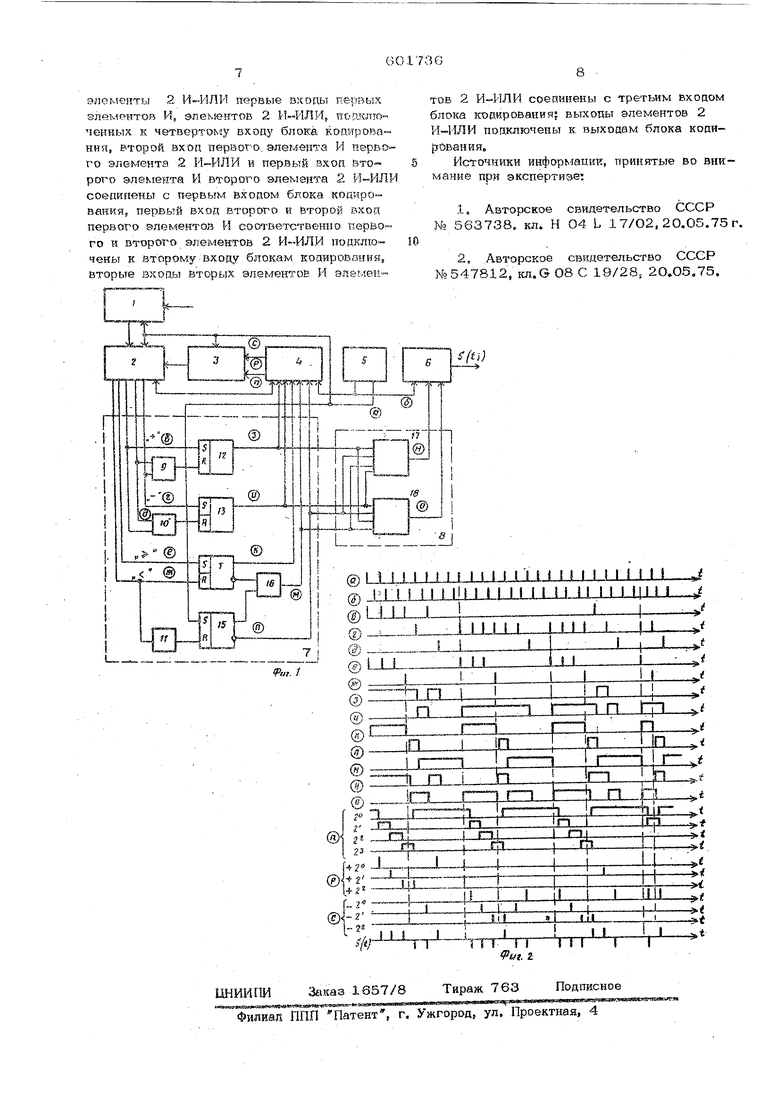

вортый и пятый входы KOTOpoio подключены к сйотиетств5 ющик: выходам анализатора знака л разности, выходы логического переключатели соединены со входами матричного коммутатора. Логический переключатель содержит , элe ieнты И, ИЛИ, триггеры и элемент задержки, выход которого соединен с 8 - вхо дом первого триггера, прямой выход первого и инверсный выход второго триггеров подключень ко входам элекюнта И, выходы элементов ИЛИ подключены соответственно К9 входам третьего и четвертого триггеров вход элеменч а задержки и Т - вход третье о триггера соединены :С первым входом логи ческого 1гереключателя, S -вход второготри гера подключен ко второму входу логического переключателя, S -вход . четвертого триггера ипервый вход первого элемента ИЛИ соединен с третьиь входом логичес кого переключателя, второй вход первого и первый вход второго элементов ИЛИ подключен к четвертому входу логического переключателя, второй вход второго элемента ИЛИ и S -вход третьего триггера подключен к пятому входу логического пере ключателя, 5- вход первого триггера соединен с-синхронизирующим входом логического переключателя, j инверсный выход первого триггера, выход элемента И, прямой выход второго и выход третьего и четвертого триггеров подключены соответственно к первому, второму, пятому, третьему и четвертому выходу матричного коммутатора. Блок кодирования содержит элементы 2 И-ИЛИ первые входы первьгх элементов И элементов 2 И-ИЛИ подключены к четвертому входу блока кoдиpoвaн rя, второй вход первого элемента И первого элемента 2И-ИЛИ и первый вход второго элемента И второго элемента 2 И-ИЛИ соединены с первым входом блока кодирования, первый вход которого и второй вход первого элементов И соответственно первого и второго элемен тов 2 И-ИЛИ подкиючены ко второму вх:оду блока кодирования, вторые входы вторы элементов И элементов 2 И-ИЛИ соединены с третьим входом блока кодирования; выход элементов 2 И-ИЛИ подключены к выходам блока. На фиг. 1 приведена функциональная электрическая схема устройства, которая со держит аналого-цифровой преобразователь 1 анализатор знака и разности 2, сумматор 3 матричныйкоммутатор 4, генератор cvuixpo- импульсов 5, формирователь сигналов 6, ло гический переключатель 7, блок- кодирования 8, второй элемент ИЛИ 9, первый элемент ИЛИ 10, элемент задержки 11,. четвертый триггер 12, третий триггер 13, второй триггер 14, первый триггер 15, элемент И 16. первый элемент 2 И-ИЛИ 17, второй элемент 2 И-ИЛИ 18. На фиг. 2 приведены временные диаграммы работы устройства. Устройство работает следующим обрасзом.Сообщение Л (с) с помощью аналого-цифрового преобразователя 1 преобразуется в параллельный двоичный код, Л ц ()i который подается на первую группу входов анализатора знака , и разности 2, на вторую группу входов которого поступает в сю становленное сообц (fc i ) в виде параллельного щение Л двоичного кода, из матричного коммутатора 4 подается опорный сигнал ДЛц(.). В результате сравнения значений ДАц(i ) и Д и, (t,-.) в анализаторе знака и разности 2 вырабатываются сигналы +, если дХц Ui) Q ,-, еслидЛц (i) О , и о если дД.„1Т,-; и, п также сигнал , если AAui (ti)2&A(t,-.X , еслкДЛц(,-) 2лл(t.).Сигналы + подаются-на вход 5 первого триггера 12 и на второй вход первого элемента ИЛИ 10, сигналы - подаются на вход S третьего триггера 13 и второй вход второго элемента ИЛИ 9, сигналы о подаются на первые входы второго элемента ИЛИ 9 и первого элемента ИЛИ 1О. Выход второго элемента ИЛИ 9 соединен со входом Т четвертого триггера 12, выход первого элемента ИЛИ 10 соединен со входом R третьего триггера 13. Сигнал подают на вход S второго триггера 14, - подают на вход второго триггера 14 и на вход элемента задержки 11, длительность задержки Л. t выбирается из условия.,25 выход элемента задержки соединяется со входом R первого триггера 15. На вход S четвертого триггера 15 подаются тактовые импульсы с частотой На выходе четвертого триггера 12 получается строб + фиг. 2,з) иа выходе, третьего триггера 13 получается строб -, на выходе второго триггера 14 получается строб (фиг, 2,к.), на инверсном выходе первого триггера 15 получится строб (фиг.2,л)., Выход первого триггера 15 и инверсный выход второго триггера 14 подетючены к первому и второму входам элемента И 16, на выходе которой получается строб (фиг,2,м). Полученные в логическом переключателе 7 стробы подаются на входы матричного коммутатора 4, где вырабатываются значения разностей в моменты времени (.2,с,р) н опорный сигнал л А ц ft-) (.2,п) для управления работой анализатора знака и разности 2, Значения разностей подаются в сумматор 3, где получается восстановленный сигнал А ц (t ). Одновременно стробы +; , 5 ; и строб (фнг,2,м.) подаются в коаирования 8 для выработки сигналов, управляющих работой формирователя сигналов 6. Строб + подается на первые входы первых элементов и первого, и второго элемента 2 И-ИЛИ 17 и 18, На вторые входы второго элемента И первого элемента 2 И-ИЛИ и второго элемента И второго элемента 2 И-ИЛИ 18 подается строб -. На второй вход элемента И первого элемента 2 И-ИЛ 17 и второго элемента И второго элемента 2 И-ИЛИ 18 подается строб -. На второй вход элемента И-первого элемента 2 И-ИЛИ 17первый вход второго элемента И второг элемента 2 И-ИЛИ 18 подается строб . Hfi первый вход второго элемента И первого элемента 2 И-ИЛИ 17 и второй вход первого элемента И второго эле г;нта 2 И-ИЛИ 18подается строб (фиг.2,и). На выходе первого элемента 2 И-ИЛИ 17 получается строб (фиг. 2,н .) на выходе второго элемен та 2 И-ИЛИ 18 получается строб (фиг.21о). Для работы матричного коммутатора 4 и фор , мйрователя 6 в генераторе синхроимпульсов 5 формируются синхроик;пульсы, задержанны относительно импульсов опроса (фиг.) на величину- чр j ,(фиг, 2,6),, Формирователь сигналов 6 вырабатывает сигналы S (t,), (фиг.2),. задержа-гшые относительно импульсов опроса на - . Импульсы опроса (фиг.) с выхода генератора синхроимпульса 5 поступают на соответствующие входы аналого-цифрового преобразователя 1 анализатора знака и разности 2, сумматора 3 и логический переклю чатель 7. Устройство может быть реализовано в лю бой цифровой системе передачи данных. Применение устройства позволит расширить диапазон передаваемых параме-гров и повыси эффективность системы передача информации Формула изобретения Устройство для передачи сигналов прирашениЙ содержащее аналого-цифровой преоб- разователь, вход которого подключен к вход устройства, анализатор знака и разности, первый, второй в третий входы которого соединены соответственно с выходами авалого цифрового преобразователя, сумматора и первым выходом матричногокоммутатора, второй и третий выходы 1йатричного коммутатора подключены к соответствующим входам сумматора; первый вхрд генератора синхроимпульсов соединен с синхронизирующими входами матричного коммутатора и формирователя сигналов, а второй выход - с синхронизирующими входами аналого-гафрового преобразователя, логического переключателя, анализатора знака и разности, первые выхода которого соединены с соответствующими входами логического переключателя, выход формирователя сигналов подключен к выходу устройства, отличаю шеес я тем, что, с целью повыщеиия точностн и быстродействия устройства в него введен блок кодирования, первь1й и второй выходь; которого подключены к соответстЕуюишм входам формирователя сигналов, Bxofu, coenviHeHbi с первым. Вторым и третьим, четвертым выходами логического переключателя, четвертый и пятый входы которого подключены к соответствующим выходам а 1ал 1затора знака и разности, выходы логического переключателя соединены со входами матричного коммутатора, 2. Устройство для передачи сигналов приращений по п. 1отл и чающееся тем, что, логический переключатель содержит элементы Vt и ИЛИ, триггеры и элемент задержки, выход которого соединен с R - входом первого триггера, прямой выход первого и инверсный вход второго триггеров подключены ко входам элемента И, выходы элементов ИЛИ подключены соответстпенно к входам третьего и четвертого триггера, вход -aneNieHTa задержки п R - вход третьего триггера соединены с первым входом логического переключателя/ S вход второго триггера подключен к второму входу логического переключателя, S -вход четвертого триггера и первый вход первого элемента ИЛИ соединен с третьим входом логического перехшючателя, второй вход первого и первый вход второго элементов ИЛИ поцключен к четвертому входу логического переключателя, второй вход Второго элемента ИЛИ н 5 -вход третьего триггера подключен к пятому входу логического переключателя, S -вход первого триггера соединен с синхронизирующим входом логического переключателя, инверсный выход первого триггера, выход элемента И прямой выход которого и выход третьего и четвертого триггеров подключены соответственно к первому, второму, пятому, третьему и четвертому входам матричного KOMMjTaTOpa. 3, Устройство для передачи сигналов приращений по п. 1 отличающеес я тем. Что блок копирования содержит

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи сигналов приращений | 1981 |

|

SU955163A1 |

| Устройство для передачи сигналов приращений | 1981 |

|

SU955162A1 |

| Устройство для передачи информации | 1975 |

|

SU547812A1 |

| Устройство для передачи сигналов приращений с предсказанием | 1978 |

|

SU765857A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для передачи сигналов приращений с предсказанием | 1977 |

|

SU705496A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Устройство для выделения признаков изображений | 1989 |

|

SU1661808A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

Авторы

Даты

1978-04-05—Публикация

1976-01-07—Подача