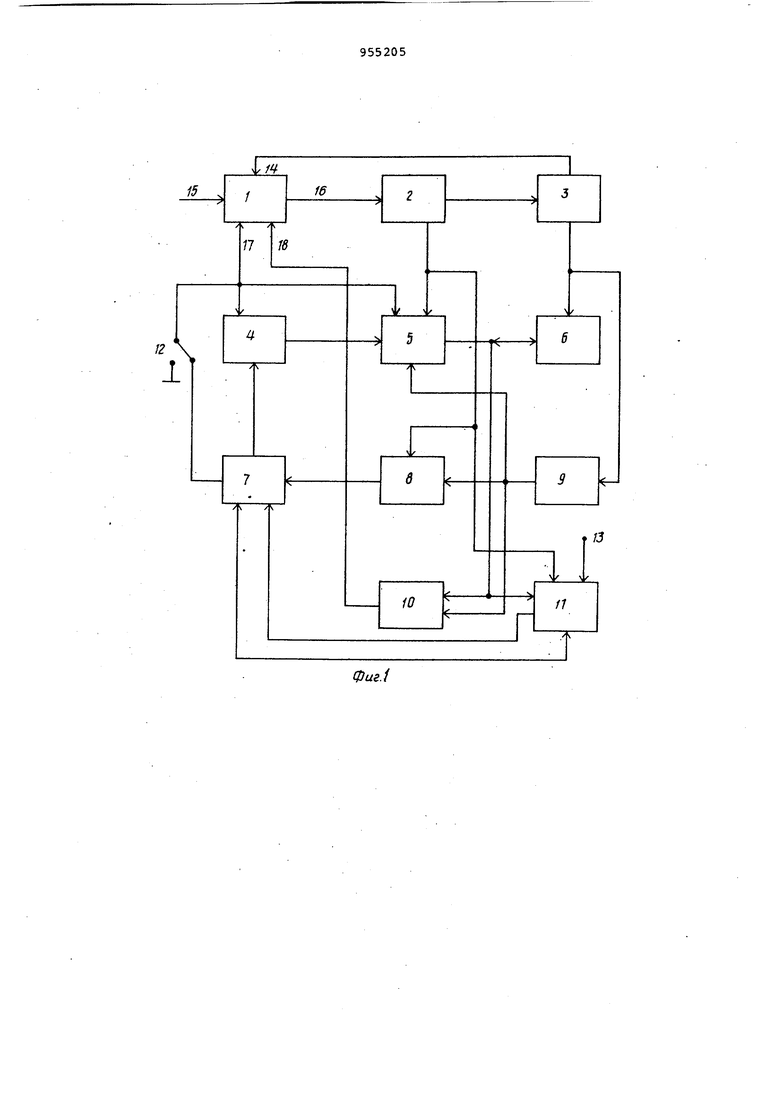

Изобретение относится к запоминающим устройствам и может быгь использовано для автоматического занесения информации в полупроводниковое запоминающее устройство путем пережигания плавких перемычек и контроля занесенной информации. Известно устройство для электричес кого программирования блоков постоянной памяти, содержащее схемы выбора соответствующего адреса слова (линии слова) и соответствующего бита информации (адреса перемычки) и генератор тока, выход которого подсоединяется к выбранной перемычке 1. Недостатками этого устройства являются низкие быстродействие и надежность. Из известных устройств наиболее близким техническим решением к предлагаемому является устройство для электрического программирования блоко постоянной памяти, содержащее операти ное запоминающее устройство (ОЗУ) емкостью 4096 12-разрядных слов, для хранения управляющей .программы и таблицы истинности, в соответствии с которой производится занесение информации,, соответствующее (эквивалент) эталонному блоку ПЗУ, блок автоматического задания адресов, схему сравнения, схему формирования командных сигналов для пережигания, блок пуСкаостанова и синхронизации, измеритель статических параметров, содержащий программируемые источники напряжения и тока и испытательный пульт для подключения программируемой схемы к разрядным ключам и к адресным цепям, блоки ввода-вывода и сопряжения .2. Недостатками этого устройства являются его сложность и невозможность автоматического задания длительности воздействия пережигающего импульса в зависимости от необходимого времени пережигания перемычки, что снижает его быстродействие и надежность. Цель изобретения - повышение надежности и быстродействия устройства. Поставленная цель достигается тем, что в устройство для электрического программирования блоков постоянной памяти, содержащее блок выбора разрядов, регистр адреса, формирователь импульсов, формирователь управляющих импульсов, разрядные ключи, блок задания эталонов, первую схему сравнения и блок местного управления, выход которого подключен к счетному блока выбора разрядов, первый рчход которого соединен со счетным входом региотра адреса, одни из выходов ко торого подключены к входам блока зад ния эталонов, первый управляющий вх блока местного управления подключен к управляющим входам формирователя и дульсов тока и разрядных ключей, од . из входов которого соединены соотве ственно с вторым выходом блока выбор разрядов с выходами блока задания эталонов и одними из вхолов первой схемы сравнения и с выходом формирователя импульсов тока, вход которого подключен к первому выходу формирователя управляющих импульсов, одни из выходов регистра адреса и другие входы и выходы разрядных ключей являются соответственно адресными выхо дами, разрядными входами и выходами устройства, введены датчик длительности импульсов тока, элемент И-ИЛИ и ключ, первый :выход которого подклю чен к шине нулевогопотенциала,- вход к второму выходу формирователя управ ляющих импульсов, а второй выход к управляющему входу формирователя импульсов, один из входов элемента И-ИЛИ соединен с выходом блока выбора разрядов и одним из датчика длительности импульсов тока, другие входы которого подключены к другим входам первой схемы сравнения и другим выходам разрядных ключей, другие входы элемента И-ИЛИ соединены с выходами блока задания эталонов а выход подключен к первому входу формирователя управляющих импульсов второй вход и третий -выход которого соединены соответственно с выходом и с первым управляющим входом датчика длительности импульсов тока, второй управляющий вход которого является входом опорного напряжения устройства, выход первой схемы сравнени подключен к.второму управляющему входу блока местного управления, установочный вход которого соединен с другим выходом регистра адреса. Блокместного управления содержит Триггеры, элемент ИЛИ-НЕ, элементы И, элементы НЕ и элемент задержки, причем выход элемента ИЛИ-НЕ подключен к входу первого элемента НЕ, выход которого соединен с первым входом первого элемента И и входами сбро са первого и второго-триггеров, второй вход первого элемента И подключей к выходу второго элемента НЕ и входу блокировки второго триггера, Которого соединен с входом блокировки Третьего триггера, вход сброса КОТОРОГО подключен к выходу первого элемента И, а счетный вход к счетному входу второГо триггера и выходу третьего элемента НЕ, вход которого соединен с первым входом второго элемента. И, второй вход и выход которого подключены соответ- i СТВ8НН-О к выходу первого триггера и первому входу первого элемента И-НЕ, второй вход i oToporo соединен с выходом третьего триггера, а выход - с входом элемента задержки, счетным входом четвертого триггера и входом четвертого элемента НЕ, выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с выходом четвертого триггера, первый вход третьего элемента И-НЕ подключен к выходу элемента задержки, а выход - к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с входом сброса четвертого триггера и является входом сброса блока, входом Пуск которого является установочный вход первого триггера, третий и четвертый входы элемента ИЛИ-НЕ и вход второго элементс1 НЕ являются соответственно установочным и управляющими входами блока, второй вход третьего элемента И-НЕ, вход третьего элемента НЕ и выход второго элемента И-НЕ являются соответственно входом разрешения останова, тактовым входом и выходом блока. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы наиболее предпочтительных вариантов выполнения блока местного управления и датчика длительности импульсов тока соответственно. Устройство содержит (фиг. 1) блок 1 местного управления, блок ,2 выбора разрядов, регистр 3 адреса, формирователь 4 импульсов тока, разрядные ключи 5, блок б постоянной памяти, в который заносится информация, формирователь 7 управляющих импульсов, элемент И-ИЛИ 8, блок 9 задания эталонов, первую схему 10 сравнения, датчик 11 длительности импульсов тока и ключ 12. На фиг. 1 обозначены вход 13 опорного напряжения устройства, установочный вход 14, вход 15 тактовых импульсов, выход 16, первый 17 и второй 18 управляющие входы блока Местного управления. При этом блок местного управления содержит (фиг. 2) элемент ИЛИ-НЕ 19, первый 20, второй 21, тргтий 22 и четвертый 23 элементы НЕ, первый 24, второй 25 и третий 26 элементы И-НЕ, первый триггер 27, первый ,28 и второй 29 элементы И элемент 30 задержки с выходом 31, второй 32, третий 33 и четвертый 34 триггеры. На фиг, 2 обозначены входы Пуск 35, сброса 36 и разрешения останова 37 блока. Датчик длительности импульсов тока предназначен для контроля времени, в течение которого происходит полное пережигание плавких перемычек, и содержит (фиг. 3) делитель 38 напряжения, вторую схему 39 сравнения, первую 40 и вторую 41 группы элементов И по числу контролируемых разрядов блока постоянной памяти и элемент ИЛИ 42, На фиг. 3 обозначен третий вход 43 датчика, предназначенный для сигнала стробирования.

Устройство работает в двух режима занесения информации и контроля.

Режим занесения информации. По команде Пуск блок 1 (фиг. 1) вырабатывает .командный сигнал, синхронный с тактовой частотой, поступающей на вход 15 (фиг. 1. и фиг. 2). Первый командный сигнал не проходит на вход блока. 2 (фиг. 1), что соответствует сохранению исходного состояния. Код из блока 2 дешифруется и поступает на входы ключей 5 элемента И-ИЛИ 8 и датчика 11. Наличие сигнала на первом выходе блока 2 соответствует выбору соответствующего разряда блока б памяти. На входы элемента И-ИЛИ 8 поступают сигналы с выходов блока 9. Совпадение сигналов в элементе И-ИЛИ 8 поступающих с выходов блока 2 и блока 9, соответствует наличию информации и указанию на пережигание перемычки в блоке б памяти. По команде на выходе 31 блока 1 (фиг. 2), поступакяцей на один из входов элемента И-ИЛИ 8 (фиг. 1) , на его выходе появляется сигнал, запускающий формирователь 7, который формирует сигнал для запуска формирователя 4 и управляющий сигнал, который через ключ 12 поступает на вход 17 блока 1 и управляющие входы формирователя 4 и ключей 5. Сигнал на входе 17 (фиг. 1) запрещает выработку командных сигналов на время пережигания перемычки. Сигналы на управляющих входах ключей 5 и формирователя 4 разрешают прохождение импульса тока на вход блока б памяти. Коды с выходов блока 2 и блока 9 поступают на ключи 5 и управляют выбором необходимого разряда блока 6. Одновременно с посылкой импульса тока через ключи 5 на вход блока производится .контроль напряжения пережигания, которое увеличивается по мере пережигания перемычки. При разрыве перемычки напряжение пережигания достигает максимальной величины.

Датчик ll производит контроль этого напряжения и при достижении напр5тасения опорного уровня, задаваемого по входу 13, и наличии стробирующего импульса на входе 43 (фиг. 3) выдает сигнгш, который запускает формирователь 4 (фиг. 1), сигнал которого ограничивает по времени командным сигналом с первого выхода формирователя 7, длительность которого определяется длительностью времени пережигания перемычки. На втором выходе формирователя 7 управляющий сигнал присутствует в течение времени, необходимого для пережигания перемычки и охлаждения схемы. На этом цикл пережигания перемычки оканчивается. Снимается запрещающий потенциал с первого управляющего входа 17 блока 1 и осуществляется привязка к тактовой частоте. Добавляется единица в блоке

2 (фиг. 1), что соответствует выбору рторого разряда нулевого адреса. Если

во втором разряде блока 9 (фиг. 1) записана единичная информация, то пережигание перемычки производится

аналогичным образом.

Если записана нулевая информация в блоке 9 по данному разряду, то отсутствует надобность в пережигании и элемент И-ИЛИ 8 (фиг. 1) не вырабатывает запускающий импульс на своем выходе, и не запрещается работа блока 1, который выдает импульс в блок 2, что соответствует выбору следующего адреса разряда, и работа продолжается.

В Тех разрядах, где отсутствует информация для записи перебор разрядов происходит с тактовой частотой (тактовая частота может соответствовать 1 МГц для элементной базы, например,

серии КМ155, а в тех разрядах где находится информация, производится пережигание с учетом необходимого ми-. нимального времени, которое зависит от технологии изготовления (размеров

перемычки) и, как правило, имеет 50% разброс.

После перебора; всех разрядов и , адресов с выхода регистра 3 на вход 14 (фиг, 1 выдается сигнал, который останавливает работу устройства.

В режиме контроля выхода ключ 12 подключается к шине нулевого потенциала. Сигнал по управляющему входу 17 разрешает опрос с тактовой частотой и блокирует работу формирователя

4 и ключей 5. Считанные коды туех разрядов блока ,6 и блока 14 сравниваются на схеме 10 и йри отсутствии ошибки разрешается изменение адреса. При наличии ошибки осуществляется

останов , результат несовпадения индицируется (цепи индикации не показаны). После повторного пуска осуществляется продолжение контроля. По окончании контроля по всем адресам осуществляется автоматический останов.

Технико-экономические преимьтцества предлагаемого устройства по сравнению с прототипом заключаются в том, что оно обеспечивает контроль за временем пережигания перемычек в блоках ПОСТОЯННОЙ памяти при существенном сокращении оборудования, что повышает его надежность и быстродействие.

Формула изобретения

1. Устройство для электрического программирования блоков постоянной памяти, содержащее блок выбора разрядов, регистр ещреса, формирователь импульсов тока, формирователь управляющих импульсов, разрядные ключи, блок задания эталонов, схему сравнения и блок местного управления, выход которого подключен к счетному входу блока выбора разрядов, первый выход, которого соединен со счетным входом регистра адреса, один из выходов которого подключен к входам блока задания эталонов, первый управляющий вход блока местного управления подключен куправляющим входам формирователя импульсов тока и разрядных ключей, одни из входов которого соединены соответственно с вторым выходом блока Еыбора разрядов, с выходами блока задания эталонов и одними из входов схемы сравнения и с выходом формирователя импульсов тока, вход которого подключен к первому выходу формирователя управляющих импульсов, одни из выходов регистра адреса и другие входы и выходы разрядных ключей являются соответственно адресными выходами, разрядными входами и выходами устройства, отличающееся тем, что.: с целью позышения надежности и быстродействия устройства, оно содержит датчик длительности импульсов тока, элемент И-ИЛИ и ключ, первый выход которого подключен к шине нулевого потенциала, вход - к второму выходу формирователя управляющих импульсов, а второй выход - к управляющему входу формирователя импульсов тока, один из входов элемента И-ИЛИ соединен с выходом блока выбора разрядов и одним из входов датчика длительности импульсов тока, другие входы которого подключены к другим входам схемы сравнения и другим выходам разрядных ключей, другие входы элемента И-ИЛИ соединены с выходами блока задания эталонов, а выход подключен к первому входу формирователя управляющих импульсов, второй вход и третий выход которого соединены соответственно с выходом и первым управляющим входом датчика длительности импульсов тока, второй управляющий вход которого является входом опорного напряжения устройства, выход схемы сравнения подключен к второму управляющему входу блока местного управления, установочный вход которого соединен с другим выходом регистра адреса.

2. Устройство по п. 1, отличающееся тем, что блок местного управления содержит триггеры, элемент ИЛИ-НЕ, элементы И, элементы НЕ и элемент задержки, причем выход элемента ИЛИ-НЕ подключен к входу пеового элемента НЕ, выход которого соединен с первым входом первого элемента И и входами сброса первого и второго триггеров, второй вход первого элемента И подключен к выходу второго элемента КЕ и входу блокировки второго триггера, выход которого соединен с входом блокировки третьего триггера, вход сброса которого подключен к выходу первого элемента И, а счетный вход - к счетному входу второго триггера и выходу третьего элемента НЕ, вход которого соединен с первым входом второго элемента И, второй вход и выход которого подключены соответственно к выходу первого триггера и первому входу первого элемента И-НЕ, второй вход которого соединен с выходом третьего триггера, а выход - с входом элемента задержки, счетным входом четвертого триггера и входом четвертого элемент НЕ, выход которого подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с выходом четвертого триггера, первый вход третьего элемента И-НЕ подключен к выходу элемента задержки, а выход к первому входу элемента ИЛИ-НЕ, второй вход которого соединен с входом сброса четвертого триггера и являетс входом сброса блока, входом Пуск которого является установочный вход первого триггера, третий и четвертый входы элемента ИЛИ-НЕ и вход второго элемента НЕ являются соответственно установочным и управляющими входами блока, второй вход третьего элемента И-НЕ, ВХОД третьего элемента НЕ и вьжод второго элемента И-НЕ являются соответственно входом разрешения останова, тактовым входом и выходом блока

Источники информации, принятые во внимание при экспертизе

1.Соучек Б. Микро-ЭВМ. М., Сов. радио, 1979, с. 59, 60.

2.Лябин В. И. и др. Программирование и контроль ПЗУ. - Электронная промышленность, 1976, № 4-, с. 64-67 (ПРОТОТИП).

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в электрически программируемый накопитель | 1983 |

|

SU1170508A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 2000 |

|

RU2182359C2 |

| Система для контроля электронных устройств | 1988 |

|

SU1667074A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Программатор для записи информации в полупроводниковые элементы памяти | 1985 |

|

SU1280449A2 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

Авторы

Даты

1982-08-30—Публикация

1981-01-05—Подача