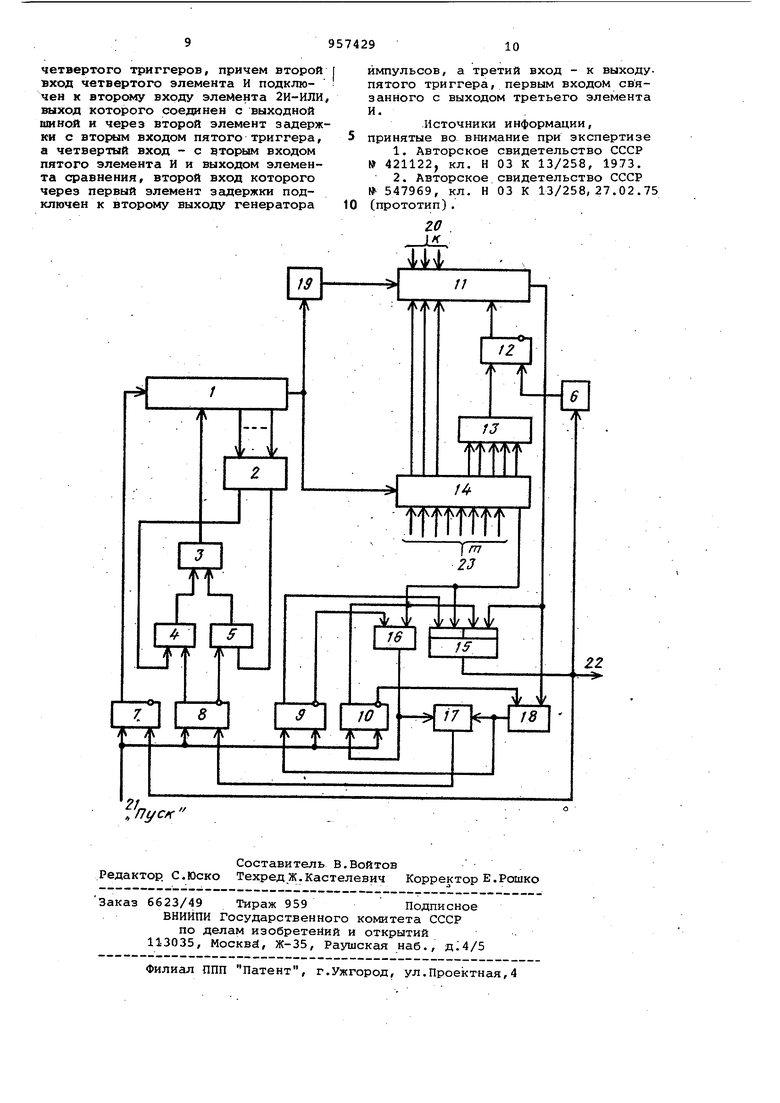

случае, если число, определяемое кодом младших разрядов, больше числа, определяемого кодом старших разрядов. Цель изобретения - расширение ди апазона преобразования временных ин тервалов. Поставленная цель достигается тем что в преобразователь кода во временной интервал, содержащий генератор импульсов, первые выходы которо го соответственно соединены с входа -ми .переключателя диапазонов, выхода ми соответственно связанного с первыми входами первого и второго элементов И, выходы которых через эле-; мент ИЛИ подключены к второму входу генератора импульсов, вторым выходом соединенного со счетным входом счетчика импульсов, установочные входы которого подключены к шине старших разрядов кода, выходы старших разрядов - к входам третьего элемента И, выходы младших - к первым входам эле мента сравнения, вторыми входами соединенного с шиной младших разрядов кода, а выход - к второму входу четвертого элемента И, два триггера, первые входы которых подклк чены к ши не Пуск, второй вход первого триггера - к выходной щине, его выход к первому входу генератора импульсов, а выходы второго - к вторым вхо дам парного и второго элементов И со ответственно, дополнительно введены элемент 2И-ИЛИ, три триггера, элемент ИЛИ, два элемента задержки и пятый элемент И, пpичe 4 первый и тре тий входы элемента 2И-ЙЛИ соответственно соединены с первыми выходами третьего и четвертого триггеров, вто рые выходы которых подключены к первым входам четвертого и пятого элементов И, выходами связанных с первыми входами четвертого и третьего триггеров и первым и вторым входами второго элемента ИЛИ, выход которого соединен с вторым входом второго триггера, первый вход которого соединен с вторыми входами третьего и четвертого триггеров, причем второй вход четвертого элемента И подключен к второму входу, элемента 2И-ИЛИ, выход которого соединен с выходной шиной и через второй элемент задержки с вторым входом пятого триггера, а четвертый вход - с вторым входом пятого элемента И и выходом элемента сравнения, второй вход которого через первый элемент задержки подклю чен к торому выходу генератора импульсов, а третий вход - к выходу пятого триггера, первым входом связанного с выходом третьего элемента И. На чертеже изображена блок-схема преобразователя кода во временной интервал. Преобразователь содержит генера- , тор 1 импульсов, переключатель 2 диапазонов преобразования, элемент ИЛИ 3, элемент И 4 и 5, элемент б задержки, триггеры 7-10, элемент 11 сравнения, ,триггер 12, элемент И 13, счетчик 14 импульсов, элемент 2И-ИЛИ 15, элемент И 16, элемент ИЛИ 17, элемент И 18, элемент 19 задержки, шигал 20-23, При этом отводы линии задержки генератора 1 импульсов подключены к соответствующим входам переключателя 2диапазоновf выходом соединенного с входами элементов И 4 и 5. Выходы элементов И 4 и 5 через элемент ИЛИ 3подключены ко второму входу генератора 1, первый вход которого связан с прямым выходом триггера 7, а выход через элемент 19 задержки - с лервым входом элемента 11 сравнения, и непосредственно со счетным входом счетчика 14 импульсов. На вторые входы счетчика импульсов по шине 23 поступает обратный код старших разрядов, а элемента сравнения (по шине 20) - -прямой код младших разрядов. Выходы старших разрядов счетчика 14 импульсов подключены через элемент И 13 к первому входу триггера 12, а младших разрядов ко второму входу элемента 11 сравнения. Прямой выход триггера 12 соединен с третьим входом элемента 11 сравнения, выходом связанного с четвертым входом элемента 2И-ИЛИ 15 и вторым входом элемента И 18. Выход счетчика 14 импульсов связан со вторыми входами элемента 2И-ИЛИ 15 и элемента И 16. Выходы элементов И 16 и 18 подключены к первым входам триггеров 9 и 10 и через элемент ИЛИ 17 к второму входу триггера 8. Прямой и обратный выходы триггера 8 соединены с вторыми входами элементов И 4 и 5 соответственно. Прямые выходы триггеров 9 и 10 соединены с первым и третьим входами элемента- 2И-ИЛИ 15, а обратные выходы - с первыми входами элементов И 16 и 18, Выход элемента 2И-ИЛИ 15 соединен с вторыми входами триггера 7 непосредственно и триггера, 12 через элемент 6 задержки. На первые входы триггеров 7 и.8 и вторые входы триггеров о9 и 10 по входной шине 21 поступает импульс запуска. Частота генератора, используемого в преобразователе, определяется запаздывающей обратной связью. Изменяя параметры Линии задержки генератора 1, при помощи переключателя 2 можно задавать частоту преобразования в соответствии с выбранным диапазоном преобразования. Устройство работает следующим образом.

Перед началом работы преобразова- i теля обратный код старших разрядов I m по шине 23 переписывается в счетчик импульсов, прямой код младших разрядов k по шине 20 подается на входы элемента 11 сравнения. Триггер 12 находится в нулевом состоянии.

Начало преобразования определяется импульсом запуска, поступающим по шине 21. Импульсом запуска устанавливаются в единичное состояние триггеры 7 и 8 и в нулевое состояние триггеры 9 и 10. Уровень напряжения с триггера 7 подается на генератор 1. Появление первого импульса генератора 1 жестко связ.ано с передним фронтом уровня напряжения.

Импульсы с выхода генератора 1 поступают на счетный вход счетчика 14 импульсов и через элемент 19 задержки на элемент 11 сравнения. Частота-выходных импульсов генератора 1 определяется коммутируемым переключателем диапазонов. Импульсы с i-ro отвода линии задержки генератора 1 через переключатель 2 поступают на вход элемента И 4, на второй вход которого подан высокий уровень триггера 8. Импульсы с выхода элемента 4 через элемент ИЛИ 3 поступают на вход генератора 1 в качестве запаздывающей обратной связи.

Схему преобразователя в зависимости от преобразуемого кода рассмотрим для двух случаев: число, определяемое кодом старших разрядов больше числа, определяемого кодом младших разрядов (); число, определяемое кодом старших разрядов меньше числа, определяемого кодом младших разрядов (т k),

В первом случае на первый выход переключателя 2 диапазона коммутируется отвод линии задержки, задающий частоту с периодом Т-; на второй выход-отвод линии задержки, задающий частоту с периодом Т -At, где t величина минимального дискретного шага преобразования.

На счетный вход счетчика 14 поступают импульсы с периодом Т. Когда в счетчике 14 устанавливается число, равное числу кода младших разрядов, записанного в элементе 11 срав нения, а в остальных разрядах счетчика устанавливаются единицы, что фиксируется триггером 12, то элемент 11 сравнения выдает импульс, поступающий на четвертый вход элемента 2ИИЛИ 15 и второй вход элемента И 18. Так как на первый выход элемента И 18 подаетсй высокий уровень, соответртвующий нулевому состоянию триггера 10, то выходной импульс элемента 11 сравнения через элемент И 18 производит переключение в единичное состояние триггера 9. Одновременно .через элемент ИЛИ 17 производится установка триггера 8 в нулевое состояние. При этом низким уровнем триггера 8 запрещается генерирование импульсов генератора с периодом Т; и вывысоким уровнем - разрешение цепи обратной связи, определяющей генерирование импульсов с периодом Т;-it . Это достигается переключением работы .элементов И 4 и 5. Импульсы с элемента И 5 поступают на вход элемен-.

0 та ИЛИ 3.

В счетчике импульсов 14 продолжается счет импульсов, поступающих с периодом Ti-ut. После заполнения, счетчика 14 формируется импульс переполнения, поступающий на второй

5 вход элемента 2И-ИЛИ 15, на первый вход которого подан высокий уровень единичного состояния триггера 9. Выходной импульс элемента 2И-ИЛИ 15 определяет конец временного интерва0ла. По этому импульсу производится также установка в О триггера 7, непосредственно, а триггера 12 через элемент 6 задержки, время задержки которого должно быть не меньше дли5тельности импульса.

Временной интервал для первого случая, соответствующий заданному коду, равен

;: т-Т. -Cn-1-k) .+ (n-t-k) ()

0

(1)

где Т- - период основной частоты сле дования импульсов; т - число, определяемое кодом

5

старших разрядов (т. О, 1,

2...); - .

k - число, определяемое кодом мпадших разрядов (k 0,i, 2..., n-l);

0 At - минимальный дискретный шаг

преобразования.

Если число, определяемое кодом старших разрядов, меньше числа, определяемого кодом младших разрядов, то переключателем 2 коммутируется отвод

5 линии задержки, задающей период Т:;, на второй - отвод лкнии задержки, за1дающий период, равный минимальному |дискретному шагу преобразования At. Импульсы генератора 1 с периодом

0 Т i поступают на счетчик 14 импульсов ина элемент 11 сравнения через элемент 19 задержки, время задержки которого должно быть не меньше времени переключения счетчика импульсов.

5

Наличие всех единиц в старших разрядах счетчика 14 фиксируется триггером 12.

Импульсом переполнения счетчика

0 14 импульсов производится переключение в единичное состояние через элемент И 16 триггера 10, и в нулевое состояние через элемент ИЛИ 17 триггера 8. Высокий уровень с прямого

5 выхода триггера 10 подается на третнй вход элемента 2И-ИЛИ 15 в качестве разрешающего напряжения.

. Переключение триггера 8 обеспечивает коммутацию цепи обратной связи (в данном случае равную минимальному дискретному шагу преобразования д1) генератора 1 путем переключения разрешающих уровней напряжения на элементах И 4 и 5. Импульсы-генератора с периодом At поступают на счетный вход счетчика 14. Если число, определяемое кодом младших разрядов, поданным на элемент 11 сравнения, равно числу, определяемому кодом младших разрядов счетчика 14, и на выходе триггера 12 имеется высокий уровень, то элемент 11 сравнения выдает сигнал сравнения. Этот сигнал поступает на четвертый вход элемента 2И-ИЛИ, выходной сигнал которого и являетсяконцом временного преобразования. По этому сигналу устанавливается в О триггер 7 и через элемент задержки б триггер.12.

Временной интервал в данном случае равен.

(2)

1 k-At ,

где m - число, определяемое кодом

старших разрядов; k - число, определяемое кодом

младших разрядов; Т - период основной частоты

преобразования; . At. - минимальный дискретный

шаг преобразования. Предлагаемое устройство выгодно отличается от известного тем, что в нем производится преобразование во временной интервал любого кода без каких-либо ограничений как в области малых разрядов, так и в области больших. В зависимости от преобразуемого кода задаются различные параметры линии задержки генератора. Если , то разница между периодами основной и дополнительной частот должна быть равна минимальному дискретному шагу преобразования At, если же m k , то период основной частоты генератора Т,- выбирается в зависимости от числа, заданного кодом старших разрядов, дополнительной - it.

Введение трех дополнительных триггеров, элемента И, элемента 2И-ИЛИ, элемента ИЛИ, двух элементов задержки и соответствующих связей позволил расширить диапазон преобразования временн&х интервалов в область малых величии преобразуемого кода.

Если , то преобразование осуществляется в соответствии с формулой (1), если , то заданный код преобразуестя во временной интервал в соответствии с формулой (2).

Для m k выбор необходимой формулы, реализуемой схемой, также производится автоматически. Необходимо лишь правильно задать основную и дополнительную частоты преобразования.

Для примера можно рассмотреть десятиразрядный код 0000001010, в котором число, определяемое кодом младших разрядов, равно k 2 (код

0 О1о), число, определяемое кодом старших разрядов равно m 1 (код 0000001}, причем в известном устройстве особенности схемы не допускают преобразование кода 0000001010 во временной инj тервал, так как обратный код старших разрядов, записанный в сче.тчик, будет больше кода младших разрядов,поданного на элемент сравнения.

Формула изобретения

Преобразователь кода во временной интервал, содержащий генератор импульсов, первые выходы которого соответственно соединены с входами переключателя диапазонов,-выходами соответственно связанного с первыми входами первого и второго элементов И, выходы которых через элемент ИЛИ

0 подключены к второму входу генератора импульсов, вторым выходом соединенного со счетным входом счетчика -импульсов, установочные входы которого подключены к шине старших

5 разрядов кода, .выходы старших разрядов - к входам третьего элемента И, выходы младших - к первым входам элемента сравнения, вторыми входами соединенного с шиной младших разрядов кода, а выход - к второму входу четвертого элемента И, два триггера, первые входа которых подключены к шине Пуск, второй вход первого триггера - к выходной шине, его вы5 2СОД - к первому входу генератора импульсов, а выходы второго - к входам первого и второго элементов И соответственно, отличающийся тем, что, с целью расширения диапазона преобразования, в него введены элементы 2И-ИЛИ, три триггера, эле-( мент ИЛИ, два элемента задержки и пятый элемент И, причем первый и третий входы элемента 2И-НЛИ соответственно соединены с первыми выходами

третьего и четвертого триггеров.

вторые выходы которых, соответственно подключены к первым входам четвертого и пятого элементов И, выходами соответственно связанных с первыми

входами четвертого и третьего триггеров и первым и вторым входами второго элемента ИЛИ, выход которого соединен с вторым входом второго триггера, первый вход которого соединен с вторыми входами третьего и

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода во временной интервал | 1975 |

|

SU547969A1 |

| Преобразователь кода во временной интервал | 1981 |

|

SU995320A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1654976A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1990 |

|

SU1725396A1 |

| Цифровой фазометр | 1986 |

|

SU1348744A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

Авторы

Даты

1982-09-07—Публикация

1981-02-25—Подача